1功能说明

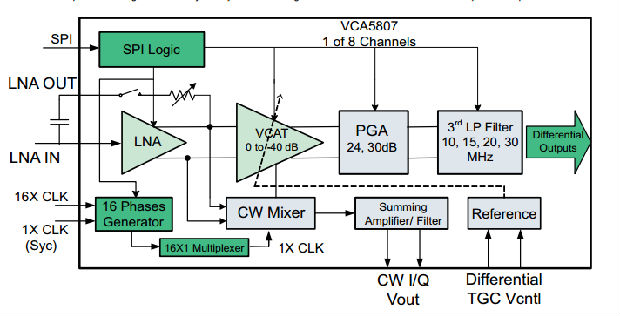

VCA5807是集成电压控制8通道电压控制放大器专门为超声波设计的放大器(VCA)–高性能、小尺寸的LNA、VCAT、PGA、LPF和CW混音系统需要可编程低噪声放大器(LNA)。VCA5807集成了一个完整的–24/18/12 dB增益时间增益控制(TGC)成像路径和连续波多普勒(CWD)路径。它还可以–0.25/0.5/1 vpp线性输入范围用户可选择各种功率/噪声中的一种–0.63/0.7/0.9 nv/rthz输入参考噪声组合以优化系统性能。–可编程主动端接因此VCA5807是一种合适的超声波模拟前端解决方案不仅适用于高端40分贝低噪声电压控制系统,也适用于便携式系统。衰减器(VCAT)VCA5807包含八个电压通道24/30 dB可编程增益放大器(PGA)控制放大器(VCA)和连续波混频器。VCA三阶线性相位低通滤波器(LPF)包括低噪声放大器(LNA),电压控制–10、15、20、30兆赫衰减器(VCAT),可编程增益放大器–巴特沃斯特性(PGA)和低通滤波器(LPF)。LNA增益是可编程以支持250 mvpp到1 vpp输入噪声/功率优化(全链)信号。可编程主动端接也是-0.75 nv/rthz下99 mw/ch,由LNA支持。超低噪声VCAT–56 mw/ch,1.1 nv/rthz时,衰减控制范围为40db,并且提高整体低增益信噪比–连续波模式谐波成像和近场成像时为80 mW/chPGA卓越的设备间增益匹配提供24分贝和30分贝的增益选项。在5 dB(典型)和.05 dB(最大)ADC,一个LPF可以配置为10 MHz、15 MHz,20兆赫或30兆赫,支持不同频率的超声波 低谐波失真应用。另外,VCA5807的快速一致的过载恢复信号链可以处理信低频声纳信号处理频率低于100 kHz,使其能够不仅用于超声波应用,而且用于连续波多普勒的被动混频器。

声纳应用。(连续工作日)–低闭合相位噪声–1时为156 dBc/Hz。VCA5807集成了低功率无源混频器。kHz关闭2.5兆赫载波和一个低噪声和放大器,以完成onchipCWD波束形成器。16个可选相位延迟相位分辨率为1/16λ可应用于每个模拟输入信号。–支持32x、16x、8x、4x和1x CW时钟,同时支持独特的3RD和5次谐波–12分贝抑制打开3RD和5为了增强连续波,实现了谐波抑制滤波器。敏感。–灵活的输入时钟VCA5807有14mm x 14mm、100-14mm x 14mm、100针TQFP。pin tqfp包,指定用于操作从-40°C到85C。应用

医学超声成像

无损评价设备

声纳成像

这种集成电路会被静电放电损坏。Texas Instruments建议使用适当的预防措施。不遵守正确的操作和安装程序可能导致损坏。静电放电损伤的范围从细微的性能退化到整个设备故障。精密集成电路可能更很容易受到损坏,因为非常小的参数变化可能导致设备不符合其公布的规格。

串行外围接口(SPI)操作寄存器写入描述不同模式的编程可以通过pins sen(串行接口)形成的串行接口来完成。启用)、SCLK(串行接口时钟)、SData(串行接口数据)和重置。所有这些销都有下拉式接地电阻为20kΩ。当SEN低时,位到设备的串行移位被启用。串行数据SData是当SEN激活(低)时,在SCLK的每个上升沿锁定。串行数据加载到寄存器SEN低时每24 SCLK上升沿。如果字长度超过24位的倍数,则超出的位被忽略。数据可以在单个有源SEN脉冲内以多个24位字加载(有一个内部在sen下降沿后计算24个时钟组的计数器)。接口可以与SCLK一起工作频率从20兆赫下降到低速(几赫兹),甚至与非50%的占空比SCLK。数据是分为两个主要部分:寄存器地址(8位)和数据本身(16位),加载到地址上注册。当用未使用的位写入寄存器时,这些应设置为0

注意

重置必须保持为“1”大于100 ns。复位后,建议大于100 ns在写入SPI寄存器之前。

寄存器读出说明

该设备包括一个选项,其中内部寄存器的内容可以被读出。这可能有用作为验证外部控制器和VCA之间串行接口通信的诊断测试。首先,<register readout enable>位(reg0[1])需要设置为“1”。然后用户应该启动串行接口周期,指定必须读取其内容的寄存器(A7-A0)的地址。数据位是“不在乎”。设备将在sdout引脚上输出所选寄存器的内容(d15-d0)。这个从SCLK的下降沿开始,SDOUT的典型延迟T8为20 ns。对于低速SCLK,SDOUT可以锁定在SCLK的上升沿。对于高速SCLK,也就是说,SCLK周期小于60ns,它将最好在SCLK的下一个下降边缘锁定SDOUT。下面的时序图显示了此操作(时间规格遵循提供的相同信息。在读取模式下,用户仍然可以访问<register_readout_enable>through sdata/sclk/sen.要启用串行寄存器写入,请设置<register_readout_enable位返回

VCA寄存器映射在VCA5807初始化阶段需要重置过程。可以通过以下两种方式之一进行初始化:

1.通过硬件复位,在复位针中施加正脉冲

2.第二步。通过软件复位,使用串行接口,通过将软件复位位设置为高。设置该位将内部寄存器初始化为各自的默认值(全部为零),然后自复位软件将位重置为低。在这种情况下,复位销可以保持在低位(不活动)。重置后,所有VCA寄存器都设置为“0”,即默认设置。在寄存器编程期间,所有保留/未列出的寄存器位需要设置为“0”。当VCA5807处于部分断电模式或完全断电模式。

寄存器描述输入阻抗配置(主动终止编程性)不同的LNA输入阻抗可以通过注册52[4:0]。通过创建和摧毁反馈电阻器在LNA输出和ACTX PINS之间,LNA输入阻抗是可调节的。Table 2描述LNA增益与52[4:0]settings之间的关系。输入阻抗设置与输入阻抗设置相同。

TGC和CW路径。

另外,VCA5807还有4 preset active termination impedances as described in 52[7:6]。内部解码用于选择适当的电阻器对应于不同的LNA增益。

连续波求和放大器的可编程增益通过寄存器54[4:0],可以为连续波求和放大器配置不同的增益。通过启用和禁用求和放大器输入和输出之间的反馈电阻,增益可调。从而使连续波路径的动态范围最大化。求和之间的关系放大器增益和54[4:0]设置。

VCA5807概述VCA5807是专门为超声波设计的集成电压控制放大器(VCA)解决方案。

要求高性能和小尺寸的系统。VCA5807集成了一个完整的时间增益控制TGC)成像路径和连续波多普勒(CWD)路径。它还允许用户选择各种功率/噪声组合以优化系统性能。VCA5807包含八个通每个通道信道包括低噪声放大器(LNA)、电压控制衰减器(VCAT)、可编程增益放大器(PGA)、低通滤波器(LPF)和连续波混频器。此外,VCA5807中的多个功能适用于超声波应用,例如主动端接,单通道控制、快速上/下电响应、可编程钳位电压控制、快速和持续过载恢复,且打开。因此,VCA5807为超便携手持系统一直到高端超声系统。此外,VCA5807可以支持声纳应用,考虑到其出色的低频(<100 kHz)响应。其简化功能

功能框图

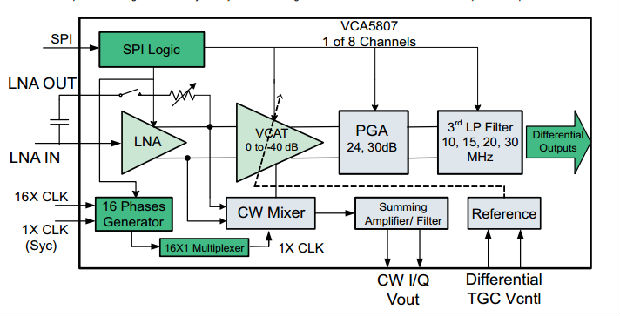

低噪声放大器(LNA)在许多高增益系统中,低噪声放大器是实现整体性能的关键。使用新的专有架构,VCA5807中的LNA在运行时提供了卓越的低噪音性能。与具有类似噪声性能的基于CMOS的结构相比,静态电流非常低。印度共和国执行单端输入到差分输出电压转换。它可配置为可编程增益24/18/12db,输入参考噪声分别为0.63/0.70/0.9nv/√hz。可编程增益设置使线性输入范围灵活,可达1vpp,实现了新产品对高信号处理能力的要求。传感器技术。较大的输入信号可被LNA接受,但信号可能会失真。因为它超过了LNA的线性操作区域。结合低噪声和高输入范围,宽输入从而实现动态范围,支持各种超声成像的高要求。

模式。

LNA输入内部偏压约为+2.4V;信号源应与LNA交流耦合。

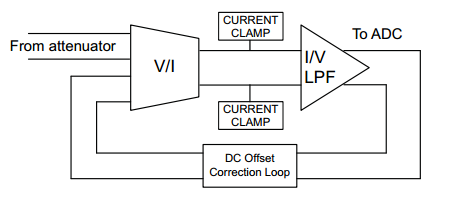

由适当尺寸的电容器输入,即,≥0.1微F。为实现低直流偏移漂移,VCA5807为每个放大器级集成了一个直流偏移校正电路。为了提高过载恢复率,积分器电路用于提取低噪声放大器输出的直流分量,然后反馈给低噪声放大器用于直流偏移校正的补充输入。该直流偏移校正电路具有高通响应,可以作为高通滤波器处理。有效角频率由连接的电容器cBypass确定。在inm.电容器越大,角频率越低。用于在最高HP文件管理器切断时稳定运行频率,可选择一个≥15nF的电容器。这个角频率几乎与C类。例如,15nf给出了大约100kHz的角频率,而47nf给出了有效角频率为33kHz。如果需要低频操作,直流偏移校正电路可以也可通过寄存器52[12]禁用/启用。可以使用1微F这样的大电容器来设置低角LNA直流偏移校正电路的频率(<2 kHz)

频率应用。

VCA5807可以被动或主动终止。在超声波应用中,主动端接是首选。减少不匹配的反射,在不降低噪声系数的情况下获得更好的轴向分辨率。很多。主动端接值可以预设为50、100、200、400Ω;其他值也可以通过以下方式编程:用户通过寄存器52[4:0]。在actx和信号源之间需要一个反馈电容器作为在主动端接路径上,还使用夹紧电路来创建低阻抗路径。

当VCA5807看到过载信号时。钳位电路限制了LNA输入端的大输入信号,并且提高了VCA5807的过载恢复性能。钳位可设为350mvpp,当寄存器52[10:9]=0时,600mVpp,1.15Vpp自动取决于LNA增益设置。其他夹钳电压,如1.15Vpp、0.6Vpp和1.5Vpp,也可通过设置寄存器52来实现[10:9]。这个夹持电路的设计还可以获得良好的脉冲反转性能,并减少不对称的影响。输入。请注意,在LN增益切换过程中,钳位设置可能会发生变化。因此夹具的固定时间在调整LNA增益时必须考虑,特别是当过载信号超过夹紧电压时。

带直流偏移校正电路的VCA5807低噪声放大器

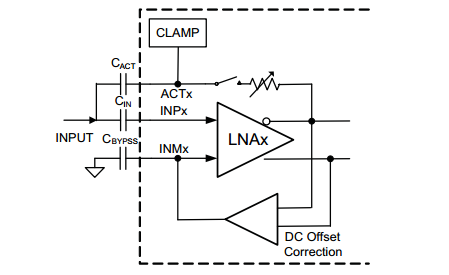

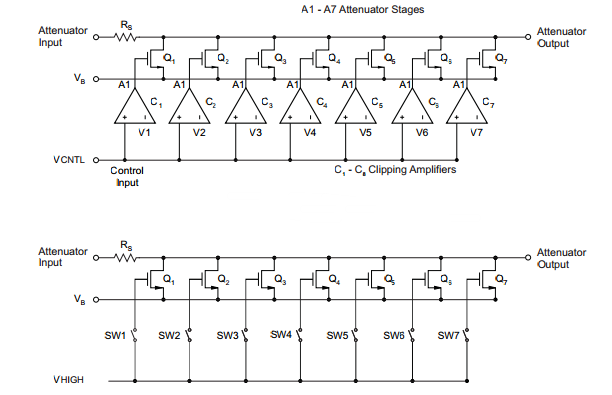

电压控制衰减器设计成具有线性In-dB衰减特性,即对于控制电压(VCNTL)的每一个相等增量,平均增益损失(单位:dB)是恒定的,如下所示:采用差分控制结构来降低共模噪声。一种简化的衰减器衰减器本质上是一个可变分压器,由串联输入电阻(RS)和七个并联FET,由连续激活的剪切放大器(A1到A7)控制。VCNTL公司是vcntlp和vcntlm之间的有效区别。每个剪辑放大器可以理解为专用电压比较器,具有软传输特性,输出极限电压控制良好。参考电压v1至v7在0V至1.5V控制电压范围内等距分布。作为控制电压通过每个削波放大器的输入范围增加,放大器输出从电压上升。

当FET接近关闭时,到了完全打开的位置。当每个场效应晶体管接近其开启状态时控制电压继续升高,下一个削波放大器/FET组合接管下一个。分段线性衰减特性的一部分。因此,低控制电压具有大多数场效应管。关闭,产生最小信号衰减。同样,高控制电压会打开场效应管,导致最大信号衰减。因此,每个场效应管都起到降低分压器分流电阻的作用。由RS和并行FET网络组成。此外,还实现了数字控制的TGC模式,以获得更好的相位噪声性能。VCA5807。衰减器可以由数字控制而不是模拟控制电压VCNTL。此模式可以由寄存器位59[7]设置。可变分压器作为固定串联电阻和场效应管实现。作为分流电阻。通过连接开关SW1-7,可以打开每个FET。打开每个开关可以提供大约6分贝的衰减。这可以由寄存器位59[6:4]控制。这个数字控制功能可以消除VCNTL电路中的噪声,保证更好的信噪比和相位噪声。对于TGC路径。

简化的电压控制衰减器(数字结构)

电压控制衰减器的噪声与衰减系数呈单调关系。在更高的衰减,输入参考噪声较高,反之亦然。然后,衰减器的噪声被PGA放大。成为ADC输入端的噪声地板。在衰减器的高衰减工作范围内,即VCNTL是高,衰减器的输入噪声可能超过LNA的输出噪声;然后衰减器成为主导以下PGA级和ADC的噪声源。因此,应尽量减少衰减器的噪声。

与LNA输出噪声相比。VCA5807的衰减器设计用于实现非常低的噪音,即使在高衰减(低通道增益),近场信噪比更好。请参阅PGA输出配置

可编程增益放大器(PGA)

在电压控制衰减器之后,可编程增益放大器可配置为24db或30db恒定输入参考噪声为1.75nv/rthz。PGA结构由差分电压-电流组成。具有可编程增益的转换器、电流箝位(偏压控制)电路、具有可编程低通滤波器,以及直流偏移校正电路。其简化框图如下:PGA简化框图

低输入噪声是PGA的首选,其噪声贡献不应降低ADC的信噪比。在衰减器之后。在最小衰减(用于小输入信号)时,lna噪声占主导地位;at最大衰减(大输入信号)、PGA和ADC噪声占主导地位。因此,PGA的24分贝增益只要放大后的信号可以超过ADC的噪声下限,就可以获得更好的信噪比。可启用PGA电流钳位电路(寄存器51),以提高VCA。如果我们在过载后测量输出的标准偏差,对于0.5伏VCNTL,大约是3.2。LSB在正常情况下,即输出在过载后约1个时钟周期内稳定。带电流钳电路禁用,该值接近4个LSB,意味着输出稳定之前的时间更长;但是,在启用电流钳位电路的情况下,对于PGA输出电平>,HD3将会降级。-2dbfs.例如,对于–2dbfs输出电平,hd3下降约3db。为了最大化输出动态范围,最大PGA输出电平可超过2VPP(0 dbfs线性输出范围),带钳位电路。因此,应选择具有良好过载恢复性能的ADC。

注意

在低功率和中功率模式下,如果VCA5807以可编程低通滤波器(LPF)的形式集成了一个消除混叠滤波器。互阻抗放大器。LPF被设计成具有巴特沃斯的差分、有源、三阶滤波器。特点和一个典型的18分贝每八度滚降。可通过串行接口进行编程,–1db频率角可以设置为10MHz、15MHz、20MHz和30MHz。过滤器带宽为所有同时播放频道。

此外,还实现了一种可选的直流偏移校正电路。此校正电路类似于一个在印度使用。它提取PGA输出的直流分量并反馈给PGA直流偏移校正的免费输入。这种直流偏移校正电路也有高通响应。截止频率为80kHz。如果需要<80kHz的操作,则可以禁用直流偏移校正电路。通过寄存器0x33[4]。

连续波波束形成器

连续波多普勒是中高端超声系统的关键功能。与TGC相比模式下,连续波路径需要处理高动态范围和严格的相位噪声性能。连续波由于上述的严格要求,波束形成通常在模拟域中实现。多个波束形成方法在超声系统中得到了应用,包括无源延迟线、有源混频器等。被动混音器。其中,被动混频器实现了功率和噪声的优化。它满足连续波处理要求,动态范围宽,相位噪声低,增益准确

相位匹配。

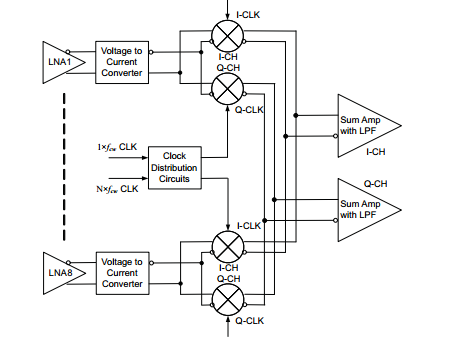

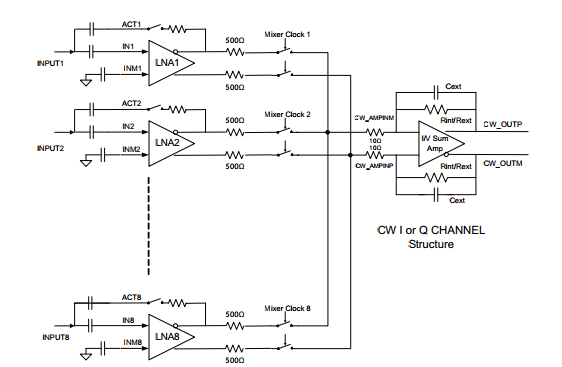

给出了一个简化的连续波路径方块图和一个同相或正交(I/Q)通道方块图。分别在下面。每个连续波通道包括一个低噪声放大器、一个电压-电流转换器、一个基于开关的混频器、一个带低通滤波器和时钟电路的共享求和放大器。所有模块均包含匹配良好的同相以及正交信道,以实现良好的图像频率抑制和波束形成精度。作为一个结果,I/Q通道的图像抑制率优于超声系统所需的-46dbc。

注:连续波安培数m/p下的10~15Ω电阻是由于内部IC布线造成的,可能会产生轻微的衰减。

完全同相或正交相位通道VCA5807中的连续波混频器是基于开关的被动混频器;被动混频器比主动混频器增加的噪声更小。它在低功耗下获得良好的性能。下图和方程式描述了搅拌机的原理。操作,其中vi(t)、vo(t)和lo(t)分别是混频器的输入、输出和本地振荡器(lo)信号。Lo(t)是基于方波的,包括奇次谐波分量,如下方程所示:搅拌机运行框图根据上述方程,Lo的3阶和5阶谐波可以与3阶和5阶谐波相连接。vi(t)中的谐波信号;或vi(t)中3阶和5阶谐波周围的噪声。因此,搅拌机性能下降。为了消除方波解调带来的副作用,AVCA5807采用了专用的谐波抑制电路。三、五次谐波分量从LO可以抑制超过12分贝。因此,lna输出噪声约为3阶和5阶谐波带不会向下转换为基带。因此,获得了较好的噪声系数。转换混音器的损耗约为-4db

8个通道的混合电流输出在内部相加。内部低噪音运行放大器用来把总电流转换成电压输出。设计了内部求和放大器以实现低功耗、低噪音和易用性。多个VCA5807S的CW输出可以在系统板上进一步组合,实现了一种8通道以上的连续波束形成器。

VCA5807 CW路径支持多个时钟选项。需要两个连续波时钟输入:N×_连续波时钟1×_cw时钟,其中_cw为cw发射频率,n可以是32、16、8、4或1。用户拥有为VCA5807选择最方便的系统时钟解决方案的灵活性。在32×_cw、16×_cw和8×中_CW模式,可支持三次和五次谐波抑制功能。因此,16×_cw和8×_cw模式比4×_cw和1×_cw模式获得更好的性能。16×_cw和32×_cw模式与其他模式相比,16×_CW模式可达到最佳相位精度。它是cw的默认模式操作。在这种模式下,需要16×_cw和1×_cw时钟。16×_CW产生16个准确的LO信号阶段。多个VCA5807可通过1×_cw同步,即多个VCA中的LO信号可以同一启动阶段。相位噪声规格仅对16倍时钟至关重要。1X时钟仅用于同步不需要低相位噪声。参见连续波时钟选择中的相位噪声要求。另外,1X时钟可以是频率为_cw的连续波,也可以是脉冲宽度t>的单脉冲(1/16 x_cw)。

每个混音器的时钟通过16×8分布交叉点开关。交叉点开关的输入是1X时钟的16个不同相位。它是建议对齐1 x_cw和16 x_cw时钟的上升沿。交叉点开关将具有适当相位延迟的时钟分配给每个混频器。例如,vi(t)是接收到的延迟为1/16 t的信号,应向搅拌机施加延迟的LO(t),以补偿1/16 t延迟。因此,该通道选择了22.5⁰延迟时钟,即2π/16

电源、接地和旁路

在混合信号系统设计中,电源和接地设计起着重要的作用。在大多数情况下,应足以布置印刷电路板(PCB),以使用VCA5807的单一接地平面。应注意,该地平面在系统内的各个部分之间进行了适当的划分,以便尽量减少模拟电路和数字电路之间的相互作用。此外,光隔离器或数字隔离器,如ISO7240可将模拟部分与数字部分完全分离。因此他们阻止了数字噪声污染模拟部分。表10列出了每个电源的相关电路块。

电源与电路块电源接地电路块LNA、衰减器、带夹具的PGA以及BPF、参考电路、CW AVDD(3.3VA)AVSS求和放大器、CW混频器,VCA SPI公司LNA、CW时钟电路、参考AVDD U 5V(5VA)AVSS电路VCA5807的所有旁路和电源应参考其相应的接地平面。应使用0.1μF陶瓷片电容器(尺寸0603或更小)绕过所有电源插脚。为了尽量减少引线和微量电感,电容器应尽可能靠近电源插脚。如果允许安装双面元件,这些电容器最好直接放置在包裹。此外,较大的双极去耦电容器(2.2微F至10微F,在较低频率下有效)也可以用于主电源销。这些元件可以放在附近的印刷电路板上(<0.5英寸或12.7英寸mm)至VCA5807本身。VCA5807有许多需要绕过的参考电源,例如CM-BYP、VHIGH和Vref_-in.这些插脚应至少绕过1微F;高值电容器可用于更好的低频。噪声抑制。为获得最佳效果,请选择低电感陶瓷片电容器(尺寸0402,>1微F)并将其尽可能靠近设备销。

高速混合信号装置对各种噪声耦合敏感。噪声的一个主要来源是来自序列化程序和输出缓冲区/驱动程序的切换噪声。对于VCA5807,已注意确保设备内模拟和数字电源之间的交互保持在最低限度。数量。数字和模拟部分耦合和传输的噪声程度取决于每个电源和接地连接的有效电感。电源有效电感较小接地销提高了噪声抑制。因此,使用多个管脚连接每个管脚供应和接地装置。在整个印刷电路板的设计过程中保持低电感特性是很重要的。使用适当的平面和层厚进行布局。

电路板布局正确的接地和旁路、短引线长度以及使用接地和电源平面对高频设计尤其重要。以高性能实现最佳性能像VCA5807这样的设备需要仔细注意印刷电路板的布局,以尽量减少电路板的影响。寄生和优化组件放置。多层印刷电路板通常确保最佳效果,并允许方便的部件放置。

此外,应考虑对连续波时钟路径进行适当的延迟匹配,特别是在具有高通道计数。例如,如果时钟延迟是16倍时钟周期的一半,22.5°C的相位误差可能存在。因此,信道间的定时延迟差异有助于波束形成器的精度。为了避免噪声通过电源插脚耦合,建议保持敏感的输入插脚,例如INM,INP,ACT管脚始终来自AVDD 3.3 V和AVDD 5 V平面。例如,跟踪或连接到这些插脚的通孔不应穿AVDD 3.3 V和AVDD 5 V平面。