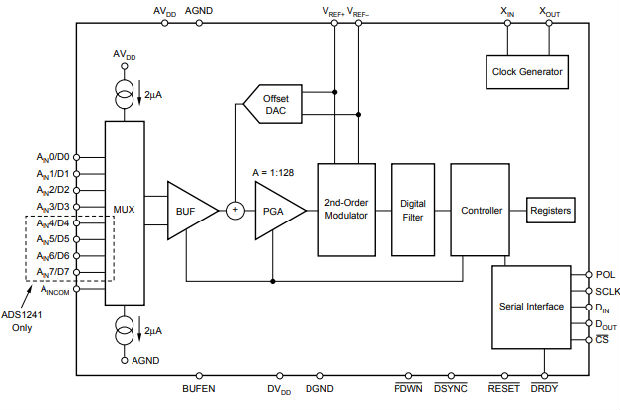

ADS1240和ADS1241具有精密宽动态范围,delta-sigma,具有24位分辨率的模数(A / D)转换器工作电压为2.7V至5.25V。delta-sigma A / D.转换器提供高达24位的无丢失代码性能和有效分辨率为21位。输入通道是多路复用的。内部缓冲可以选择为直接连接提供非常高的输入阻抗传感器或低电平电压信号。倦怠电流源提供允许检测开路或短路传感器。8位数模转换器(D / A)提供偏移校正,其范围为满量程范围(FSR)的50%。可编程增益放大器(PGA)提供可选增益1到128,有效分辨率为19位,增益为128使用二阶Δ-Σ调制器和可程有限脉冲响应(FIR)滤波器完成A / D转换提供同时50Hz和60Hz的陷波。参考输入是差分的,可用于比率转换串行接口与SPI兼容。最多8位数据还提供了可用于输入或输出的I / O.该

ADS1240和ADS1241专为智能变送器,工业过程控制中的高分辨率测量应用而设计称重秤,色谱仪和便携式仪器。

特征

24个没有丢失的代码

同时50Hz和60Hz的拒绝(-90dB MINIMUM)

0.0015%INL

21 BITS有效解决方案(PGA = 1),19位(PGA = 128)

PGA从1到128增益

单循环沉降

可编程数据输出速率

外部差别参考0.1V至5V

片上校准

SPI?兼容

2.7V至5.25V供电范围

600μW功耗

注意八个输入通道

最多8个数据I / O.

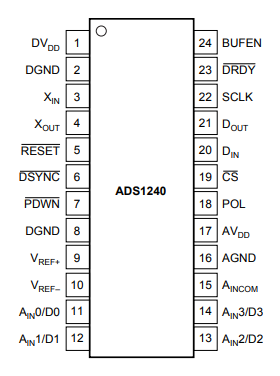

引脚配置图(ADS1240)

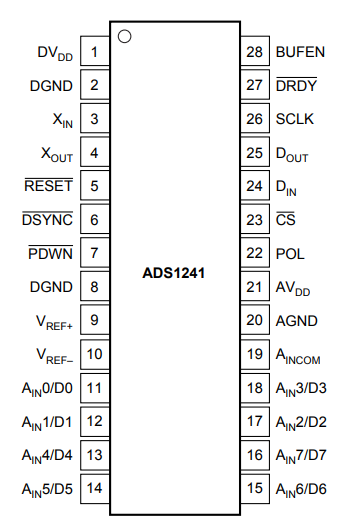

引脚配置图(ADS1241)

引脚说明(ADS1240)

号码名称说明

1个DVDD数字电源

2 DGND数字地

3 XIN时钟输入

4 XOUT时钟输出,与外部晶体一起使用。

5 RESET低电平有效,重置整个设备。

6 DSYNC低电平有效,同步控制

7 PDWN低电平有效,掉电。 断电功能可关闭模拟和数字电路。

8 DGND数字地

9 VREF +正差分参考输入

10 VREF-负差分参考输入

11 AIN0 / D0模拟输入0 /数据I / O 0

12 AIN1 / D1模拟输入1 /数据I / O 1

13 AIN2 / D2模拟输入2 /数据I / O 2

14 AIN3 / D3模拟输入3 /数据I / O 3

15 AINCOM模拟输入公共端,如果未使用,则连接到AGND。

16 AGND模拟地

17 AVDD模拟电源

18 POL串行时钟极性

19 CS低电平有效,片选

20 DIN串行数据输入,施密特触发器

21 DOUT串行数据输出

22 SCLK串行时钟,施密特触发器

23 DRDY低电平有效,数据就绪

24 BUFEN Buffer Enable

密码描述(ADS1241)

号码名称说明

1个DVDD数字电源

2 DGND数字地

3 XIN时钟输入

4 XOUT时钟输出,与外部晶体一起使用。

5 RESET低电平有效,重置整个设备。

6 DSYNC低电平有效,同步控制

7 PDWN低电平有效,掉电。断电功能可关闭模拟和数字电路。

8 DGND数字地

9 VREF +正差分参考输入

10 VREF-负差分参考输入

11 AIN0 / D0模拟输入0 /数据I / O 0

12 AIN1 / D1模拟输入1 /数据I / O 1

13 AIN4 / D4模拟输入4 /数据I / O 4

14 AIN5 / D5模拟输入5 /数据I / O 5

15 AIN6 / D6模拟输入6 /数据I / O 6

16 AIN7 / D7模拟输入7 /数据I / O 7

17 AIN2 / D2模拟输入2 /数据I / O 2

18 AIN3 / D3模拟输入3 /数据I / O 3

19 AINCOM模拟输入公共端,如果未使用,则连接到AGND。

20 AGND模拟地

21 AVDD模拟电源

22 POL串行时钟极性

23 CS低电平有效,片选

24 DIN串行数据输入,施密特触发器

25 DOUT串行数据输出

26 SCLK串行时钟,施密特触发器

27 DRDY低电平有效,数据就绪

28 BUFEN Buffer Enable

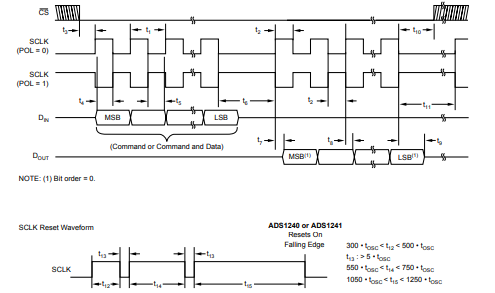

时序图1

时序图2

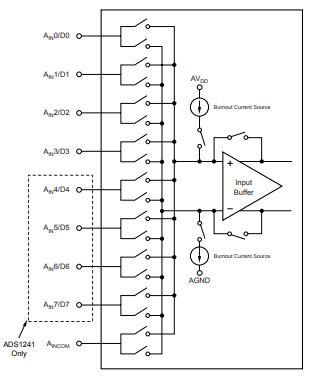

输入多路复用器提供在任何输入通道上选择的差分输入的任何组合,如如图1所示。例如,如果选择AIN0作为正差分输入通道,任何其他通道都可以选择作为差分输入的负端子渠道。使用这种方法,最多可以有八个单端输入通道或四个独立差分ADS1241的输入通道和四个单端输入通道或两个独立的差分输入通道ADS1240。请注意,AINCOM可以视为输入渠道。

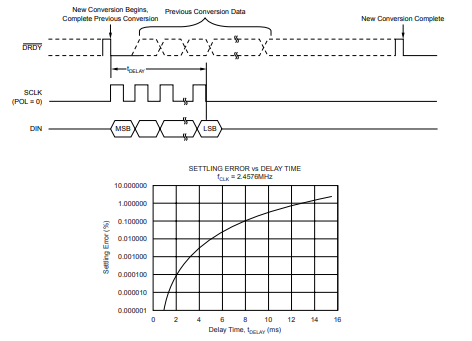

ADS1240和ADS1241具有单周期稳定功能数字滤波器,在第一次转换时提供有效数据在新频道选择之后。为了尽量减少建立错误,将MUX更改同步到转换开始,由DRDY的下降沿表示。在

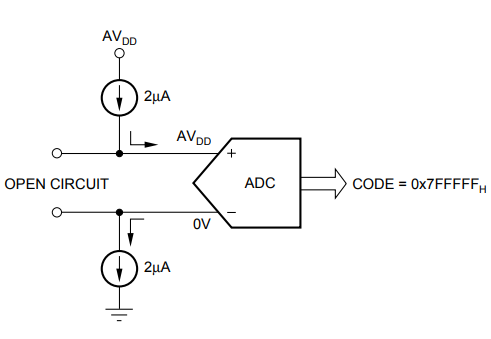

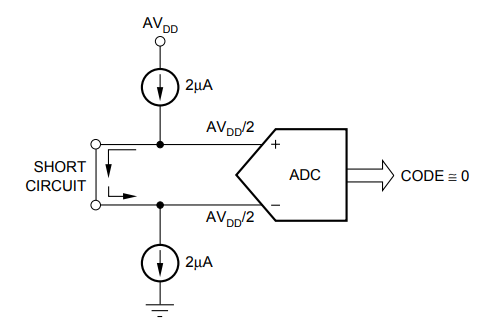

换句话说,通过WREG发出MUX变更DRDY变为低电平后立即命令最小化解决错误。增加转换之间的时间开始(DRDY变为低电平)并且MUX更改命令(tDELAY)导致转换中的建立错误数据,如图2所示。烧毁当前的来源倦怠电流源可用于检测传感器短路或开路条件。设置职业倦怠SETUP寄存器中的电流源(BOCS)位激活两个2μA电流源称为燃尽电流源。一电流源连接到转换器的负输入,另一个连接到转换器积极的投入。图3显示了开路传感器的情况。这个

是多种远程连接传感器的潜在故障模式。正输入的当前来源起作用作为一个上拉,导致积极的输入转为正面模拟电源,负输入电流源充当下拉,导致负输入地面。因此,ADS1240 / 41输出满量程(7FFFFF十六进制)。

输入缓冲区

没有缓冲器的ADS1240 / 41的输入阻抗使能约为5MΩ/ PGA。对于需要的系统ADS1240 / 41提供极高的输入阻抗斩波稳定的差分FET输入电压缓冲器。 什么时候激活后,缓冲器会提升ADS1240 / 41输入阻抗大约5GΩ缓冲器的输入范围约为50mV至AVDD - 1.5V。缓冲区的线度将降低到此范围之外。应调整差分信号以使两个信号均匀在缓冲区的输入范围内。可以使用BUFEN引脚或者使用BUFEN使能缓冲器ACR寄存器中的BUFEN位。当缓冲区打开时BUFEN引脚为高电平且BUFEN位置1。如果BUFEN引脚为低电平,缓冲器禁用。如果BUFEN位是设置为零,缓冲区也被禁用。

缓冲区在激活时会消耗额外的电流。该缓冲器所需的电流取决于PGA设置。当PGA设置为1时,缓冲区大约使用50μA;当PGA设置为128时,缓冲器使用大约500μA。PGA可编程增益放大器(PGA)可设置为增益1,2,4,8,16,32,64或128.使用PGA可以改善A / D转换器的有效分辨率。例如,用PGA为1的5V满量程信号,A / D转换器即可降低到1μV。 PGA为128,满量程号对于39mV,A / D转换器可以分辨到低至75nV。AVDDPGA设置高于4时电流增加。OFFSET DAC

PGA的输入可以移动满量程输入的一半使用偏移DAC(ODAC)寄存器的PGA范围。该ODAC寄存器是一个8位值; MSB是标志和个LSB提供偏移的幅度。使用偏移DAC不会降低A / D的性能转换器。有关ODAC的更多详细信息,请参阅TI申请报告SBAA077调制器是单环二阶系统。该调制器以源自的时钟速度(fMOD)运行外部时钟(fOSC)。

ADS1240和ADS1241均支持自身和系统校准。ADS1240和ADS1241的自校准可校正内部失调和增益误差,并由三个命令处理:SELFCAL,SELFGAL和SLEFOCAL。 SELFCAL命令执行偏移和增益校准。SELFGCAL执行增益校准,SELFOCAL执行偏移校准,每个校准需要两个tDATA周期完成。在自校准期间,ADC输入在内部与输入引脚断开。PGA必须设置为在发出SELFCAL或SELFGCAL命令之前1。任何发出SELFOCAL命令时允许PGA。对于例如,如果使用PGA = 64,则首先设置PGA = 1并发出。