DS2165Q点击型号即可查看芯片规格书

DS2165Q ADPCM处理器芯片是一个专用的数字信号处理(DSP)的芯片,该芯片已优化,以在3进行自适应差分脉冲编码调制(ADPCM)语音压缩不同的费率。该芯片可以被编程以压缩(扩展)64kbps的语音数据下降到(从)无论是32kbps的,24kbps,16kbps的还是。32kbps压缩遵循CCITT规定的算法建议G.721(1986年7月)和ANSIT1.301文件(1987年4月)。压缩到24kbps符合ANSIT1.303文件。压缩到16kbps的如下专有算法由DallasSemiconductor开发的。在DS2165Q可以的即时切换压缩算法。这允许用户最大程度地利用可用带宽的一个动态的基础上。

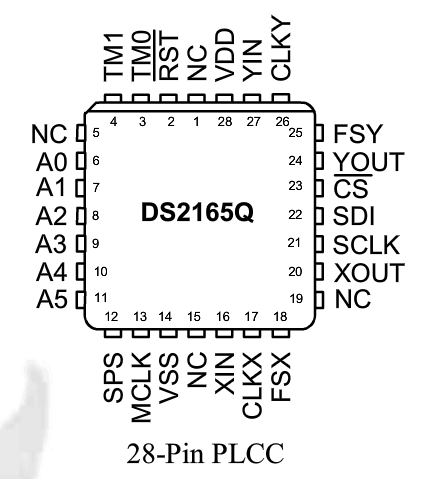

图1

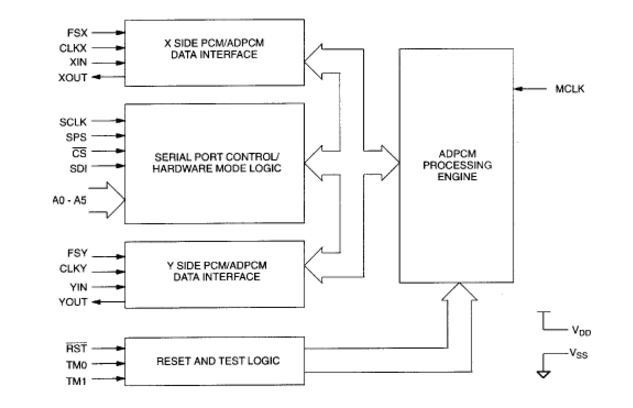

概观

DS2165Q包含三个主要功能块:一个高性能(10MIPS)的DSP引擎,二独立的PCM接口(X和Y)直接连接到串行时分多路复用(TDM)背板和一个串行口,可以通过一个外部控制器上配置的即时的设备。10MHz的主时钟是必需的,由DSP引擎。该DS2165Q可以被配置成执行以下两种扩张,2按压,或一个膨胀和一个压缩。在PCM/ADPCM数据接口支持的数据速率从256KHz的到4.096MHz。通常,PCM数据速率是1.544MHz为M-法和为2.048MHz的A律。上的器件样品的串行输入的PCM或ADPCM的比特流中的每个信道在用户编程的输入时隙中,处理数据和一个用户可在输出其结果编程输出时隙。每个PCM接口有一个控制寄存器,指定的功能特性(压缩,扩展,旁路和闲置),数据格式(M-法律或A律)和算法复位控制。与SPS绑脚高,软件模式被使能,串行端口可用于配置该设备。在此模式中,一个新的解决方案允许多个设备共用一个3线控制总线,简化了系统级互连。使用SPS低,硬件模式被启用。此模式禁用串行端口映射和一定的控制寄存器位的一些地址和串口引脚。在硬件模式下,无需外部主机是必需的控制器和所有的PCM/ADPCM输入和输出时隙默认为0时隙。

硬件复位

RST允许用户重新设置两个信道的算法和内部寄存器的内容。该引脚必须保持为低电平在系统上电的主时钟后至少1ms的稳定,以确保设备已正确初始化。RST改变或从硬件时也应置模式。RST清除的控制寄存器的两个通道,除了IPD位的所有位;瞳距位两个通道都设置为1。

软件模式

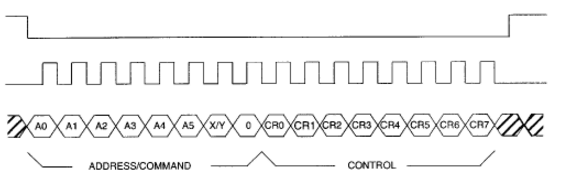

连接SPS高使得软件的模式。在此模式下,外部主机控制器写通过输入SCLK,SDI和配置数据DS2165Q通过串行端口CS(图2)。每写入DS2165Q可以是一个2字节写或4字节的写入。一个2字节操作包括的地址/命令字节(ACB),后跟一个字节来配置控制寄存器(CR)对任一在X或Y通道。4个字节的写入由ACB,随后一个字节配置在CR,然后1字节设置输入时隙和另一个字节来设定输出时隙。

图2

控制寄存器

控制寄存器确定空闲,算法复位,旁路,数据格式,和信道编码的选择的信道。在X侧和Y侧的PCM接口可以独立地禁用(输出三态)用瞳距。当IPD设置两个通道,器件进入低功耗待机模式。在这种模式下,串行端口不能操作比39kHz更快。ALRST重置所选择的频道为初始值的算法系数。ALRST被清除通过该装置,当该算法在完成复位。

图3