VSP2232点击型号即可查看芯片规格书

特征

CCD信号处理

–相关双抽样(CDS)

–可编程黑色夹持

可编程增益放大器(PGA)

––6-db到42 db增益范围

10位数字数据输出

–最高36兆赫转换率

–无缺失代码

76分贝信噪比

便携式操作

–低压:2.7 V至3.6 V

–低功率:3.0 V时为130 mW(典型)

–待机模式:6兆瓦

说明

VSP2232是一个完整的混合信号处理IC。

用于提供信号调节和CCD输出的模数转换

数组。主CCD通道提供相关双采样(CD)提取视频信息从像素,A–6-db到42 db增益,带数字控制适用于不同的照明条件和黑色水平夹紧以获得准确的黑色水平参考。

输入信号的夹紧和输入的偏移校正还执行CDS。稳定增益控制是线性的。

单位:dB。此外,黑度很快恢复增益变化后。

VSP262Y(12位20兆赫)单芯片产品。

VSP232Y采用48针LQFP封装。

由单个3-V/3.3-V电源供电。

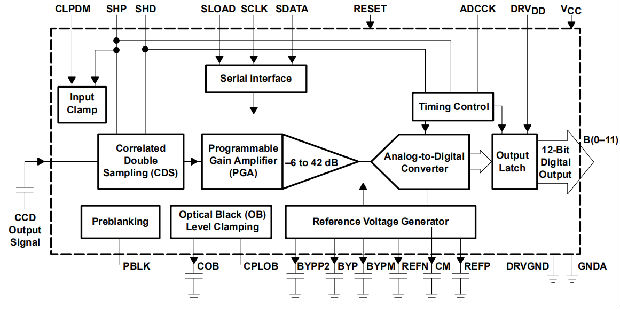

VSP2232方块图

详细描述

介绍

VSP2232是一个完整的混合信号集成电路,包含与处理相关的所有关键功能。

在摄像机、数字静止摄像机、安全摄像机或类似装置中的CCD成像仪输出信号。

应用。本数据表首页显示了一个简化的方框图。

VSP2232包括相关双采样(CDS)、可编程增益放大器(PGA)、模数转换器(ADC)、输入钳位、光学黑色(OB)电平钳位回路、串行接口、定时控制和基准电压发生器。我们建议在CCD输出和VSP2232之间有一个片外发射极跟随器缓冲器。

CCDIN输入。可进行PGA增益控制、时钟极性设置和操作模式选择。

通过串行接口。当复位销变低时,所有参数都会重置为默认值。

从时钟异步。

相关双采样器(CDS)

在一个像素周期内对CCD成像仪的输出信号进行两次采样,一次在参考间隔处采样,以及另一个在数据间隔。

减去这两个样本,提取像素的视频信息,并去除与这两个间隔相同或相关。

因此,CD对于降低复位噪声和低频噪声非常重要

CD通过片外耦合电容器(CIN)驱动。强烈建议使用交流耦合,因为CCD输出信号的直流电平通常过高(几伏),CD无法正常工作。0.1-微FCIN推荐使用电容器,但取决于应用环境

相关双采样器(CDS)(续)

此外,建议使用能够驱动10 pF以上的片外发射极跟随器缓冲器,因为在输入端可以看到采样电容和少量的杂散电容。模拟输入信号CCDIN引脚的范围为1 Vp–p,CD的适当共模电压约为0.5 V至1.5 V

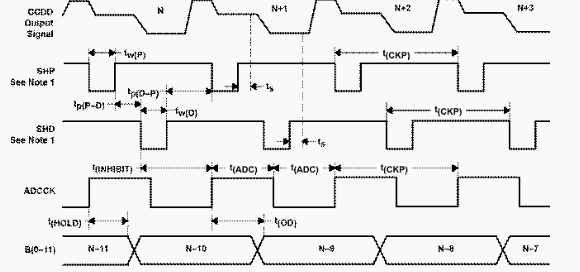

参考电平在SHP激活期间采样,电压电平保持在采样电容器上。

(1)在SHP后缘。在SHD激活期间对数据电平进行采样,电压电平为固定在SHD后缘的采样电容器C(2)上。然后,开关电容放大器执行这两个级别的减法。

可通过串行接口选择SHP/SHD的激活极性(高激活或低激活),参见详细信息的串行接口。SHP/SHD的默认值为低激活。然而,在通电后,这个值未知。因此,必须使用串行接口将其设置为适当的值,或重置为重置管脚的默认值。本数据表中的说明和时序图均基于低极性激活(默认值)。

输入钳和虚拟像素钳缓冲的CCD输出电容耦合到VSP2232。输入钳的目的是恢复输入信号的直流分量,该分量随交流耦合而丢失,并建立所需的直流偏压点。

对于CD。输入电平被固定在虚拟像素间隔期间的内部参考电压参考值(1.25 V)。更具体地说,当两个CLPDM

SHP激活后,假钳位功能激活。如果虚拟像素和/或CLPDM脉冲在您的系统中不可用,只要夹紧,CLPOB脉冲就可以用来代CLPDM。

在黑色像素期间发生。在这种情况下,CPLDM管脚(与CLPOB同步激活)和SHP在光学黑像素间隔期间变为激活状态,然后虚拟夹持功能变为激活状态。

可通过串行接口选择CLPDM和SHP(有功高或有功低)的有功极性。

详见串行接口。CLPDM和SHP的默认值为低激活。然而,权力之后在上,此值未知。因此,必须使用串行接口将其设置为适当的值,或通过重置管脚重置为默认值。本数据表中的说明和时序图均为基于激活低极性(默认值)。

高性能模数转换器

模数转换器(ADC)采用全差分和流水线结构。这个ADC很好适用于低压运行、低功耗要求和高速应用。它保证输出数据的10位分辨率,无丢失代码。VSP2232包括参考电压发生器对于ADC。refp(正参考,针脚38)、refn(负参考,针脚39)和cm(共模

电压(针脚37)应使用0.1-微F陶瓷电容器旁路至接地。不要使用这个电压系统中的其他任何地方,因为它会影响这些参考电平的稳定性,然后导致ADC性能下降。这些是模拟输出引脚,因此不要从外部施加电压。

可编程增益放大器(PGA)

PGA增益的特性。PGA提供的增益范围为-6 dB至42 dB,其中以分贝为单位是线性的。增益由10位分辨率的数字代码控制,可通过串行接口,有关详细信息,请参阅串行接口部分。增益控制代码的默认值为128(pga增益=0 dB)。然而,在通电后,这个值是未知的。因此,必须将其设置为使用串行接口的适当值,或通过重置引脚重置为默认值光学黑色(OB)电平钳环

为了正确地提取视频信息,必须将CCD信号引用到一种成熟的光学黑色。

(OB)水平。VSP22232具有一个自动校准回路,用于使用光学黑色像素建立OB级别。

从CCD成像仪输出。OB像素的输入信号电平被标识为实际的OB电平和当CLPOB处于活动状态时,应在此期间关闭循环。在有效像素间隔期间,参考CCD输出信号的电平被OB电平钳位回路夹持到OB电平。确定循环时间常数,需要一个片外电容器,并应连接到COB(引脚28)。时间常数t

c是连接到COB的电容器值,i(min)是控制DAC在OB电平钳位回路,0.15μA相当于DAC输出电流的1 LSB。当C为0.1微F时,则

时间常数t为40.7μs。此外,转换速率(sr)在方程式2中给出。

C是连接到COB的电容器值。i(max)是控制DAC在OB电平钳位回路,153微安相当于1023 LSB的DAC输出电流。

通常,高速时的OB级夹持会导致夹持噪音(或白色条纹噪音)。但是,噪音将通过增大电容器大小而减小。另一方面,较大的电容器需要更长的时间从待机模式恢复,或在电源接通后立即恢复。因此,我们建议0.1-μF至0.22-μF Capcitor。但是,它取决于应用程序环境,并使用建议采用试切法。

预消隐和数据延迟

在消隐时间间隔内,一些共有器件有较大的瞬态输出信号。这些信号可能会超过VSP23232的1-VP输入信号范围,并将使VSP2222超速进入饱和状态。从饱和状态恢复的时间可能很长。为了避免这种情况,VSP2232具有输入消隐(或预消隐)功能。当PBLK变低时,CCDIN输入与内部CDS级断开,防止大的瞬态通过。vsp2232的数字输出将在adcck的第11个上升沿从pblk设置为低后转到所有零,以适应vsp2232的时钟延迟。在此模式下,数字输出数据以11个时钟周期(数据延迟为11)的延迟从ADCCK的上升沿输出。在正常操作模式下,它不同于预消隐模式。数字输出数据在ADCCK的上升沿输出,延迟9个时钟周期(数据延迟为9)。

为了保持OB钳位稳定准确,PBLK激活期间不应激活CLPOB。由于CCDIN输入与内部电路断开,即使CLPOB激活时自动校准回路也应关闭。然后,OB钳位电平不同于由CCD成像仪输出建立的实际OB电平。丢失的OB钳位会影响图像质量。

如果输入电压高于电源轨0.3 V或低于接地轨0.3 V,保护二极管将打开,以防止输入电压进一步升高。如此高的摆动信号可能会对VSP2232造成设备损坏,应避免。

详细描述(续)待机模式

为了省电,当VSP2222不使用时,可以通过串行接口将VSP2222设置为待机模式(或断电模式)。详见串行接口。在此模式下,所有功能块都被禁用,数字输出将变为所有零。消耗电流将降至2 mA。由于所有旁路电容器在此模式下都将放电,因此需要相当长的时间(通常为200 ms至300 ms)才能从待机模式恢复。

电压基准

VSP22232所需的所有参考电压和偏压电流均由其内部带隙电路产生。CDS和ADC使用三个参考电压:refp(正参考电压,插脚38)、refn(负参考电压,插脚39)和cm(共模电压,插脚37)。所有的refp、refn和cm应使用适当的电容器(例如:0.1-微F陶瓷电容器)进行严重的去耦。不要在系统中的任何其他地方使用这些电压,因为它会影响这些参考电平的稳定性,并导致ADC性能下降。这些是模拟输出引脚,因此不要从外部施加电压。

BYPP2(针脚29)、BYP(针脚31)和BYPM(针脚32)也是模拟电路中使用的参考电压。BYP应使用0.1-μF陶瓷电容器接地。bypp2和bypm的电容值影响阶跃响应。我们认为,在许多应用中,200 pf到600 pf是合理的值。但是,它取决于应用环境,建议使用“切割并尝试”方法进行仔细的调整。所有的bypp2、byp和bypm都应该用适当的电容器进行严重的去耦。不要在系统中的任何其他地方使用这些电压,因为它会影响这些参考电平的稳定性,并导致性能下降。这些是模拟输出引脚,因此不要从外部施加电压。

附加输出延迟控制

VSP22232可以通过串行接口通过寄存器设置来控制输出数据的延迟时间。在某些情况下,输出数据的转换会影响模拟性能。通常,通过调整ADCCK的定时来避免这种情况。在ADCCK定时不能调整的情况下,这种输出延迟控制可以有效地降低瞬态噪声的影响。详见串行接口。

串行接口有一个2字节移位寄存器和各种并行寄存器,用于控制VSP2232的所有数字可编程功能。写入这些寄存器由四个信号(sload、sclk、sdata和reset)控制。要启用移位寄存器,必须将sload拉低。sdata是串行数据输入,sclk是移位时钟。SData的数据被带到SCLK上升沿的移位寄存器中。数据长度应为2字节。在2字节移位操作之后,移位寄存器中的数据将传输到sload上升沿的并行锁存器。除了并行锁存器,还有几个专用于设备特定功能的寄存器,它们与ADCCK时钟同步。将并行锁存器中的数据写入这些寄存器需要5到6个时钟周期。因此,为了完成数据更新,它必须在SLOAD上升沿的并行锁存之后等待五到六个时钟周期。

VSP2232有两种驱动片上A/D转换器的选项。通过串行接口访问配置寄存器,可以选择内部驱动模式和外部驱动模式。内部驱动方式,即A/D转换器的驱动时钟,由片内定时控制电路根据SHP和SHD信号自动生成。外部驱动方式为主时钟(ADCCK),直接驱动片上A/D转换器。数字数据输出与主时钟(ADCCK)同步,与驱动模式无关。

CDS和ADC由SHP/SHD操作,它们的衍生时钟由片内定时发生器产生。数字输出数据与ADCCK同步。CCD信号、SHP/SHD、ADCCK和输出数据之间的定时关系如VSP2222 CDS定时规范所示。CLPOB用于在OB像素间隔期间激活黑色电平钳位环路,CLPDM用于在虚拟像素间隔期间激活输入钳位。如果系统中没有CLPDM脉冲,只要在黑色像素期间进行夹持,就可以使用CLPOB脉冲代替CLPDM,有关详细信息,请参阅输入夹和虚拟像素夹。SHP/SHD、CLPOB、CLPDM的时钟极性可通过串行接口独立设置,具体见串行接口部分。本数据表中的说明和时序图均基于激活低极性(默认值)。为了保持稳定和准确的OB钳位,建议在PBLK激活期间不要激活CLPOB。有关详细信息,请参阅预消隐和数据延迟。在待机模式下,ADCCK、SHP、SHD、CLPOB和CLPDM被内部屏蔽并拉高。

电源、接地和设备去耦建议

VSP22232集成了一个非常高精度和高速的模拟-数字转换器和模拟电路,很容易受到来自轨道或其他地方的任何外来噪声的影响。因此,尽管VSP2232具有模拟和数字电源插脚,但应将其视为模拟组件,除DRV以外的所有电源插脚应仅由系统的模拟电源供电。这将确保最一致的结果,因为数字电源线往往携带高水平的宽带噪声,否则将耦合到设备中,并降低可实现的性能。DD

正确接地、短引线长度和使用接地平面对高频设计也非常重要。为获得最佳性能,建议使用多层PC板,因为它们具有明显的优势,如减小接地阻抗、通过接地层分离信号层等。强烈建议将VSP2232的模拟和数字接地引脚连接在集成电路上,并且仅连接到系统的模拟接地。.数字输出(B(11:0))的驱动级通过专用电源插脚(DRV)供电,并应与其他电源插脚完全分开,或至少用铁氧体珠隔开。还建议尽可能降低输出数据线上的电容负载(通常小于15 pF)。较大的电容性负载需要较高的充电电流,这是由于浪涌会反馈到VSP2232的模拟部分并影响性能。

如有可能,应使用外部缓冲器或闩锁,以提供额外的好处,将VSP2232与数据线上的任何数字噪声活动隔离开来。此外,与每条数据线串联的电阻有助于将浪涌电流降至最低。100Ω至200Ω范围内的值将限制输出级的瞬时电流,并且必须在输出电平从低到高或从高到低变化时为寄生电容重新充电。由于工作速度快,转换器也会产生高频电流瞬变和噪声,这些电流瞬变和噪声会反馈到电源线和参考线中。这就需要充分绕过电源和参考销。在大多数情况下,0.1-微F陶瓷芯片电容器足以将参考针去耦。应使用钽(1微F至22微F)和陶瓷(0.1微F)电容器的平行组合将电源针与接地平面分离。去耦的有效性在很大程度上取决于单个触针的接近程度。DRV应与DRVgnd的邻近位置分离。必须特别注意COB、BYPP2和BYPM的旁路,因为这些电容值决定了设备的重要模拟性能。

定时规范

机械数据

PT(S-PQFP-G48)塑料四芯扁平封装

注:a.所有线性尺寸单位均为毫米。

B.本图如有更改,恕不另行通知。

c.属于JEDEC MS-026

d.这也可以是一个热增强塑料包装,其引线与模垫相连。