AD8009AR点击型号即可查看芯片规格书

AD8009AR是一款超高速电流反馈放大器具有惊人的5,500 V /μs压摆率导致上升时间为545 ps,非常适合作为脉冲放大器。高压摆率降低了压摆率限制的影响导致所需的440 MHz的大信号带宽高分辨率视频图形系统。在宽带宽内保持信号质量,最坏情况下失真-40dBc@250MHz(G = + 10,1 V p-p)。对于应用程序多音信号,如IF信号链,三阶在相同频率下实现12dB的截距(3IP)。这个失真性能加上电流反馈架构使AD8009成为增益的灵活组件F / RF信号链中的级放大器。

AD8009能够提供超过175 mA的负载电并且在维护时将驱动四个后端终止的视频负载差分增益和相位误差分别为0.02%和0.04,分别。高驱动能力也反映在能够在70MHz时提供10dBm的输出功率-38 dBc SFDR。

AD8009采用小型SOIC封装,并将提供工作温度范围为-40°C至+ 85°C工业温度范围。

AD8009也采用SOT-23-5封装,可以运行在0C至70C的商业温度范围内。

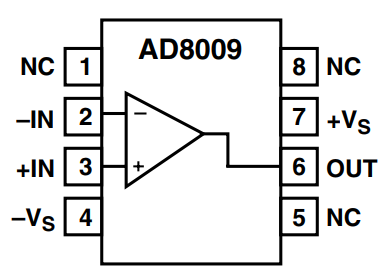

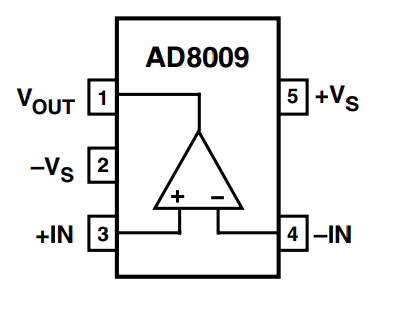

功能块图

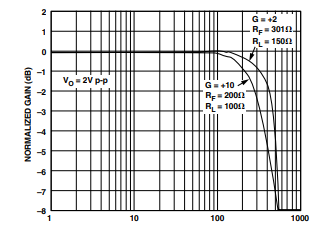

频率响应(MHz)

大信号频率响应; G = +2和+10

频率响应(MHz)

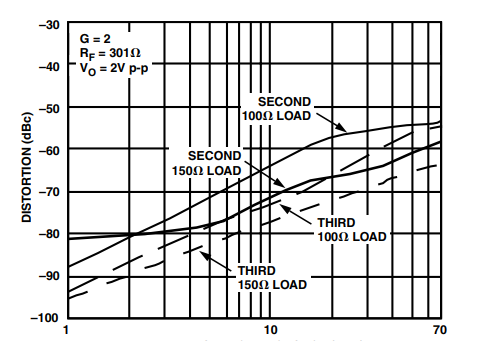

失真与频率的关系; G = +2

最大功率耗散

AD8009可以安全消耗的最大功率受结温升高的影响。塑料封装器件的最大安全结温由塑料的玻璃化转变温度决定,约150°C。暂时超过此限制可能会导致由于应力的变化导致参数性能的变化通过包裹施加在模具上。

虽然AD8009内部具有短路保护功能,但也可以这样做不足以保证在所有条件下都不超过最高结温(150°C)。确保正确操作,有必要观察最大功率降额曲线。

应用

所有电流反馈运算放大器都受杂散电容的影响在他们的-INPUT上。TPC35和36说明了AD8009

对这种电容的反应。TPC 35显示通过放置a可以扩展带宽电容与增益电阻并联。小信号脉冲

在TPC 36中示出了对应于电容/带宽的这种增加的响应。作为实际考虑,电容上的电容越高

-INPUT到GND,需要更高的RF才能最小化峰值/振铃。RF滤波器驱动器输出驱动能力,宽带宽和低失真。

AD8009非常适合创建可以的增益模块驱动RF滤波器。许多这些过滤器都需要输入由50Ω源驱动,而输出必须终止50Ω,滤波器可显示其指定的频率响应。TPC 37示出了用于驱动和测量频率的电路一个滤波器的响应,Wavetek 5201可调谐带通滤波器调谐到50 MHz中心频率。 HP8753D网络为测量提供刺激信号。分析仪有50Ω源阻抗,用于驱动端接的电缆AD8009的高阻抗同相输入端为50Ω。

AD8009的增益设置为+2。系列50Ω电阻器输出,以及滤波器提供的50Ω终端它的终止,为测量产生整体单位增益路径。TPC 38的频率响应曲线显示了该电路通带中的插入损耗为1.3 dB

阻带中的75 dB抑制。

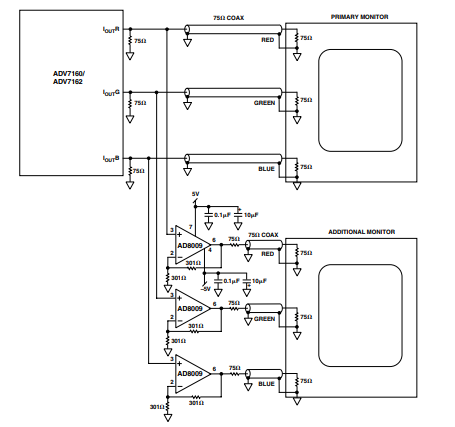

使用三个AD8009驱动附加高分辨率监视

RGB显示器驱动程序

高分辨率计算机显示器需要非常高的全功率带宽信号,以最大化其显示分辨率。该驱动这些监视器的RGB信号通常由提供一个电流输出RAMDAC,可以直接驱动一个75Ω的双倍电压终止线。有时候需要传送相同的输出额外的监视器终止由内部提供每个监视器都禁止简单地连接第二个监视器监控与第一个并行。额外的缓冲必须提供。上图显示了两个高分辨率的连接图监视器由ADV7160或ADV7162驱动,220 MHz(每秒百万像素)三重RAMDAC。这个像素率要求驱动器的全功率带宽至少为其一半像素速率或110 MHz。这是为了提供良好的分辨率在零刻度和满刻度之间摆动的最坏情况信号在相邻像素上。主监视器以传统方式连接在75Ω的每端有一个75Ω的接地端接电缆。有时这种配置称为“双端接”,并在驱动器为高输出阻抗时使用电流源。对于附加监视器,每个RGB信号接近RAMDAC输出应用于高输入阻抗,AD8009的同相输入,其增益为+2。该输出每个驱动器串联75Ω电阻,电缆和终端因此,监视器中的电阻器将输出信号除以2提供整体统一收益。该方案称为“后端接”并在驱动器输出较低时使用阻抗电压源。后端需要信号电压是监视器看到的值的两倍。双端接要求输出电流加倍在监视器终止中流动的值。

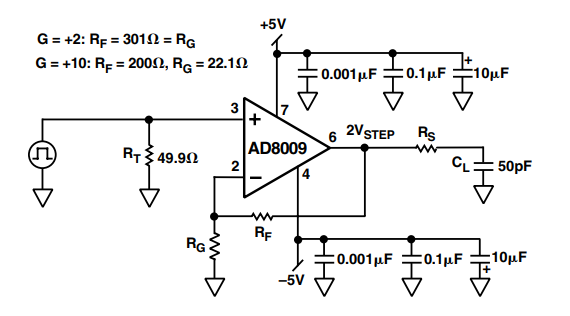

驱动电容负载

容性负载,如某些A / D转换器所示,有时可能是运算放大器驱动依赖的挑战关于运算放大器的架构。大部分问题都是由此造成的由运放和输出阻抗产生的极点被驱动的电容器。这会产生额外的相移最终会导致运算放大器变得不稳定。防止不稳定和改善安置时间的一种方法驱动电容器是在两者之间串联一个电阻器运算放大器输出和电容器。反馈电阻仍然是直接连接到运算放大器的输出,而系列电阻器提供了一些容性隔离运算放大器输出。

上图显示了AD8009驱动50 pF的电路加载。RS = 0时,AD8009电路将不稳定。为一个获得+2和+10,通过实验发现设置RS对于42.2Ω,最小化0.1%的建立时间,步长为2V输出。测得0.1%的稳定时间为40ns这个电路。对于较小的容性负载,较小的RS将产生最佳建立时间,而更大的电容需要更大的RS负载。当然,更大的电容总是需要更多确定精确度的时间比较小的时间,这个将由于所需的RS增加而延长。充其量,一个给定RC组合将需要大约七个时间常数单独收到0.1%,所以也会达到限制大的电容不能由给定的运算放大器驱动而且仍然是满足系统所需的稳定时间规范。