CAT25640VI-GT3点击型号即可查看芯片规格书

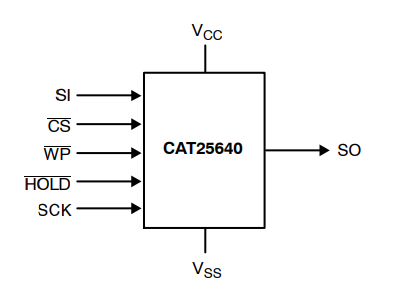

CAT25640VI-GT3内部是EEPROM串行64-Kb SPI器件组织为8Kx8位。这具有64字节的页面写缓冲区和支持串行外设接口(SPI)协议。该设备是通过片选(CS)输入启用。另外,还需要总线信号是时钟输入(SCK),数据输入(SI)和数据输出(SO)线。HOLD输入可用于暂停任何串行与CAT25640设备通信。该设备功能软件和硬件写保护,包括部分以及全阵列保护。

特征

兼容20 MHz(5 V)SPI

1.8 V至5.5 V电源电压范围

SPI模式(0,0)和(1,1)

64字节页面写入缓冲区

自定时写周期

硬件和软件保护

块写保护- 保护1 / 4,1 / 2或整个EEPROM阵列

低功耗CMOS技术

1,000,000个编程/擦除周期

100年数据保留

工业和扩展温度范围

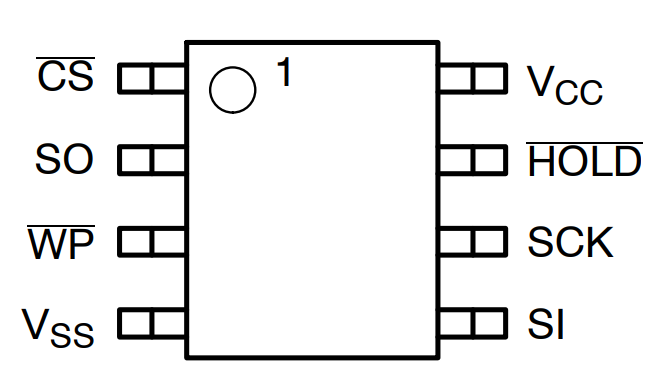

SOIC,TSSOP 8引脚和UDFN 8焊盘封装

该器件无铅,无卤素/ BFR,RoHS

功能符号图

PIN配置图

绝对最大额定值

工作温度-45至+ 130°C

储存温度-65至+ 150°C

任何引脚相对于地的电压(注1)-0.5至+6.5 V.

超过最大额定值表中列出的应力可能会损坏设备。如果超出任何这些限制,则设备功能不应该假设,可能会发生损坏并且可靠性可能受到影响。任何引脚上的直流输入电压不应低于-0.5 V或高于VCC + 0.5 V.在转换期间,任何引脚上的电压可能下冲至不低于-1.5 V或过冲至不超过VCC + 1.5 V,持续时间小于20 ns。

可靠性特征

符号参数最小单位

1.NEND(注3)Endurance 1,000,000程序/擦除周期

TDR数据保留100年

2.最初测试这些参数,并在根据适当的AEC-Q100影响参数的设计或工艺变化之后进行测试

和JEDEC测试方法。

3.页面模式,VCC = 5 V,25°C

引脚说明

SI:串行数据输入引脚接受操作码,地址和数据。在SPI模式(0,0)和(1,1)中,输入数据被锁存在SCK时钟输入的上升沿。

SO:串行数据输出引脚用于传输数据装置。在SPI模式(0,0)和(1,1)中,数据被移出在SCK时钟的下降沿。

SCK:串行时钟输入引脚接受提供的时钟由主机用于同步通信主机和CAT25640之间。

CS:芯片选择输入引脚用于启用/禁用CAT25640。当CS为高电平时,SO输出为三态(高电平)

阻抗)并且设备处于待机模式(除非内部写操作正在进行中)。每次沟通主机和CAT25640之间的会话必须以a开头从高到低的过渡,从低到高结束CS输入的转换。

WP:写保护输入引脚将允许所有写操作高电平时对设备的操作。当WP引脚是低电平和状态寄存器中的WPEN位(参见状态寄存器描述,在本数据手册的后面部分)设置为“1”,禁止写入状态寄存器。

HOLD:HOLD输入引脚用于暂停传输主机和CAT25640之间,无需重新传输整个序列在以后的时间。要暂停,HOLD必须是采取低和恢复它必须带回高,与两次转换期间SCK输入为低电平。什么时候不用暂停时,HOLD输入也应该与VCC相连直接或通过电阻器。

功能说明

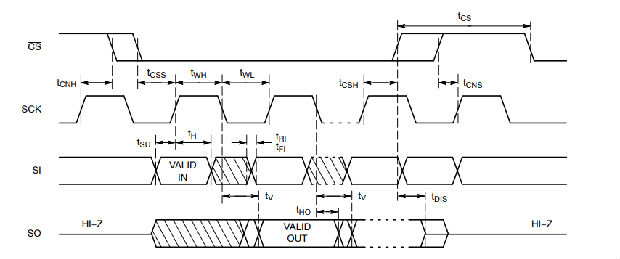

CAT25640器件支持串行外设接口(SPI)总线协议,模式(0,0)和(1,1)。该器件包含一个8位指令寄存器。指示表9列出了设置和相关的操作码。读取存储在CAT25640中的数据是通过以下方式完成的只需提供READ命令和地址即可。写入CAT25640,以及写入命令,地址和数据,也需要启用用于写入的设备首先设置状态中的某些位注册,将在后面解释。在CS输入引脚上经过高电平到低电平的转换后,CAT25640将接受六条指令中的任何一条表9中列出的操作码将忽略所有其他可能的操作码8位组合。通信协议如下图的时序。