AD9854点击型号即可查看芯片规格书

目录

| 1.信号源介绍 |

| 4.测试结果和分析 |

| 结语 |

为了实现高性价比、低相噪和低杂散的数字化信号源,本文提出了以直接数字频率合成芯片AD9854 为核心的设计方案。并详细论证了DSP、CPLD(comp

lex p rogramm ab le logic

device)、外部IO器件与AD9854相结合构成多功能信号源的硬件组成、功能扩展及其实现方法,还对输出信号的品质进行了详细分析,最后给出信号源样机的主要技术指标。

信号源是雷达、通信及其他电子系统不可缺少的重要组成部分。低相位噪声、高稳定度、高可靠性和多功能信号源的研究受到普遍重视。目前实现信号源的主要技术有: 直接频率合成、锁相式频率合成和直接数字频率合成DDS。DDS具有极高的频率分辨率、极快的频率切换速度、频率切换时相位连续、易于功能扩展和全数字化易于集成等优点。特别适合应用于信道间隔小、信道频率数多和相位噪声低的场合。文献[3~6]详细分析了DDS相位噪声对其本身输出波形品质的影响,指出相位噪声主要由累加相位截断、正弦表存储器有限字长、DAC有限分辨率和内部噪声等因素决定,DDS本身对相位噪声的影响可以忽略。

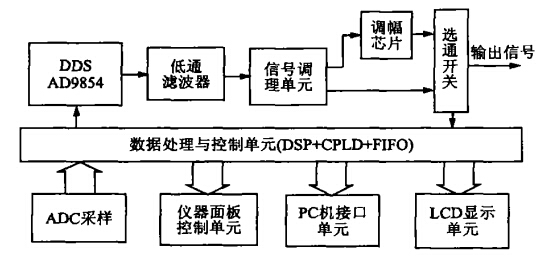

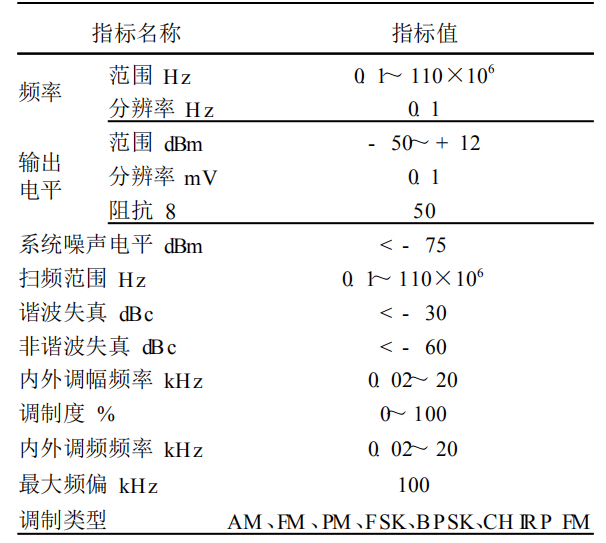

多功能信号源的硬件框图,如图1所示。系统由5个部分组成:数据处理与控制单元、DDS单元、模拟调制与数字调制单元、外调制信号采样单元和输入输出接口单元。信号源要达到的主要技术指标,如表1所示。

图1 信号源的总体结构框图

表1 信号源的主要技术指标

DDS单元是系统的核心,本系统使用的AD9854是最高工作时钟频率为300MHz,功能非常强大的直接数字频率合成器。一般情况下,DDS时钟频率的40%为实际输出波形的最高频率,AD9854时钟频率300MHz,则输出波形的最高频率可达120MHz。且根据参考文献[7]中对其各类参数的描述,符合信号源的性能要求,所以选择AD9854用于该信号源中。

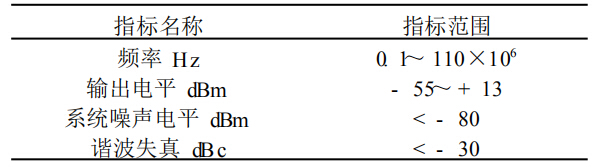

AD9854工作频率高,IO端口功能丰富,其内部功能框图如图2所示。主要特点如下:

图2 AD9854内部功能框图

(1)工作频率高达300MHz,片内有PLL(phase2locked loop ),可实现对参考频率4~20倍频,支持单端或差分时钟源。推荐使用差分时钟芯片产生差分时钟信号,再通过片内PLL倍频成300MHz。简化了时钟源的设计, 同时使低成本和低相位噪声的参考时钟源在技术上可行。

(2)双频率控制字,字长48位;双相位控制字,字长14位。当工作频率为300MHz时,频率分辨率为1×10- 6Hz, 频率转换时间最小值为6.7 ns。

(3)具有良好的动态性能。在100MHz时输出仍有80dB SDFR(无杂散动态范围)。

(4)具有简化的高速IO控制端口。10MHz的串行两线或三线接口,8位并行100MHz端口。本系统因为要实现多种调制功能,需要快速刷新DDS内部的频率、幅度和相位控制字,所以使用并行接口。

(5)2个300MHz高速12位DAC(digital2analoy converter),可以输出正交信号,可以方便应用于调制和解调系统中。2个DAC都是差分电流型输出, 都可以实现频率、幅度和相位的独立控制, 完成扫频、调制和O SK 等功能。

(6)内置高速比较器,配合片上2个DAC,可以单片产生扩展脉冲信号,且占空比可调。

(7)片内可选5种工作模式:单频、FSK、RAMPFSK、CHIPFM、BPSK。调制功能极其丰富,还可以配合片外芯片实现复杂的数字调制和模拟调制。

在图1中,键盘和LCD(liqw d crystal disp lay)构成人机交互的界面。用户由键盘输入参数,通过LCD显示。同时单片机将数据通过HPI口送DSP,在DSP中进行处理,然后将处理后的数据在CPLD的协调下由8位并行口送入AD9854中。AD9854输出频率0.1H z~110MHz的正弦波,此信号是差分电流形式,需由电阻网络转变为电压信号,再经过低通滤波器输出。为了使信号输出电平范围满足要求,还必须将信号送后级调理电路处理,经放大和衰减再通过射频传输器把差分信号耦合成单端信号,最后输出符合要求的正弦波信号。信号源的内调制是通过对调制波计算采样后,在CPLD+DSP控制下,由 FIFO循环送数至DDS中实现的。外调制是通过ADC采用外调制信号,DSP测量外调制信号的频率幅度, 再以内调制方式处理而实现的。内外调幅功能, 也可以通过乘法器AD835实现。数字调制功能由DSP+CPLD控制AD9854实现。

AD9854提供了串行和并行两种控制方式,为了满足丰富的调制功能,需要对芯片进行高速的复杂控制,所以使用8位并行控制方式是合理的。并行接口有8位数据线和6位地址线,内部寄存器共40个,地址范围00h~27h。其中1Dh~20h是控制寄存器,其他都是数据寄存器。系统仅要考虑对AD9854写操作,按照写时序关系,写数据进入片内缓冲寄存器中,然后只有当数据更新管脚(pin20)出现正脉冲后(芯片工作在外部数据更新模式),数据由缓冲寄存器装载至DDS核内。这时,DDS才以更新后的参数输出信号。以三角形自动线性扫频信号的产生为例,阐述对AD9854的操作步骤。

(1)复位DDS,即Master(pin71)保持10个以上系统时钟周期的正脉冲。

(2)写控制寄存器。设置工作模式、数据更新方式、锁相环倍频数、开启和屏蔽相应的功能。因为是三角形自动线性扫频,所以必须设置Triangle bit为高。

(3)写数据寄存器。写入扫频的起始频率和终止频率, 设置扫频步进和扫频斜率。

(4)数据设置完成后,在数据更新管脚产生正脉冲,芯片开始扫频,并不断以终频2初频2终频的方式循环。注意:扫频开始时可以在FSK data管脚(pin29)产生正脉冲, 以决定从终频还是从初频开始扫频。

AD 9854片内可选5 种基本工作模式, 利用芯片提供的功能模块, 配合DSP、CPLD和FIFO(first in first out) 可以实现功能扩展。

(1)数字调制

AD 9854 可以方便地实现二进制FSK和PSK。芯片提供了基带数据输入管脚(pin29),直接由该管脚的高低电平选择2个不同的频率和相位来实现FSK和PSK。M FSK M PSK的实现必须由用户根据数据符号宽度的定时控制多个频率或相位的切换。多种形式的扫频功能也是由片内硬件实现的,详细操作方法与§2.1中三角形扫频例子相同。

(2)模拟调制

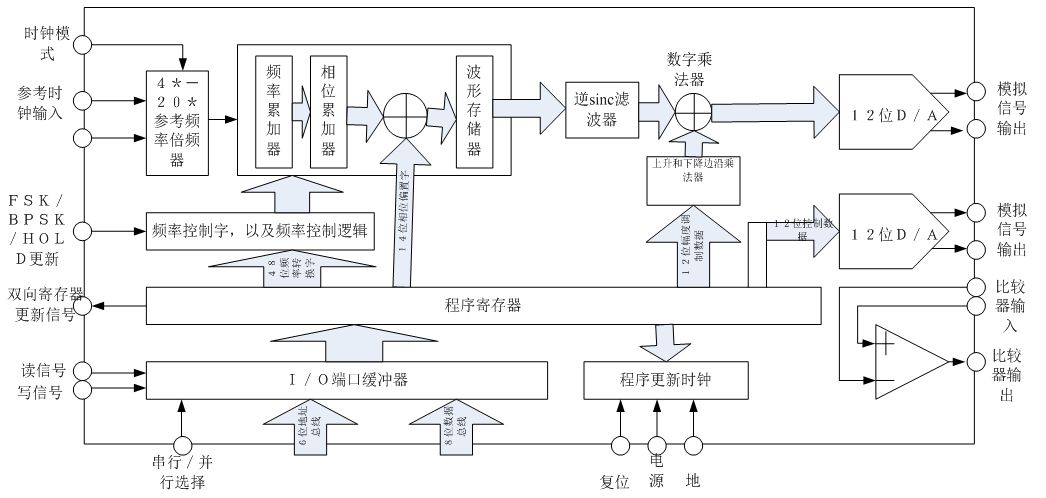

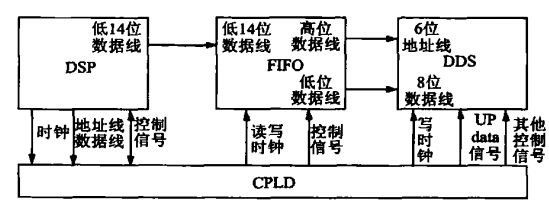

DSP通过对调幅波和调频波的计算量化,将频率字或幅度字按时序的先后关系依次存入FIFO中。在CPLD的作用下,FIFO不断循环地向DDS传送数据。如图3所示,DSP将地址线连接在CPLD上,通过CPLD中的逻辑关系确定FIFO在IO口上的地址。DSP的低14位数据线和FIFO低14位数据线相连,则DSP送FIFO的14位数据按低8位数据,高6位地址排列。所以FIFO低8位数据线连接DDS的并行口数据线,FIFO高6位数据线连接DDS的并行口地址线,按照CPLD提供的读写时钟信号传送数据。DSP的CL Kout引脚接CPLD的GCLK引脚,提供全局工作时钟。CPLD通过用户IO引脚为FIFO和DDS提供相同的读写时钟,实现器件间的时序同步。CPLD控制时序,不断将FIFO中的数据循环送入DDS中,按周期刷新UPdata管脚以完成模拟调试。模拟调制的关键是CPLD协调FIFO和DDS的时序。调频波和调幅波的频率可以设置,则其频率变化时,需要插入的等待周期就不同,即CPLD所控制的FIFO读时钟和DDS并行口写时钟都要随调制波频率的变化而变化。实现方法是DSP的数据线与地址线连接CPLD的IO口,在CPLD中设置一个计数值可变的计数器,计数器的输出端通过CPLD的IO口连接FIFO读时钟和DDS并行口写时钟。计数器的计数值就决定了输出时钟频率,这个值是DSP根据调制波频率计算后由IO寻址方式送入CPLD的。

图3 模拟调制的实现

(1)正交信号的产生

AD9854有2个高速DAC,输出信号的频率、幅度和相位都可以独立调节。只要使相位寄存器中预置值相差90°,则2路输出信号相位差为90°,正交信号便产生。这样信号源可为正交调制提供载波。

(2)脉宽可控的脉冲信号的产生

AD9854的I支路信号经低通滤波后作为内部高速比较器的负端输入信号,Q支路信号经低通滤波后,作为比较器的正端输入信号。通过设置DAC的输入改变比较电平,控制脉冲宽度的变化,脉冲信号的频率由频率控制字1确定。

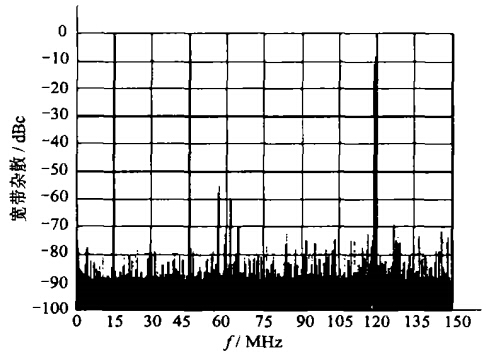

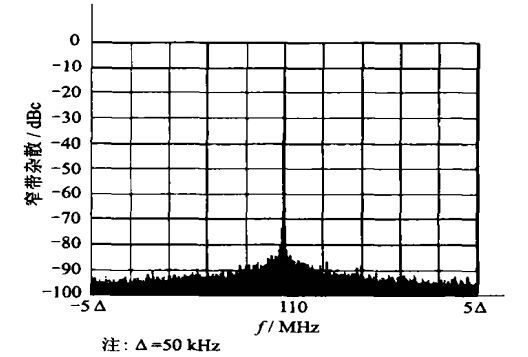

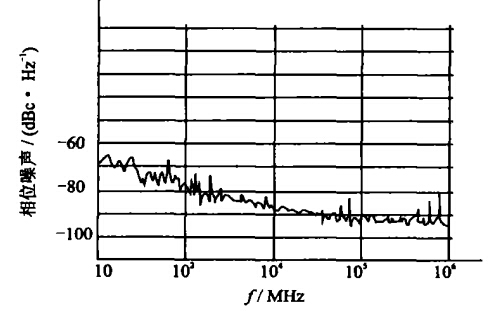

系统在确定了硬件结构后,精心设计硬件电路,完成系统调试和功能测试。测试样机达到的主要性能指标,如表2 所示。测试结果与表1中参数对比,可以看出信号源输出信号的频率、电平、噪声电平等主要性能指标完全达到要求。对整个频率范围内输出信号的杂散性能,使用了频谱分析仪A T 5011 进行测试,测试结果如图4~6所示。图4是输出110M H z波形的宽带杂散性能,其值优于40 dBc。图5是输出110 M H z 波形的窄带杂散性能,其值在±250 kH z范围内优于75 dBc。图6是输出110M H z 波形的相位噪声,测量得到在偏离中心频率1Hz处相位噪声为- 80 dBc H z,当偏 10 H z 时,相位噪声下降为- 60 dBc H z,之后随偏离频率变大,相位噪声逐渐减小。测试结果表明,主要技术指标达到性能要求,进一步在电源设计、隔离电路设计和低通滤波器设计等方面进行改进, 还可以减少相位噪声改善杂散性能。

表2 信号源样机测试的性能指标

图4 输出信号110M Hz 时的宽带杂散

图5 输出信号110M Hz 时的窄带杂散

图6 输出信号110M Hz 时的相位噪声

基于AD9854的多功能信号源能灵活、方便地实现多种模拟调制和数字调制。系统最大限度地挖掘了AD9854的潜力,将数字信号处理器、可编程逻辑器件和先进先出存储器与AD9854紧密结合, 输出正弦信号的最高频率为110M H z、谐波失真小于- 30 dBc。能够完成调幅、调频和频移键控等调制功能。并通过了分析和实际测试结果表明,以DDS为核心构造多功能信号源的有效途径。