目录

| 1.相变存储器 |

| 2.相变存储器芯片 |

| 结论 |

本文介绍设计了一种依靠电流驱动的驱动电路,整体电路由带隙基准电压源电路、偏置电流产生电路、电流镜电路及控制电路组成。该结构用于16 K以及1

Mb容量的相变存储器芯片的设计,并采用0.18 m标准 CMOS

工艺实现。该驱动电路通过Hpice仿真,表明带隙基准电压、偏置电流均具有较高的精度,取得了良好的仿真结果。

相变存储器(PC2RAM)是一种新型半导体存储器,在研发下一代高性能不挥发存储技术的激烈竞争中,PC2RAM在读写速度、读写次数、数据保持时间、单元面积、功耗等方面的诸多优势显示了极大的竞争力,得到了较快的发展。相变存储器是利用加工到纳米尺寸的相变材料在晶态与非晶态时不同的电阻状态来实现数据存储。读、写操作是通过施加电压或电流脉冲信号在相变存储单元上进行的。相变存储单元对驱动电路产生的驱动电压或电流十分敏感,因此,设计一个性能优良的驱动电路成为实现芯片功能的关键。

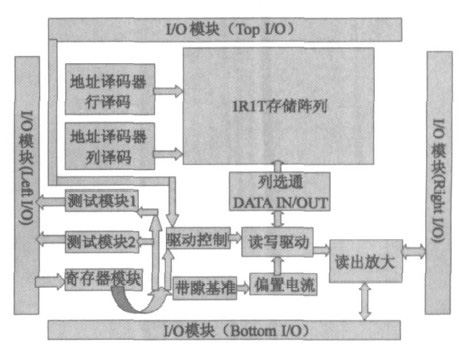

图1为相变存储器内部结构框图,主要包括相变存储单元阵列(1r1tarray)、地址解码器(rowdec和columndec)、读写驱动电路(drv8)、驱动控制电路(drvcon)和读出放大电路(sa8)。

图1 相变存储器芯片结构

相变存储单元阵列包括字线、位线和处在字线与位线的交叉区的相变存储单元,每一个存储单元包括一条字线、一个选通管及一个相变电阻,并且每一个相变电阻均可在非晶态与晶态之间进行编程;地址解码器解码输入行地址,以选择每个存储单元的字线,位选择电路根据输入的列地址,选择一条位线;驱动电路生成将所选存储单元编程为非晶态或晶态的写电流,以及读出被编程后的存储单元状态的读电流;驱动控制电路由控制逻辑与脉冲信号发生器组成,用于产生一定脉冲宽度的读/写脉冲,其中,写过程包括写“0”、写“1”两种情况(Set和Reset),对应相变单元在晶态(低阻)及非晶态(高阻)之间的转换。

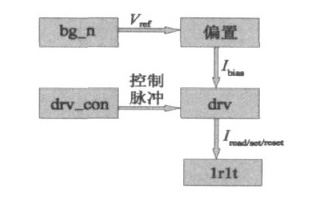

本文所设计的相变存储器驱动电路主要结构如图2所示。首先,由带隙基准电压电路bgn生成高精度的基准电压Vref,接着,该基准电压通过偏置电流产生电路偏置产生高精度的偏置电流Ibias,偏置电流输出给后级用于终驱动的电路drv。drv由两级电流镜电路组成,每有三个电流镜结构,可分别用于产生大小不同的Read、Set、Reset电流,drvcon用于控制产生所需的电流脉冲.

图2 驱动电路

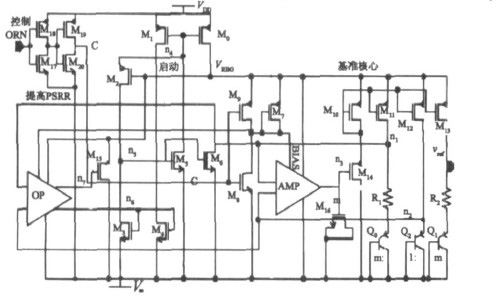

基准电压电路如图3所示,主要由控制电路、电路、提高电源抑制比(PSRR)电路及启动电路组成。该电路终可产生高精度的基准电压输出,在温度为-10~120℃时,具有613×10-6/℃的温度系数,在电源电压为310~316V变化时基准输出随电源电压变化仅为010101%/V,PSRR为69dB。

图3 基准电压电路

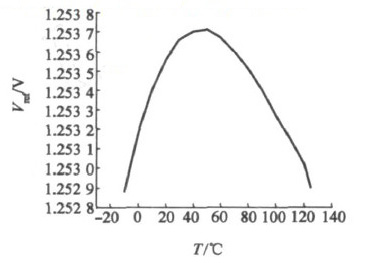

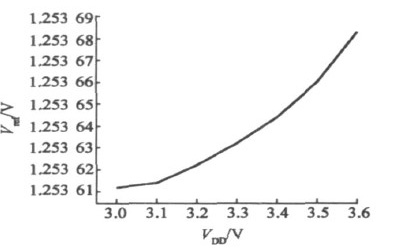

各种工艺偏差均较小,相对TT模型的偏差为01002311,是一种低温度系数,高电源抑制比的带隙基准电压源。图4和图5分别给出该带隙基准电压的温度特性曲线及电源抑制特性曲线。

图4 基准电压的温度特性曲线

图5 基准电压随电源电压变化曲线

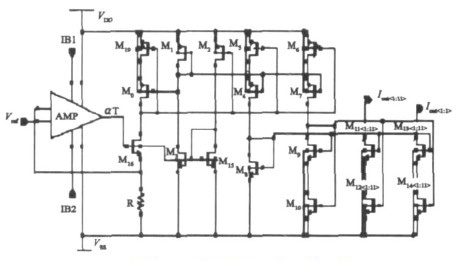

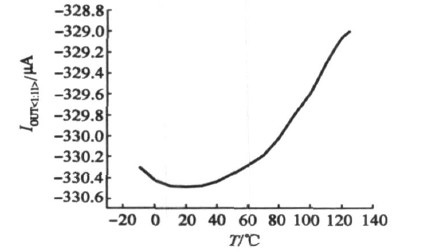

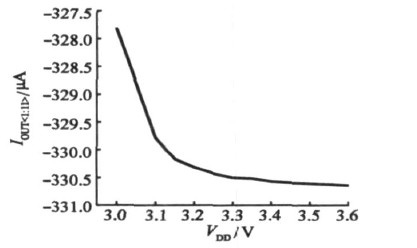

偏置电流产生电路如图6所示,其实现方法主要是通过差分运放的负反馈及电流镜的映射实现,通过前级电压输出给AMP一端,经负反馈电路得到AMP另一端输出电压等于Vref,该电压加在高精度电阻R上,得到一高精度的电流,经电流镜电路映射终得到两路电流输出IOUT1<1:11>,IOUT2<1:11>,其中,IOUT1用于后级驱动的电流镜电路所需的偏置,IOUT2则用于读出放大时所需的偏置。该两路电流均为高精度的。图7和8为电流的输出特性曲线。

图6 偏置电流产生电路

图7 偏置电流的温度特性曲线

图8 偏置电流的电源抑制特性曲线

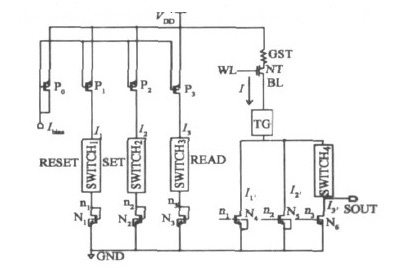

驱动电流的产生主要是根据电流镜的映射实现的,基本原理如图9所示。具体实施时,采用了两级电流镜结构,级为由NMOS管形成的电流镜,第二级为由PMOS管形成的电流镜。由基准电流源电路产生的基准电流,通过两级映射后产生的电流终耦合至位线,加到相变单元上。该两级电流镜电路,终产生用于Set、Reset和Read的大小不同的驱动电流,且在级电流镜电路与第二级电流镜电路间加入控制开关SWITCH1、SWITCH2和SWITCH3,这些控制开关的打开与关闭由驱动控制电路部分发出的脉冲信号进行控制,使加到相变单元上的脉冲信号具有一定脉宽与脉高,实现Set、Reset和Read操作。

图9 驱动电流镜电路

进行写操作时,以Reset为例,需要施加一个短而强的电压或电流脉冲,电能转变成热能,使相变材料的温度升高到熔化温度以上,经快速冷却,可以使多晶的长程有序遭到破坏,从而实现由多晶向非晶的转化,低阻变为高阻。首先通过解码电路输出的高电平将选通管NT打开,随后通过驱动控制电路将SWITCH1打开,而SWITCH2和SWITCH3此时则处于关闭状态,这样,由PMOS管P0和P1形成的电流镜,产生一定大小的并且一定倍数于基准电流IOUT1的电流I1。同样的,由NMOS管N1和N4形成的电流镜将I1再次镜像得到所需的Reset电流I1’,I1’通过打开的传输门TG及打开的选通管NT施加到相变单元中的相变材料上,从而使相变材料发生相变,SWTICH1的时序决定了所施加的Reset电流脉冲的宽度,要求是一个较短的脉冲,比较典型的数值一般小于50nm。

Set时,需要施加一个长且强度中等的电压或电流脉冲,相变材料的温度升高到结晶温度以上、熔化温度以下,并保持一定的时间(一般大于50ns),使相变材料由非晶转化为多晶,高阻变为低阻。具体实施时,SWITCH1和SWITCH3关闭,SWITCH2打开,通过由PMOS管P0、P2和NMOS管N2、N5形成的两级电流镜产生所需的Set电流I2’,施加到相变单元中的相变材料上,使相变材料发生由非晶态到晶态的转换,SWITCH2的时序决定了所施加的Set电流脉冲宽度。要求是一个稍长的脉冲,比较典型的数值一般大于100nm。

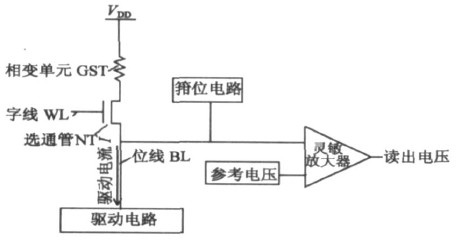

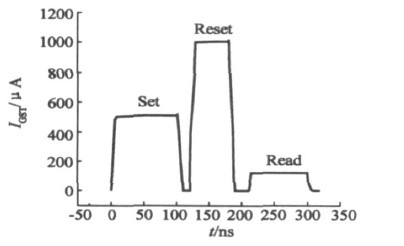

Read操作时,开关SWITCH4打开,传输门TG打开,电流镜中SWITCH1、SWITCH2关闭,SWITCH3打开,通过PMOS管P0、P3和NMOS管N3、N6形成的两级电流镜产生读电流I3’,施加到相变单元GST上,该读电流是足够小的,产生的热能保证相变材料的温度始终低于结晶温度,材料不发生相变。读出的实质是读出相变单元上的电压情况,由其电压看电阻情况。该电压由端口SOUT输出,与某一参考电压经过灵敏放大器被比较放大读出,晶态与非晶态时的读出电压是可以严格区分开的。图10为读出放大电路示意图。图11为终加到相变单元上的电流脉冲信号,具体脉宽可通过脉冲信号发生器进行调节。

图10 读出放大电路示意图

图11 驱动电流脉冲

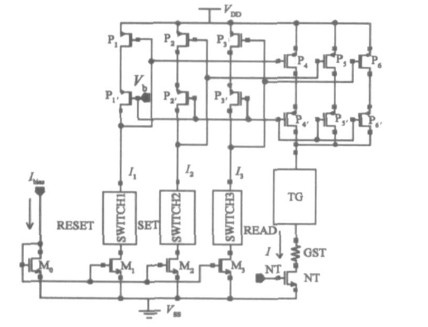

考虑如图12所示的电流镜,该结构采用共源共栅的改进结构,可得到更的驱动电流,并且将选通管源端接地(不同于图10中的情况:选通管的衬偏效应限制了能流过相变单元的电流,故其尺寸需要设计的较大些),图12中选通管的衬偏效应得以消除,可仅用较小的选通管尺寸得到相同的效果,这种结构将在1Mb容量的PC2RAM芯片中得以运用。

图12 改进的电路镜电路

以上就是基于相变存储器的驱动电路设计与实现方法。仿真表明,基准电压、偏置电流具有良好的精度,整个16KbPCRAM芯片采用SMIC0118μmCMOS工艺实现,测试进一步验证了仿真结果,表明该驱动电路具有良好的驱动能力。