目录

| 1.引脚接法 |

有源晶振是晶振中的一类,有4只引脚,是一个完整的振荡器,里面除了石英晶体外,还有晶体管和阻容元件。有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使有源晶振用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。下面将介绍其的引脚接法以及EMC设计:

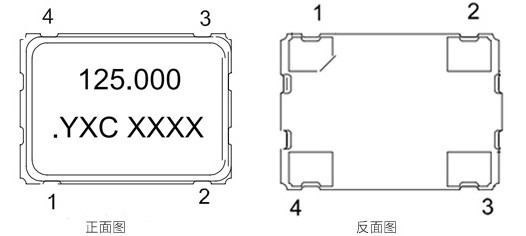

有源晶振一般有4个脚,有个点标记的为1脚,按逆时针(管脚向下)分别为2、3、4。通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

有源晶振正反面

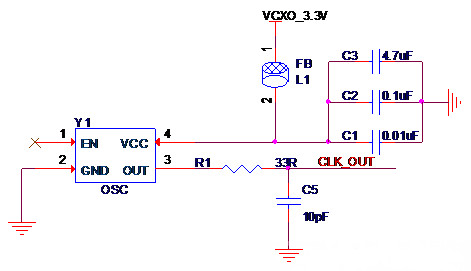

有源晶振EMC标准设计电路如下:

电路原理图

(1) 有源晶振的电源引脚最好不要直接接电源,而是通过一个磁珠后接入,这可大大降低电源噪声对时钟输出频率的影响。晶振电源的去耦电容的匹配也很重要,去耦电容一般选3个,容值依次递减。

(2) 有源晶振的时钟输出端串联一个小电阻,作用是为了减少信号反射,以免造成信号反射引起的信号过冲。电阻R1是预留匹配设计,可根据实验情况进行阻值调整。其具体作用如下:

①可以减少谐波。有源晶振的输出是方波,当阻抗严重不匹配的时候将引起谐波干扰。加上串联电阻后,该电阻与输入电容构成RC电路,将方波变成正弦波。

②可以进行阻抗匹配,减少反射信号的干扰。

(3) C5是预留设计,可根据实验情况进行调整,它的作用是:与串联电阻组成RC滤波电路,减少时钟信号的过冲。

(1) 耦合电容应尽量靠近晶振的电源引脚,位置摆放顺序:按电源流入方向,依容值从大到小依次摆放,容值最小的电容最靠近电源引脚。

(2) 晶振的外壳必须接地,可以晶振的向外辐射,也可以屏蔽外来信号对晶振的干扰。

(3) 晶振下面不要布线,保证完全铺地,同时在晶振的300mil范围内不要布线,这样可以防止晶振干扰其他布线、器件和层的性能。

(4) 晶振不要放置在PCB板的边缘,在板卡设计时尤其注意该点。

以上就是有源晶振的EMC设计介绍了,对于时序要求敏感的应用,可以选用比较精密的晶振,甚至是高档的温度补偿晶振。有些DSP内部没有起振电路,只能使用有源的晶振。有源晶振通常体积较大,许多有源晶振是表贴的,体积和晶体相当,有的甚至比许多晶体还要小。