目录

| 1.系统总体设计 |

| 2.视频数字图像采集 |

| 3.视频图像数据处理 |

| 4.视频图像的VGA显示 |

| 总结 |

随着近几年低成本的FPGA不断推陈出新,利用EDA工具对FPGA芯片进行多样性设计,已经成为电子设计的通用平台,并逐步向支持系统级设计的方向发展。与专用集成电路相比,FPGA芯片具有快速的定制性和高灵活性,扩展性强,作为一个平台,FPGA显然已经非常适合于高性能低成本的视频和图像处理,尤其在图像分辨率和帧率要求比较高的场合,如:天气预报、资源探测、导弹的精确制导、战场的动态分析等,仅用高性能DSP或者专用视频处理芯片均无法获得令人满意的效果。目前较有代表性的方案有两种:

一种是在中央控制器的总调度下,采用两片或者多片视频处理芯片并行处理视频数据;另一种是整个视频处理系统由视频采集和压缩两个子系统共同完成视频处理。本系统采用第二种方案,提出了一种基于FPGA实现的视频显示系统,该系统能接收与ITU-R BT.656标准兼容的YCrCb 4:2:2视频数据,并将接收到的视频图像显示到VGA显示器上。

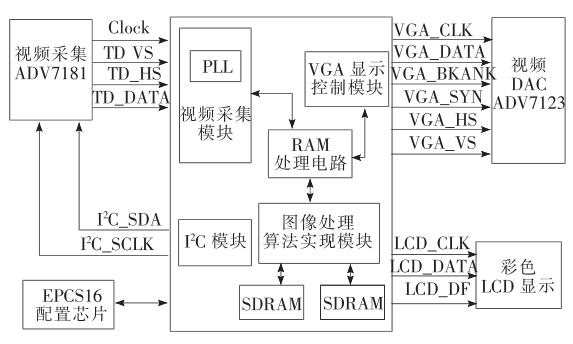

基于FPGA实现的视频显示系统整体结构框图如图1所示。系统主要分为:视频采集模块、PLL锁相环时钟管理模块、I2C总线模块、RAM视频数据处理模块和VGA显示控制模块。系统上电后,FPGA首先从EPCS16中读取配置数据,完成自身程序加载,随后通过I2C总线完成对视频解码芯器ADV7180的配置。配置完成后,ADV7180将采集到的模拟视频数据转换成ITU-RBT.656标准的YCrCb 视频数据及图像时钟送入FPGA进行处理,并将处理后的图像数据存储在RAM中,同时视频控制模块读取存放在RAM中的视频图像数据,按照VGA显示时序要求将视频图像数据和控制信号送入D/A芯片ADV7123,实现VGA显示。

图1 系统硬件结构框图

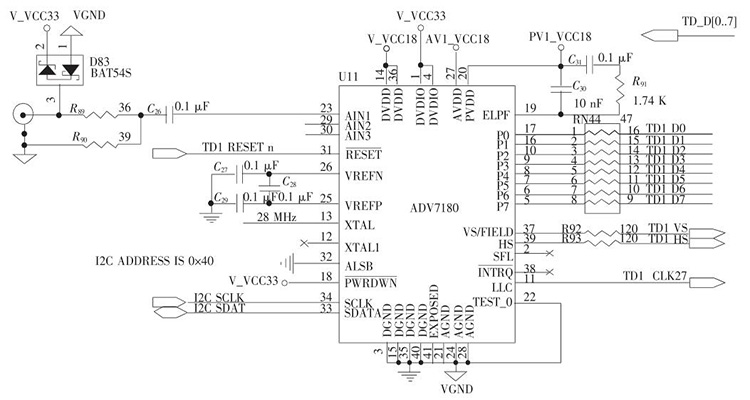

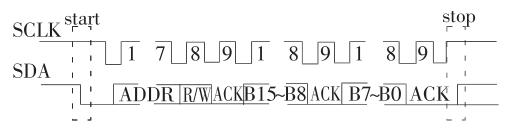

选用AD公司的ADV7180作为视频采集解码芯片,图2为ADV718视频解码电路原理图。ADV7180的数字输出8位或16位的、与ITU-R BT.656标准兼容的YCrCb 4:2:2视频数据。将ADV7180配置数据存储在查找表LUT_DATA中,通过SCLK、SDA两根串行线,调用I2C控制器模块读/写ADV7180的寄存器,完成对ADV7180的配置。I2C控制器使用33个I2C时钟周期完成1次传输24位数据,第一个时钟周期用于初始化控制器,第2、3个周期用于启动传输,第4~30个周期用于传输数据(其中包含24位数据和3个ACK),最后3个时钟周期用以停止传输。在开始传输之前和停止传输之后,I2C_SCLK信号保持高电平,I2C的起始条件(START)与终止条件(STOP)由I2C_SCLK与I2C_SDA配合完成,I2C总线的时序如图3所示。

图2 视频解码电路原理图

图3 I2C总线时序图

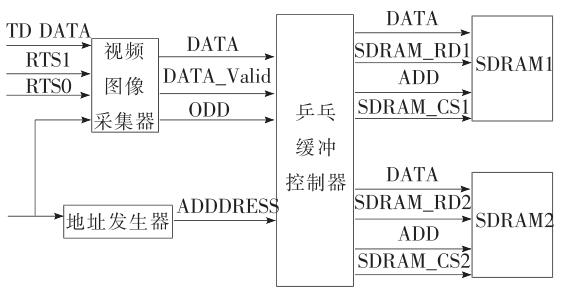

ADV7180数字输出的是ITU-R BT.656标准的串行YCrCb4:2:2视频数据,还包括水平同步TD_HS、垂直同步TD_VS、行锁定时钟LLC及场同步等信号,经串并转换、YCrCb 4:2:2视频数据插值、解交织处理、色度空间转换等后续处理,转换成RGB数据,接下来把每一幅图像数据存储到一个SDRAM中供后续显示。本设计中视频数据存储主要由视频存储控制器和两片同等大小独立编址的SDRAM(64MB)使用乒乓机制交替完成。

视频存储控制器主要由视频图像采集器、地址发生器和乒乓缓冲控制器组成,图4为其逻辑结构图。LLC为时钟信号,RTS为复位信号,地址发生器用一个计数器来实现,视频图像采集器接收来自ADV7180输出的TD_DATA,处理后输出奇偶信号ODD,“0”为奇数场,“1”为偶数场。当RTS有效同时LLC处于上升沿时,图像数据有效,DATA_Valid为数据有效信号。

图4 存储控制器逻辑结构框图

乒乓缓冲控制器控制SDRAM的读写操作,通过控制读写信号与片选信号实现两片SDRAM交替读写。当SDRAM1接收视频采集模块采集的视频数据时,SDRAM2用于视频输出,当新的一帧图像采集完成后,两块SDRAM角色互换。读操作时SDRAM_RD1与SDRAM_CS1有效表示选中SDRAM1,同样SDRAM _ RD2与SDRAM_CS2有效表示选中SDRAM2。写操作时写信号有效。乒乓操作的最大特点就是将经过缓存的数据流无时间停顿地传送到输出端,因此非常适合对时序不连续的像素进行无缝缓冲处理。

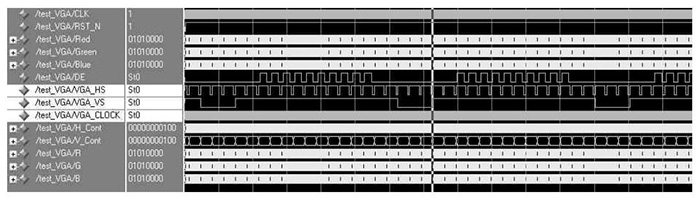

根据VGA显示的基本时序设计显示控制模块,用于产生VGA所需的RGB数据信号和控制信号,VGA显示控制模块的输入频率为25MHz,由系统时钟分频得到,根据输入时钟,显示控制模块可以产生VGA所需的控制信号,包括行同步、场同步和复合消隐信号等。输出像素则与输入像素相同,因此,只要对VGA控制芯片ADV7123的HSYNC和VSYNS接口产生符合要求的水平同步信号和垂直同步信号,然后在相应的时间内把要显示的数据的像素值传送到R、G、B端口,就可以实现对应的图像显示。ModelSim仿真结果如图5所示。

图5 VGA显示时序仿真图

系统外接输出NTSC制式的DVD视频信号源,上电后通过VGA接口在显示器上显示的实物图如图6所示,显示效果良好。

图6 显示器显示实物图

以上就是基于FPGA的视频显示系统设计介绍了。该系统大幅减少了电路板的尺寸,节约了成本,同时增加了设计的灵活性和系统的可靠性,充分应用了FPGA快速并行处理数据的特性,在产生同步信号的同时送出像素数据,解决了嵌入式系统实时图像显示的问题,扩展了应用范围。