目录

| 1.数字集成电路设计 |

| 小结 |

如今是数字化的社会,在很多领域都用上了数字集成电路,如信息高速公路、多媒体电脑数字电视等等。而且数字集成电路也在不断更新换代,由早期的电子管、晶体管、小规模集成电路(几一几十门)、中规模集成电路(几十门~几百门)、大规模集成电路(几百门一几千门)发展到超大规模集成电路(几万门以上)以及具有特定功能的专用集成电路(ASIC)芯片。本文介绍了数字集成电路设计的发展趋势,以及分析了VHDL的特点,再结合实例介绍VHDL在数字集成电路设计中的应用。

数字集成电路设计涉及对电子器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的创建。所有的器件和互连线都需安置在一块半导体衬底材料之上,这些组件通过半导体器件制造工艺(例如光刻等)安置在单一的硅衬底上,从而形成电路。对于数字集成电路来说,设计人员现在更多的是站在高级抽象层面,即寄存器传输级甚至更高的系统级(有人也称之为行为级),使用硬件描述语言或高级建模语言来描述电路的逻辑、时序功能,而逻辑综合可以自动将寄存器传输级的硬件描述语言转换为逻辑门级的网表。对于简单的电路,设计人员也可以用硬件描述语言直接描述逻辑门和触发器之间的连接情况。

VHDL主要用于描述数字系统的结构、行为、功能和接口。除了含有许多方面具有硬件特征的语句外,VHDL的语言形式和描述风格与句法十分类似一般的计算机高级语言。VHDL的程序结构特点是将-项工程设计或设计实体(可以是一个元件、一个电路模块或一个系统)分成外部(即端口)和内部(即设计实体的内部功能和算法完成部分)。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其它的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。具体特点如下:

(1)与其它的硬件描述语言相比,VHDL具有更强的行为描述能力,决定了它成为系统设计领域最佳的硬件描述语言。

(2)VHDL丰富的仿真语言和库函数,在大规模集成电路设计的早期就能查验出设计系统的功能可行性,可随时对设计进行功能仿真、时序仿真,在设计初期就可以对整个工程设计的可行性作出决策,缩短了设计周期,减少了研发成本。

(3)VHDL语句的行为描述能力和程序结构具有支持大规模集成电路设计的分解和对已有设计的再利用功能。重复利用他人的IP(Intelli-gence Property core)模块和软核(soft core)是VHDL的特色,在更高的层次上把IP模块利用起来,能达到事半功倍的效果。

(4)对于VHDL完成的一个确定设计,可以利用EDA工具(如MAX+PLUS)进行逻辑综合和优化,并自动把VHDL描述设计转换成门级网表。这种设计方式突破了传统门级设计中的瓶颈,极大地减少了电路设计的时间和错误发生率,降低了开发成本,缩短了设计周期。

(5)VHDL对设计的描述具有相对的独立性,设计者可以不懂硬件的结构,也不必关心最终设计的目标器件是什么而进行独立的设计。正因为VHDL的硬件描述与具体的工艺和硬件结构无关,VHDL设计程序的硬件实现目标器件有广阔的选择范围。

(6)由于VHDL具有类属描述语句和子程序调用等功能,对于已完成的设计,在不改变源程序的前提下,只需改变类属参数或函数,就能改变设计的规模和结构。

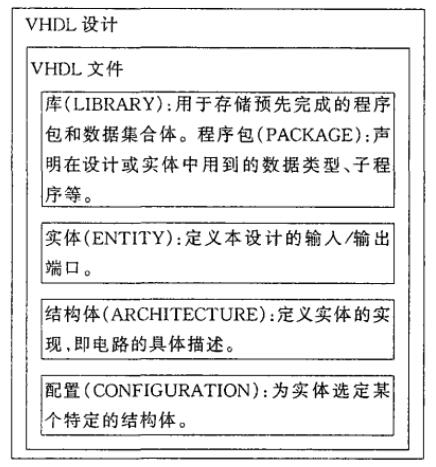

一个相对完整的VHDL设计由以下几个部分组成:(1)库﹑程序包;(2)实体;(3)结构体;(4)配置;其各自作用如图1所示:

图1 VHDL程序结构框图

以上四个部分并不是每个VHDL程序都必须具备的,其中只有一个实体和一个与之对应的结构体是必须的。

Altera公司的MAX + PLUS ( Multiple ar-ray matrix and programmable logic user system)开发系统是一个完全集成化、易学易用的可编程逻辑设计环境,它可以在多种平台上运行。它所提供的灵活性和高效性是无可比拟的,具有丰富的图形界面,辅之以完整的、即时访问的在线文档,使设计者能够轻松的使用MAX + PLUSⅡ软件包设计数字集成电路。

(1)开放的界面

MAX + PLUSⅡ软件可以与其它工业标准的设计输入。综合与校验工具相连接。

(2)与结构无关

MAX+ PLUSⅡ系统的核心Compiler支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX5000和 Classic可编程器件,提供了真正与结构无关的可编程设计环境。

(3)多平台

MAX+ PLUS软件可基于486、奔腾PC的Windows NT3.51或4.0、Windows95、98下运行,也可在Sun SPAC station,HP 9000 Se-ries7007800和 IBM RISC System/6000工作站上运行。

(4)完全集成化

MAX+ PLUSl软件的设计输人、处理与校验功能全部集成在统一的开发环境下,这样可以加快动态调试、缩短设计周期。

(5)丰富的设计库

MAX+ PLUSⅡ提供了丰富的库单元,其中包括74系列的全部器件和多种特殊的逻辑宏功能(Macro-Function)以及参数化的兆功能(Mage-Function)供设计者调用,大大减轻了设计者的工作量,缩短了设计周期。

(6)模块化工具

设计者可以从各种设计输入。处理和校验选项中进行选择从而使设计环境用户化,必要时,还可以根据需要添加新功能。

(7)支持多种硬件描述语言

'MAX +.PLUSⅡ软件支持多种硬件描述语言设计输人选项,包括VHDL、Verilog HDL和AHDL语言。

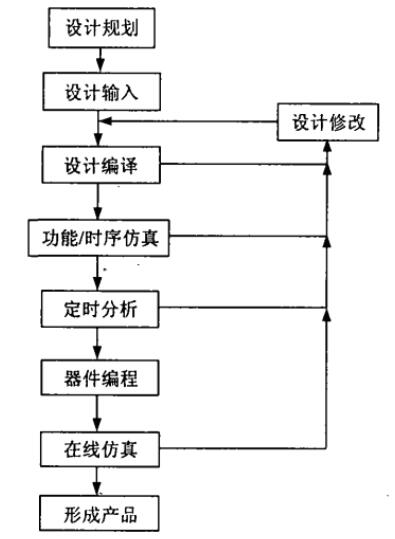

设计流程如图2所示:

图2基于MAX+ PLUSⅡ的数字系统设计流程图

(1)设计输入:设计输人就是设计者对逻辑器件的逻辑功能描述。设计输入通常采用图形输入和VHDL文本输人方式。

(2)项目编辑:为完成设计的处理,MAX +PLUSI提供了一个完全集成的编译器(Compil-er) ,可直接完成从网表提取到最后编程文件的生成。在编译过程中生成一系列标准文件可进行时序模拟、适配等。

(3)项目校验:完成对设计的功能、时序仿真;进行时序分析、寄存器性能分析。

(4)项目编程:将设计的项目下载/配置到所选择的器件中。

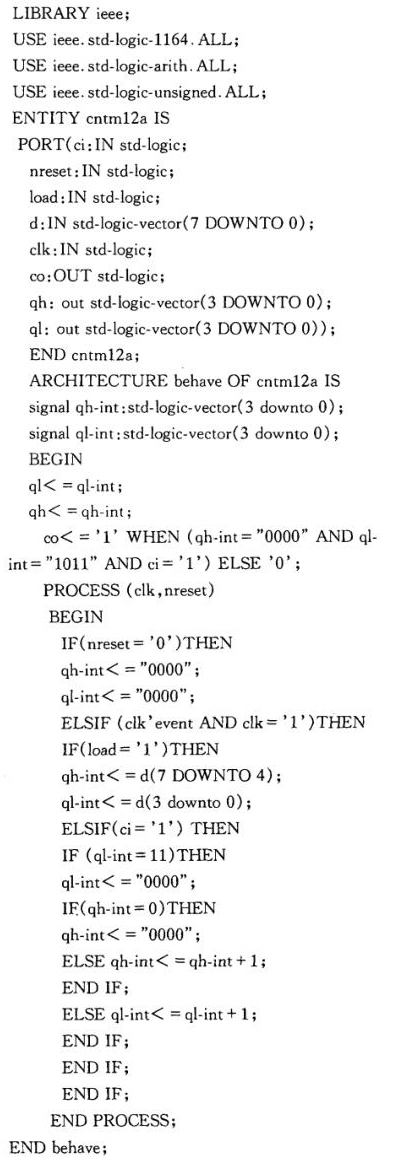

在数字集成电路中,计数器的应用十分普遍。计数器是一种对输入脉冲进行计数的时序电路。按其进位制可分为二进制计数、十进制计数和任意进制计数;按其功能又分为加法计数器﹑减法计数器和加/减可逆计数器等。在传统的计数器电路中,采用74161/1627163及相应的外围电路来构成所需的计数器;如果要构造非规则进制的计数器,则需添加更多的外围器件,若用VHDL语言来构造就方便的多了。下面以模为12的加法计数器为例来说明VHDL在数字电路设计中的应用。

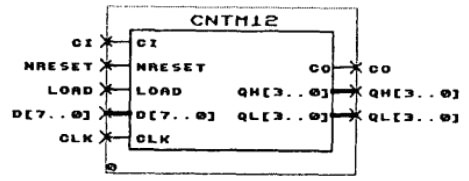

模为‘12’的计数器采用加法计数器,且具有数据加载、置位功能,输入端口为ci(进位)、nrest(置零)、load(加载),d(数据输入)、clk(时钟);输出端口设计为co(输出进位)、qh(高位输出)、ql(低位输出)。

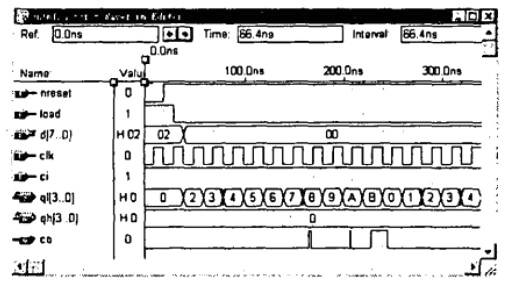

仿真结果如图3所示:

图3模‘12'计数器仿真波形图

仿真结果说明:

(1)预加载值‘2’在‘ load'信号有效时装载,输出ql从‘2’开始计数,计到‘B'(十进制的‘11 '),'co'输出高电平(约16ns),计数器置位,从‘0'开始计数,如此循环;

(2)计数器在CP脉冲的上升沿翻转;

(3)预加载值可以在仿真时随时更换;

(4)‘co'在计数值为‘8'和‘A'处各出现一个“毛次”,是由‘0111'(7)到‘1000'(8)及‘1001'(9)到‘1010'(10)翻转过程中,因各触发器速度不一致,造成中间短时出现‘1011'(B)过渡状态所致。这是二进制编码的先天不足,也是采用Gray(格雷码)的主要原因。

此计数器设计实体对应的电路原理图符号如图4所示:

图4 电路原理图符号

此实例模为‘12',只要在原程序的基础上稍加修改,可实现任意进制的加法计数器、减法计数器或可逆计数器。还可以作为库文件被其它设计所调用。

以上就是基于VHDL的数字集成电路设计应用介绍了。本文以基于VHDL的计数器的设计为例介绍了VHDL在数字集成电路设计中的应用,体现了VHDL语言的‘魅力'。随着CPLD/FPGA器件的广泛应用,EDA技术的发展,数字系统的设计变得象软件设计一样灵活,极大地改变了传统的数字系统的设计方法、过程和观念。