目录

| 1.系统整体设计 |

| 3.系统软件设计形成 |

| 4.关于数字电位器的常见问题 |

| 结语 |

电位器在电力和电子学的最早期就已经是一个重要的无源电路组件。电位器是一种三端子设备,带有一个可访问的电阻元件,可通过旋转轴上用户可设置的滑动臂实现分压功能。电位器已用于无数的模拟和混合信号电路,能满足各种各样的应用要求。全电子数字电位器仿真了机电式电位器的功能,但这是通过一个没有活动部件的集成电路来实现的。数字电位器可接受多种格式的数字代码,并确立一个相应的电阻值。因此,这种器件有时被称为电阻式数模转换器(RDAC)。在传统电位器中,可以用手(有时甚至是小型电机)来设定滑臂位置,以此设置分压比。然而,在数字电位器中,计算机控制器通过数字接口与数字电位器IC连接,并建立一个与滑臂位置等效的数值。

数字电位器可代替机械式电位器,具有使用灵活、调节精度高、无触点、低噪声等显著优点。由于某型检测系统是用于某有线通信线路的在线检测,这类线路通过二线差分方式可传输多类通信信号,其标称电平峰值范围为0.8~9V,频率范围为50~2.5MHz,匹配阻抗为120Ω、600Ω,其在检测过程中无法预先知道传输信号类型;因而本文运用数字电位器可编程控制阻值功能,设计了增益可自适应调整的数据采集系统,可以较好地解决了这一问题。

数据采集系统,通常由信号调理电路﹑模数转换器(ADC)电路和信号传输电路3部分组成。信号调理电路主要完成阻抗匹配﹑信号幅度调节和滤波;ADC主要完成模拟信号到数字信号的转换;信号传输电路主要用于将ADC输出的数字信号传送到上位机,并从上位机获取控制信号完成采集系统的功能控制。

依据前文所述,为完成对信号的采集,采集系统的设计指标应略有富余:输入阻抗大于6MΩ,输入信号幅值范围大于0.5~10V,电路频率范围大于30~3MHz。

在数据采集系统中,ADC芯片是核心,整个电路设计应当围绕ADC芯片展开,所以首先要完成ADC芯片的选型工作。根据采样定理,为得到完整的信号信息,采样频率只需大于信号最大频率的2倍即可,而在工程实践中,通常选择采样频率为信号最大频率的5~10倍,这就要求系统中数模转换电路的采样频率应大于20MHz。按照功能性和经济性的原则,ADC芯片选择ADS822,其主要参数为:分辨率为10位;采样速率为40MSPS;动态输人范围为2V;信噪比(SNR)为60dB;无动态失真范围(SFDR)为72dBFS;微分非线性误差(DNL)为0.5LSB;可选择单端或差分输入;+5V单电源供电。

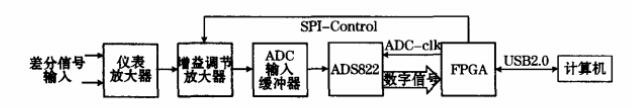

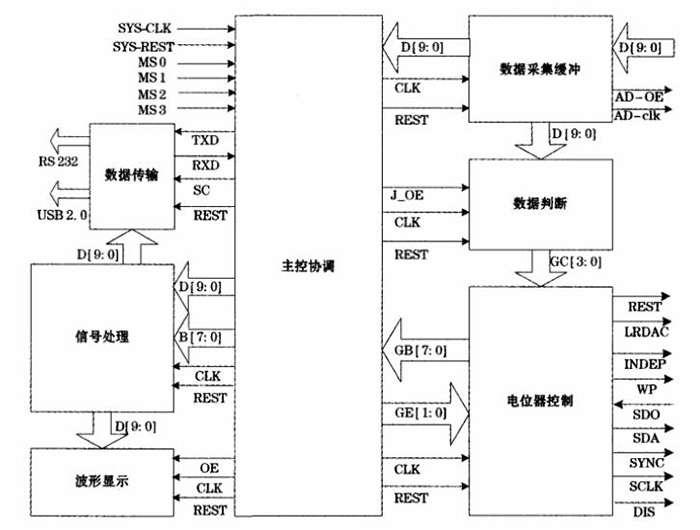

图1是数据采集系统结构框图,信号调理电路由仪表放大器、增益调节放大器、ADC输入缓冲放大器组成。仪表放大器的主要功能是提供高输入阻抗(通常可以达到109~1012Ω),用于提高电路共模抑制比和完成差分输入到单端输出的转换。增益调节放大器用于完成信号增益控制,以匹配ADC的输人范围。ADC输入缓冲器配合ADC使用,用于隔绝前后级电路的干扰,同时完成ADC单端信号的输入调整。模数转换器(ADC)电路以ADC芯片为核心组成,用于完成模拟信号到数字信号的转换。信息传输电路以FPGA芯片为核心组成,用于为ADC提供采样时钟,读取ADC输出数字信号,进行初步信号处理,将数据传送到上位机,并通过SPI控制线对增益调节放大器进行控制。

图1 数据采集系统结构框图

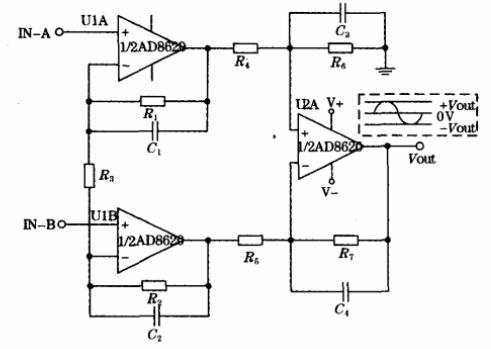

仪表放大器是一种具有差分输入和相对参考端单端输出的闭环增益单元。通常由3个运放组成,图2是仪表放大器原理图,U1A、U1B组成差分放大电路,为同相差分输入方式,用于提高电路的输入阻抗,减少电路对小信号的衰减,同时该电路只对差分信号进行放大,而共模信号只起跟随作用,其对差分信号的增益G=1+(R1+R2)/R3。U2A为减法器电路,用于完成差分信号到单端信号的转换,当R4=R5,R6=R7时,其增益G=R6/R4。图2所示仪表放大器的总增益为2。R1与C1,R2与C2,R6与C3,R7与C4,分别组成一阶低通滤波器,能够抑制放大器噪声,同时可防止电路产生高频自激。

图2 三运放组成仪表放大器

运放芯片选择双通道集成芯片AD8620,该芯片为高精度的JFET输人放大器,其供电电源为±5V或±13V,使用±13V供电时其性能参数为:最大输入失调电压:150μV;最大输入偏置电流:±10pA;最大输入失调电流:±10pA;输入电压范围:-10.5~+10.5V;最小共模抑制比(CMRR):90dB;输出电压范围典型值:-11.84~+11.84V;输出短路电流:±65mA。

增益调节放大器电路主要对输入信号幅值进行衰减或放大,根据系统技术指标和ADC芯片的技术参数,信号调理电路的增益范围应当大于0.2~4,由于仪表放大器的增益为2,所以该电路的增益调节范围应当大于0.1~2。目前很多公司已经生产了可编程增益放大器(PGA)来完成增益调节的功能,已有的产品虽然使用方便,但是PGA大部分用于小信号放大电路中,其增益大于1。因而该电路选择集成运放芯片和数字电位器来完成信号增益调节功能。

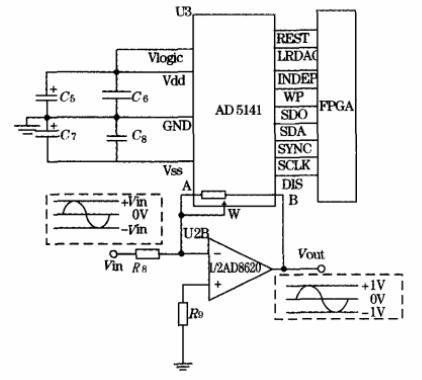

数据采集系统增益放大器用于输入ADC信号的增益控制。如图3所示,增益调节放大器电路由AD8620芯片的另一个运放和一个数字电位器芯片AD5141组成。AD5141芯片为单通道,10kΩ,100kΩ可选数字电位器,控制方式SPI、可选,256个游标位置,其主要性能参数为:最大电阻容差:8%,10kΩ带宽:3MHz,A、B、W端允许通过电流值范围:-6~+6mA。

图3 增益放大器电路

数字电位器W端和B端的阻值为RBW,其调节范围为40~10kΩ,步进值39.23Ω,运放芯片应用为反相放大器,其增益G=-RBW/R8,R8=5kΩ时,该电路增益调节范围0.008~2。R9为匹配电阻,通常选择R9=RBW/R8,在这里由于R,BW是可变,因此选择R0=2kΩ。

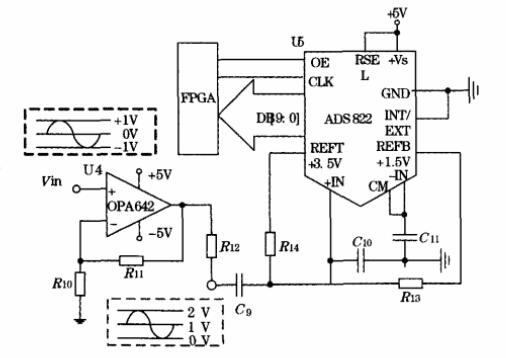

仪表放大器输出的信号经过增益调节放大器后,调整为2Vp-p信号,传送到ADC输入缓冲器中。图4为ADC输入缓冲器和ADC工作电路。ADS822工作在单端输入状态时,其输入信号范围为0~2V,因而从增益调节放大器过来的信号不能直接送到ADC的输入端,需要增加一个输入缓冲器,将信号范围调节成0~2V,图4中的U4组成电路即为ADC输入缓冲器,该电路是依据ADS822的使用手册提供参考电路设计。

图4 输入缓冲器与ADC电路

数据采集系统的软件主要是完成系统控制﹑数字信号处理和信号传输等功能,通过FPGA芯片XC3S400来完成。FPGA芯片为ADC电路提供时钟,读取ADC输出数据,并对通过对数据大小的分析,判断ADC的输入信号幅值范围,如果信号幅值过大或者过小,就通过输出控制信号调节数字电位RBW器大小来改变增益调节放大器的增益,使输入ADC的信号幅值保持在ADC工作的最佳范围之内。FPGA同时可对接收到的数字信号进行处理,将处理后的数据通过USB2.0接口传输到上位机。

图5 软件设计结构

系统软件基于ISE环境开发,采用模块化设计,其设计结构如图5所示,依据功能不同整个软件可以分为以下7个模块:

(1)主控协调模块,用于接收控制端输入的工作模式和控制信息,完成整个系统功能的控制,并为数据在FPGA内部传输提供通道,同时向各个模块提供时钟和复位信号。

(2)数据采集模块,用于控制ADC芯片工作,为ADC芯片提供采样时钟,读取ADC芯片输出的数字信号,采用FIFO方式对数据进行缓冲,并将数据传送到主控协调模块和数据判断模块。

(3)数据判断模块,主控单元通过JOE控制该模块是否工作,该模块工作时用于分析、判断ADC的输入信号幅值范围,并将判断结果转换为增益控制信号传送到电位器控制模块。

(4)电位器控制模块,接收主控协调单元的输出的工作状态控制信号,可工作于3种固定增益方式或增益自适应方式。3种固定增益方式应用于能够确定信号类型得场合。工作在增益自适应方式时,通过接收数据判断模块输出的控制信号,转换成相应的数字电位器控制信号输出,调节数字电位器RBW变化。

(5)信号处理模块,用于补偿因为采集系统增益造成的数据变化,将ADC采集到的数据还原成输入系统的数据,并可依据应用需要,进行部分运算量大、运算实时性要求高的数字信号处理,并将最终处理结果传送到数据传输模块和波形显示模块。

(6)数据传输模块,用于采集系统与上位机的通信,完成上位机控制信号的接收和采集系统数据的发送。该模块分为两部分,一部分是RS232接口,用于低速控制信号的接收,一部分是USB2.0接口,用于高速数据的传输。

(7)波形显示模块,用于将信号处理模块传输来的数据转换为可以用显示器显示的波形信号,并输出到显示器显示,可用于数据采集系统的采集状态监测,在主控协调单元的使能信号下工作。

4.1数字电位器的用途是什么?

数字电位器(也称为电阻式数模转换器,或非正式的数字电位器)是一种模拟电位器模拟功能的数字控制电子元件。它通常用于微控制器微调和缩放模拟信号。

4.2数字电位器是如何工作的?

数字电位器(也称为数字电阻器)具有与普通电位器相同的功能,但与普通电位器相比,数字电位器使用数字信号和开关代替机械动作。任何时候都只关闭一个开关,闭合的开关决定了“雨刷”的位置和电阻比。

4.3数字电位器的电阻容差是多少?

数字电位器往往具有大的的端到端公差。Maxim数字电位器通常具有20%至30%的电阻容差。当数字电位器用作与其他电阻器串联的分压器时,电阻容差可能会出现问题。

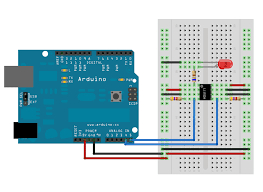

4.4如何将数字电位器连接到Arduino?

将数字电位器的时钟引脚(SCL)的引脚4连接到Arduino上的模拟引脚5,将数据线(SDA)的引脚5连接到模拟引脚4。在SCL和SDA线上,添加4.7K欧姆拉上电阻,将两条线连接到+5V。最后,将LED连接到引脚1,即AD5171的“雨刷器”,串联一个680欧姆LED。

图6 数字电位器连接到Arduino

以上就是基于数字电位器的增益自适应数据采集系统设计介绍了。数字电位器是一种数字设置的IC,在许多系统结构和电路设计中取代了经典的机电式电位器。数字电位器不仅减少了产品尺寸和因意外移动而出错的可能性,而且还增加了与处理器的兼容性,从而增加了软件的兼容性,还具有更高的精度和分辨率(如果需要)以及其它的有用功能。本文通过分析论证,给出了完整的硬件设计电路和软件设计结构,经过仿真,系统符合设计要求,可为类似的数据采集系统设计提供参考借鉴。