TM4C1294NCPDT 点击型号查看芯片规格书

Texas Instruments(德州仪器) 芯片规格书大全

作者:Brian Wang

TM4C129x系列是TI 推出的通用MCU 产品,该产品具有120Mhz Cortex M4F核,最大1MB的Flash 空间以及灵活多样的通信接口。同时该产品的内置Ethernet PHY,可支持高集成度、低成本的以太网通信。片上丰富的资源使其非常适合作为储能等新能源应用的House Keeping MCU 来使用,配合TI 的BMS采样AFE及实时控制芯片C2000共同完成储能系统所需要的采集、监控、控制等一些列功能。

近年来,随着储能等新能源应用的飞速发展,各类行业标准不断发展和健全,对储能系统的安全性也提出了越来越高的要求。而作为储能系统的控制中枢,对于MCU 在故障状态下的安全也提出了新的要求。例如IEC60730最先对家储产品提出当MCU 晶振失效,系统需要能够安全地断电, 这就需要MCU 必须具有一种可靠地检测、诊断和处理MCU 晶振失效的措施。本文就将以储能系统的这一需求为例,介绍如何在TM4C129X中应对系统晶振失效的问题。

1. TM4C129X晶振失效检测功能

TM4C129X 系列MCU中本身提供了主时钟诊断功能,该功能将主时钟(MOSC)频率与内部晶振频率对比,一旦发现主时钟频率异常则触发以下异常中的一种, 并自动切换到内部晶振 (PIOSC)来继续为MCU的后续运行提供是时钟源。

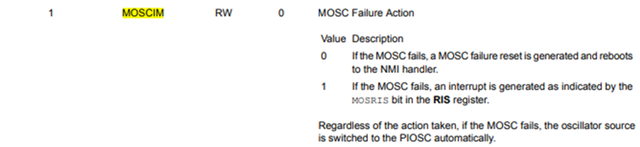

图-1 主晶振失效动作选择配置

针对本文中所讨论的安全下电需求,我们可以配置MOSCCTL.MOSCIM=0从而实现晶振异常时触发MOSC Fail 中断,并在中断中进行相关的安全下电操作,具体的配置实现代码如下:

ui32MOSCCTL = HWREG(SYSCTL_MOSCCTL);

// Enable MOSC verification enable MOSC fail interrupt

SysCtlMOSCConfigSet(ui32MOSCCTL | SYSCTL_MOSC_VALIDATE | SYSCTL_MOSC_INTERRUPT);

// Enable MOSC interrupt at SYS level

HWREG(SYSCTL_IMC) = 0x08;

// Enable SYS interrupt at NVIC level

IntEnable(INT_SYSCTL);

void SystemtHandler(void)

{

// Add error handling code here

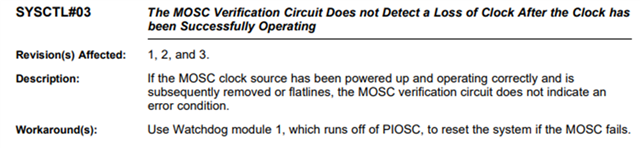

该方法可以在不增加额外外围电路的情况下实现晶振失效状态下MCU的安全状态处理,但需要注意的时在TM4C129X系列的Errata中有注明该系列芯片的MOSC verification 电路存在一定的无法准确检测晶振失效的风险。因此该方法仅能用作一种辅助手段,或应用在对于诊断率要求 不高的应用当中。我们必须增加其他解决问题的措施。

图-2 TM4C129X 晶振检测功能勘误

2. 使用硬件方式应对晶振失效

在储能系统中,为了应对TMC129X内置时钟诊断可能存在的风险,我们可以增加额外的硬件电路来实现更加可靠的错误处理。对于此类问题,常见的解决方案的是使用一颗额外的看门狗(Watchdog)芯片。

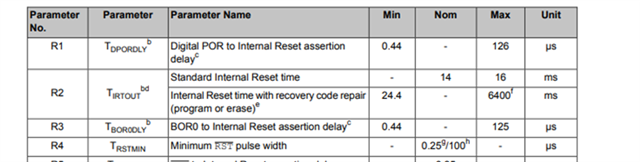

对于TM4C129X系列芯片,通过其数据手册可以芯片最小复位脉冲宽度在0.25~100us,绝大多数的TI 看门系列产品均可满足此时间要求:

图-3 TM4C1294 复位时序要求

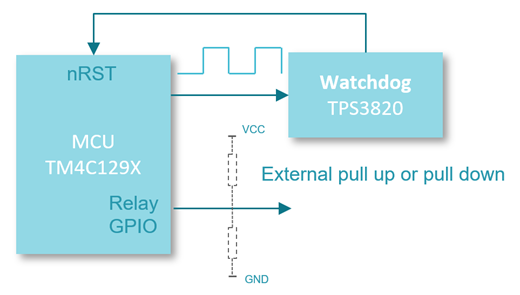

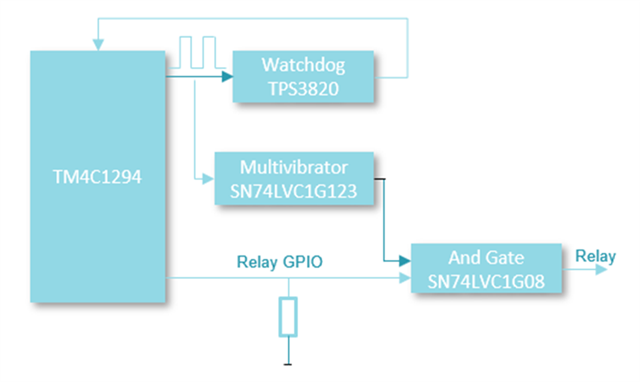

在此选择TI TPS3820 为例说明看门狗方案:

图-4 TM4C1294 看门狗方案示意图

正常工作状态下,TM4C129X通过PWM 以固定频率对TPS3820进行喂狗。当晶振失效,若TM4C1294 晶振内部的晶振失效诊断电路生效,按照预先设计好的程序执行断电保护。若内部电路不失效,则芯片将失去时钟源停止喂狗,25ms后TPS3820将向TM4C129X发送复位脉冲,通过nRST引脚将芯片复位。

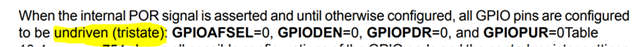

当TM4C129X 复位,则所有GPIO将被复位到高阻状态(tristate),此时引脚电平将有外部的上拉或下拉电阻决定。因此只需要按照安全状态在继电器控制I/O端口的外围增加相应的上拉或下拉电阻即可保证复位后GPIO处于安全状态。

图-5 TM4C1294 GPIO默认状态

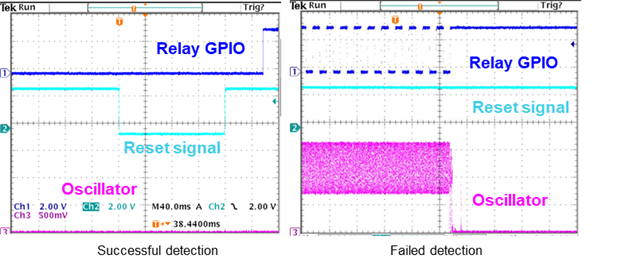

经过对该方案的深入测试,在内部检测电路不工作的情况下,该硬件复位方案有极高的成功率(如图6左)。但在小概率下,我们可以抓到如图6 右侧的失败情况。在该种情况下,晶振下电后芯片没有发生复位,继电器控制I/O 也没有如预想被拉低,芯片似乎“卡死”在了某种状态里。

图-6 测试波形

针对此问题对硬件的看门狗方案进行了改进,在原有看门狗的基础上增加了个一个单稳态触发器和一个与门,当MCU 晶振失效MCU 停止喂狗,1G123通过与门拉低继电器控制信号,保证在MCU 无法复位的情况下仍能断开继电器。

图-7 改进的硬件看门狗方案示意图

3. TM4C晶振失效复位失败的解决方法

上一节中,我们通过增加片外的复位和I/O口控制电路保证了芯片晶振失效时I/O口能够处在安全状态,但并未解决TM4C无法正确复位的问题。

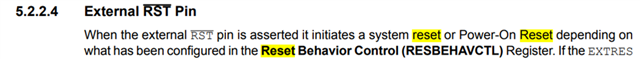

该问题的主要原因是TM4C在接收到nRST 复位脉冲时可以触发两种不同的复位模式:

Power on Reset(POR): 该模式又称为冷复位(code-reset),此复位模式等同于芯片上电复位,是一种完全彻底的复位方式;

System Reset: 该模式又称为暖复位(warm-reset),此模式只复位芯片的核心及部分外设,不是完全复位。

经过反复多次测试,TM4C在外部晶振失效的情况下只能可靠的地进行system reset,而无法支持 POR Reset。默认状态下,nRST均触发POR Reset,因此会出现上一节类似MCU ‘卡死‘的异常状态。需要通过Reset Behavior Control寄存器将复位模式改为System reset 即可正常复位。

图-8 TM4C129X RST脚复位模式选择

使用如下API 进行配置:

1

SysCtlResetBehaviorSet (SYSCTL_RESBEHAVCTL_EXTRES_SYSRST);

重复上述实验,无论如何测试,在晶振失效情况下收到TPS3820的复位触发信号后TPS3820均可正常复位,GPIO按照预设置高。

图-9更改复位模式后的测试波形

4. 总结

本文以储能系统为例,介绍了如何在TM4C129x系列芯片的使用过程中应对晶振失效故障。针对芯片本身功能存在的不足,本文通过增加外围电路解决增加了“双保险”,大大提高了TM4C129X芯片在晶振失效情况下的可靠性。

参考文献

[1] Texas Instruments: Tiva TM4C1294NCPDT Microcontroller DATA SHEET

[2] Texas Instruments: Tiva C Series TM4C129x Microcontrollers Silicon Revisions 1, 2, & 3 Errata (Rev. G)