特征

•RGB的三个2:1和4:1多路复用器

•内部设定增益-1

•高速三态输出(HIZ)

•断电模式(启用)

•锁存启用(EL4340)

•±5V操作

•±870 V/微秒转换速率

•500MHz带宽

•典型供电电流为10mA/ch(EL4340)和15.3mA/ch(EL4342)

•无铅(符合RoHS)

应用

•HDTV/DTV模拟输入

•视频投影仪

•计算机显示器

•机顶盒

•安全视频

•广播视频设备

500MHz三重多路放大器

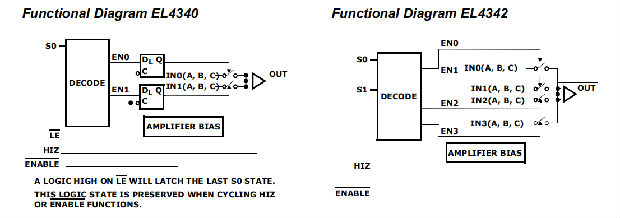

EL4340和EL4342是固定单位增益多路放大器,具有高转换速率和视频交换的出色带宽。这些设备具有高阻抗输出状态(HIZ),使多个设备的输出连接在一起。电源关闭模式(ENABLE)用于关闭电源敏感应用中不需要的电路。当启动引脚拉高,设置EL4340,EL4342进入待机功率模式-仅消耗18兆瓦。EL4340中的一个附加功能是锁存启用功能(LE),允许使用公共逻辑总线进行独立逻辑控制。

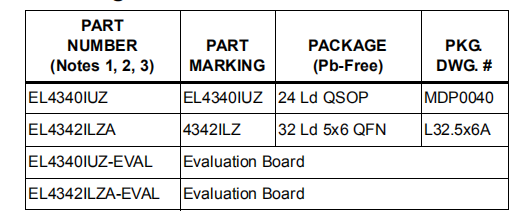

订购信息

笔记:

1、 为磁带和卷盘添加“-T13”或“-T7”后缀。卷盘规格详见TB347。

2、 这些Intersil无铅塑料包装产品采用特殊的无铅材料组、模塑料/模具连接材料和100%哑光镀锡板加退火(e3端接处理,符合RoHS标准,并与SnPb和无铅焊接操作兼容)。Intersil无铅产品在满足或满足无铅峰值回流焊温度时被归类为MSL超过IPC/JEDEC J STD-020的无铅要求。

3、 有关湿度灵敏度水平(MSL),请参见EL4340和EL4342的设备信息页。

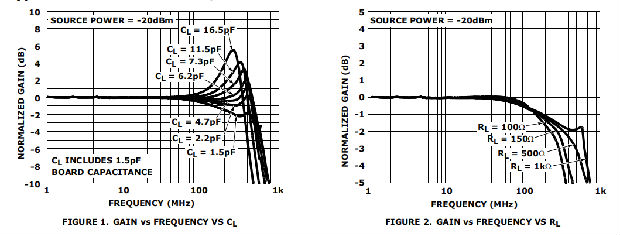

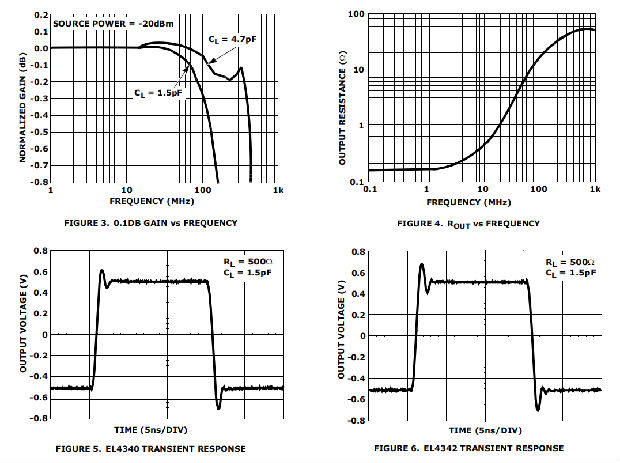

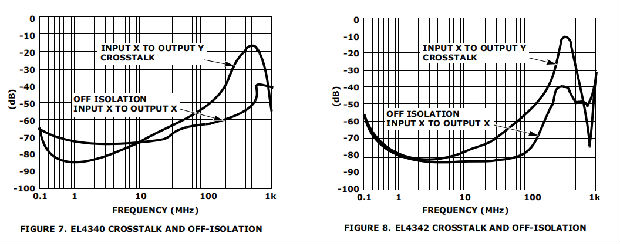

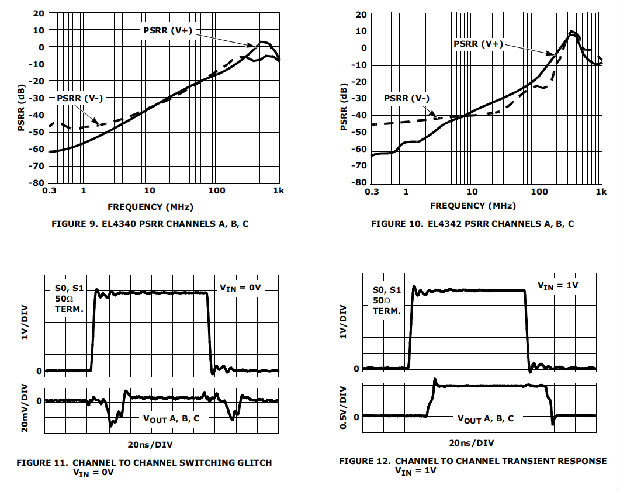

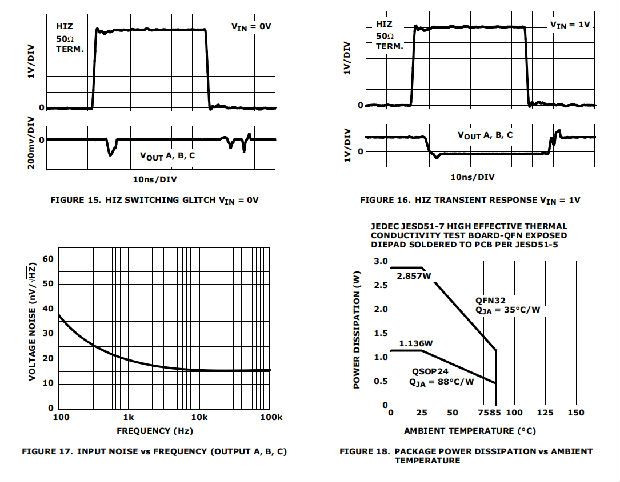

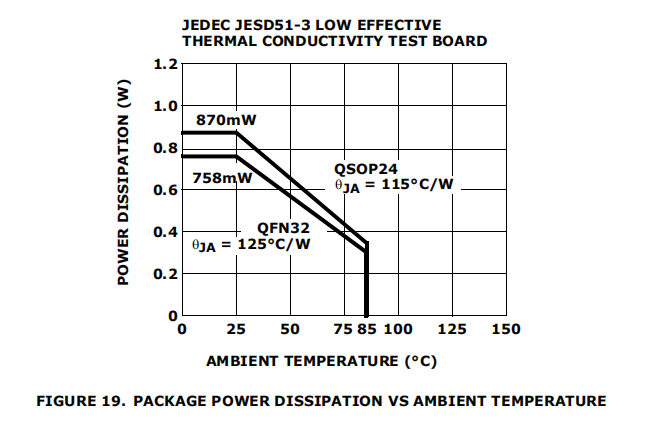

除非另有规定,否则典型性能曲线VS=±5V,RL=500Ω至GND,TA=+25°C。

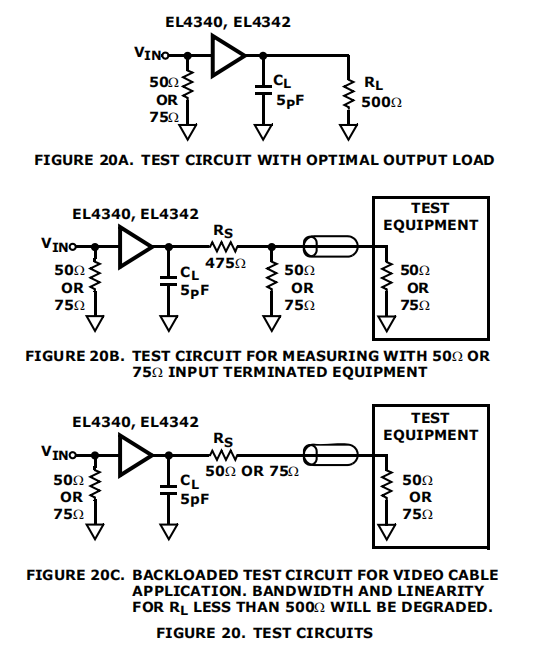

交流测试电路

图20A说明了测试交流性能的最佳输出负载。图20B说明了连接到50Ω输入端接设备时的最佳输出负载。

应用程序信息

总则

EL4340、EL4342三倍2:1和4:1毫安是理想的作为高性能交换机的矩阵元素路由器。关键特性包括缓冲高阻抗模拟输入和输出负载下卓越的交流性能低至150Ω,用于视频电缆驱动。单位增益电流反馈输出放大器稳定地工作在电容性负载和带宽在5pF与500Ω并联。总输出电容可以在印刷电路板电容和外部负载之间分开电容器。

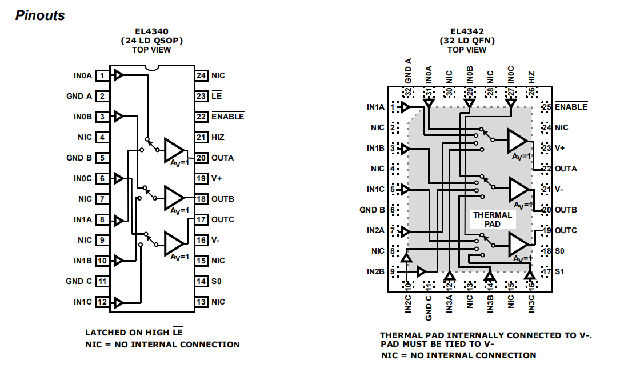

接地连接

为了获得最佳的隔离和串扰抑制,所有的GND管脚和NIC管脚必须连接到GND平面。

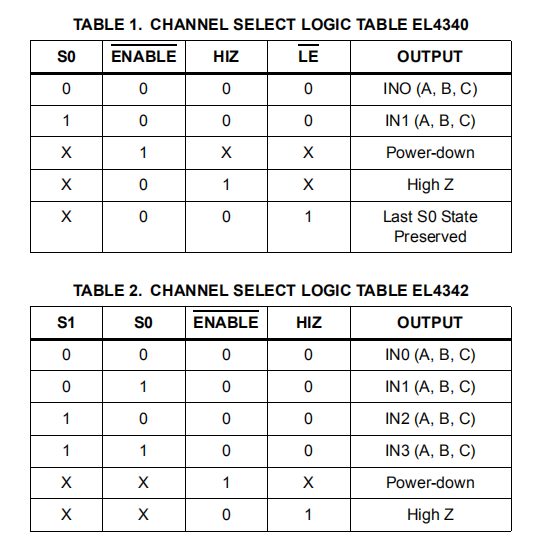

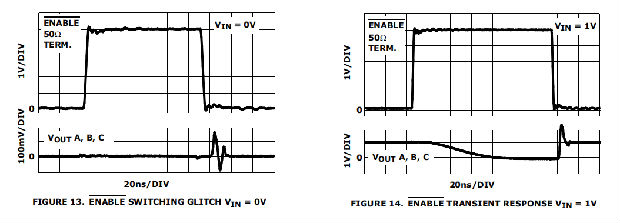

控制信号

S0,S1,ENABLE,LE,HIZ-这些是二进制编码的,TTL/CMOS兼容控制输入。S0,S1引脚选择输入。三个放大器同时切换从他们各自的投入。ENABLE,LE,HIZ引脚是用于禁用部件以节省电源,在最后一个逻辑中锁定状态和三状态输出放大器,分别。为了控制信号升降时间小于10ns使用靠近部件的终端电阻将使瞬变最小化耦合到输出。

通电注意事项

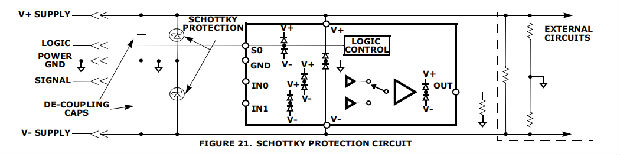

ESD保护电路使用来自所有管脚的内部二极管V+和V-供应。另外,一个dV/dT触发的钳位器连接在V+和V-管脚之间,如引脚说明的等效电路1至4部分桌子。dV/dT触发的钳位施加最大值电源接通转换率为1V/微秒。损坏电流可电源上升率超过1V/微秒的流量,如就像热插拔一样。在这些条件下,附加应采取措施确保增长率超过。

必须考虑权力的顺序

适用于V+和V-管脚,以及模拟和逻辑输入引脚。肖特基二极管(摩托罗拉MBR0550T或等效)从V+接地和V-接地(图21)将分流损坏电流内部V+和V-ESD二极管+在V型电源之前向设备供电。

如果对逻辑或模拟视频施加正电压输入引脚在V+施加之前,电流将流过内部ESD二极管到V+引脚。大人物的存在去耦电容器及其它电路的负载效应连接到V+,可能导致通过装置内的ESD二极管和其他有源电路。因此,数字和需要模拟输入以防止在这段时间内损坏这些输入端的电压比V+更正。

希兹州

一个内部下拉电阻器确保设备在没有连接到HIZ引脚的情况下激活。通过在HIZ引脚上放置一个逻辑高(>2V),在大约15ns内建立HIZ状态(图16)。如果选择了HIZ状态,则输出为高阻抗1.4MΩ,约为1.5pF与输出的10μa偏置电流并联。当多个mux共享一个公共输出时使用此状态。

在HIZ状态下,输出为三个状态,即使在高转换率的情况下也保持其高Z。此状态下的电源电流与激活状态相同。

启用和关机状态

启用引脚处于低激活状态。内部下拉电阻器确保设备在没有连接到启用pin。断电状态在如果逻辑高(>2V)为放置在启用管脚上。在断电状态下输出无泄漏,但具有较大的可变电容(约为15pF),并能向后驱动。在这种情况下,大的输入摆率会导致几十毫安的故障电流。不要将此状态用作高当多个MUX安培共享相同的输出线。

LE State

EL4340配备有锁闩启用销。逻辑LE引脚上的高(>2V)锁定最后一个逻辑状态。这个循环HIZ或ENABLE时保留逻辑状态功能。

限制输出电流

这些部件不存在输出短路电流限制。全部应用程序需要将输出电流限制在小于50毫安。零件的热沉也足够必修的。

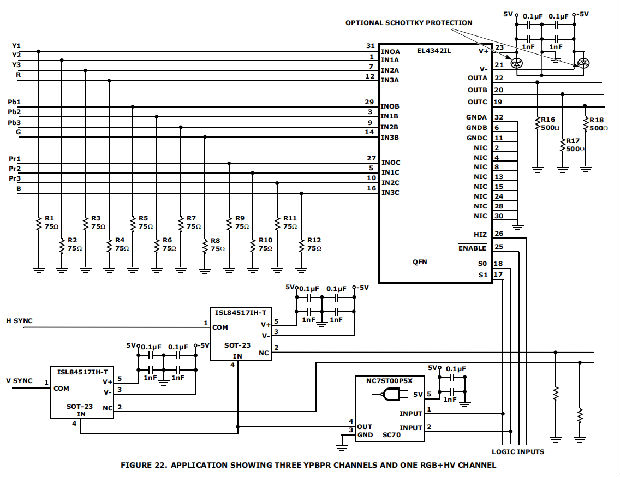

应用实例

图22说明了EL4342的使用,两个ISL84517SPST交换机和一个NC7ST00P5X NAND门到mux 3不同分量视频信号和一个RGB视频信号。SPDT开关为RGB视频并断开部件信号。

PC板布局

该电路的交流性能在很大程度上取决于在设计PC板时要小心。以下是达到最佳高频的建议PC板的性能。

•使用低电感元件,如芯片强烈建议使用电阻器和片式电容器。

•最小化信号跟踪长度。跟踪电感和电容很容易限制电路性能。避免尖角,尽可能使用圆角。过孔在信号线中增加高频电感应该避免。大于1“的PCB记录道开始显示信号上升/下降时的传输线特性小于等于1ns的次数。高频性能可能是对于大于1英寸的痕迹降级,除非带状线使用。

•匹配通道通道模拟I/O跟踪长度和布局对称。这将最小化传播延迟不匹配。

•最大限度地利用交流去耦PCB层。所有信号输入/输出线路应在连续的地平面上布线(即这些线下没有分割平面或PCB间隙)。避免过孔在信号输入/输出线路中。

•使用适当的终端电阻值和位置。终端电阻应尽可能靠近设备可能的。

•测试时使用高质量的连接器和电缆,匹配电缆类型并将电缆长度保持在最少。

•至少2个电源去耦电容器建议(1000pF,0.01μF)尽可能靠近设备尽可能避免盖和设备之间的通孔因为过孔会增加不需要的电感。更大的盖子可以再远一点。当布局中需要过孔时应尽可能远离设备。

•NIC管脚位于输入管脚的两侧。这些销没有内部连接到模具。它是建议将这些插脚绑在地上,以尽量减少相声。

QFN包需要额外的PCB布局

热垫规范

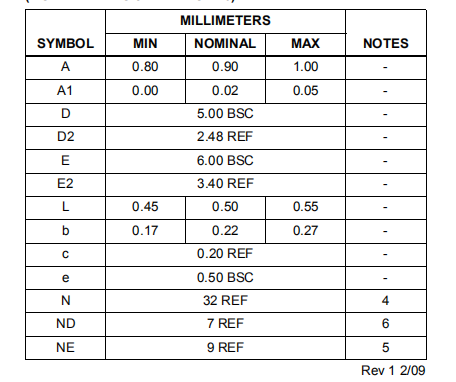

热垫与V电源电连接通过高阻IC基板。它的主要功能为集成电路提供散热。但是,因为通过基板连接到V电源热垫必须与V电源连接,以防止不需要的电流流向热垫。别系这个别针接地,因为这可能导致大的反向偏压电流在GND和V-之间流动。EL4342使用这个包衬垫尺寸D2=2.48mm,E2=3.4mm。

如果热垫连接到多层中的专用去耦合层PC板。如果无法使用专用层,在较高的频率下,交流性能可能会降低。

热垫要求与功率成正比散热和环境温度。专用层不需要单独的热垫区域。当专用层不可能1“x 1”的焊盘区域足够对于在+50°C环境下消散0.5W的EL4342。应根据具体情况评估焊盘区域要求案例基础。

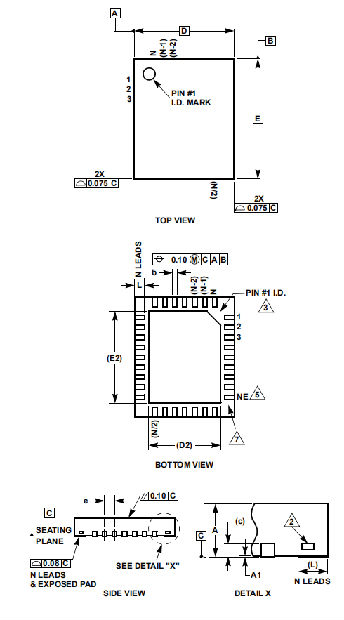

四平无铅塑料包装(QFN)

微型引线框架塑料包装(MLFP)

L32.5x6A(MDP0046中的10个包之一)

32导四平无铅塑料包装

(符合JEDEC MO-220)

笔记:

1、 尺寸和公差符合ASME Y14.5M-1994。

2、 显示的Tiebar视图是一个非功能特性。

3、 底侧销1内径是如图所示的模垫倒角。

4、 N是设备上的终端总数。

5、 是的。NE是封装“E”侧(或Y方向)的端子数。

6、 ND是封装“D”侧(或X方向)的端子数。ND=(N/2)-NE。

7、 终端的内端可以是方形或圆形半径(b/2)如图所示。

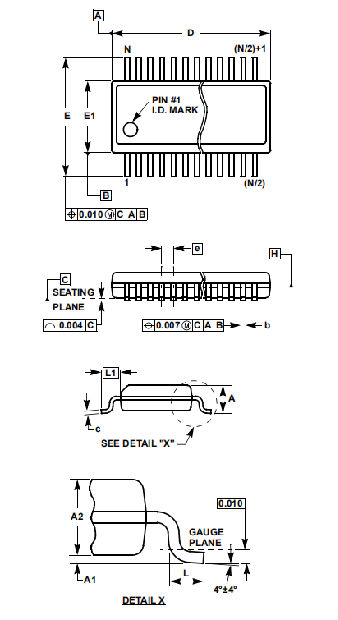

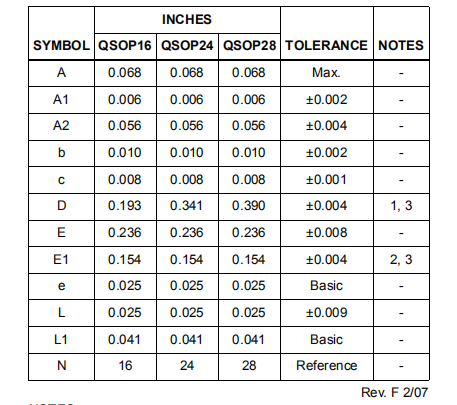

四分之一尺寸塑料包装系列(QSOP)

MDP0040型

四分之一尺寸塑料包装系列

笔记:

1、 不包括每侧最大0.006“的塑料或金属突出物。

2、 不包括每侧最大0.010“的塑料嵌线突出物。

3、 尺寸“D”和“E1”在基准面“H”处测量。

4、 尺寸和公差符合ASME Y14.5M-1994。