W25X16点击型号即可查看芯片规格书

W25X32点击型号即可查看芯片规格书

一般说明

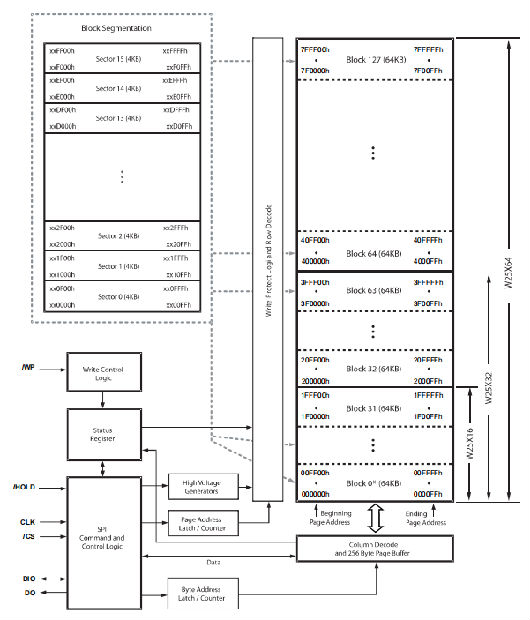

W25X16(16M位)、W25X32(32M位)和W25X64(64M位)串行闪存为空间、管脚和电源有限的系统提供了存储解决方案。25X系列提供了超越普通串行闪存设备的灵活性和性能。它们是代码下载应用程序以及存储语音、文本和数据的理想选择。这些设备在一个2.7V到3.6V的电源上工作,电流消耗低至5mA激活,1微a断电。所有设备都以节省空间的软件包提供。

W25X16/32/64分别具有512/1024/2048个可擦除扇区和32/64/128个可擦除块。小的4KB扇区允许在需要数据和参数存储的应用程序中具有更大的灵活性。

W25X16/32/64支持标准串行外围接口(SPI)和使用四个管脚的高性能双输出SPI:串行时钟、芯片选择、串行数据I/O和串行数据输出。当使用快速读取双输出指令时,支持高达75MHz的SPI时钟频率,允许150MHz的等效时钟速率。这些传输速率与8位和16位并行闪存相当。

一个保持引脚,写保护引脚和可编程写保护,具有顶部或底部阵列控制功能,提供进一步的控制灵活性。此外,该设备支持JEDEC标准

制造商和设备标识。

特征

•系列闪存

•单输出或双输出SPI

–时钟、芯片选择、数据I/O、数据输出

–可选的保持功能,提高SPI灵活性

•数据传输高达150M位/秒-时钟工作频率为75MHz

–快速读取双输出指令

–自动增量读取功能

•具有4KB扇区的灵活架构

–扇区擦除(4K字节)

–块擦除(64K字节)

–页面程序最大256字节<2ms

–多达100000个擦除/写入周期

•低功耗,宽

温度范围

–单个2.7至3.6V电源

–5毫安有功电流,1微安断电(典型)

–-40°至+85°C工作范围

•软件和硬件写保护-写保护全部或部分内存

–使用/WP引脚启用/禁用保护

–顶部或底部阵列保护

•节省空间的包装

–8针SOIC 208 mil(宽25x16,X32)

–8针PDIP 300 mil(宽25x16,X32,X64)

–16针SOIC 300 mil(宽25x16,X32,X64)

–8垫WSON 6x5毫米(宽25x16)

–8垫WSON 8x6毫米(宽25x32,X64)

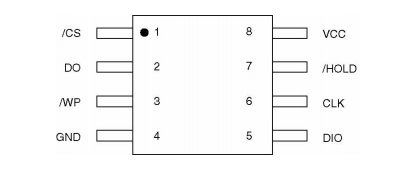

引脚配置SOIC 208-MIL

图1a.W25X16和W25X32引脚分配,8针SOIC(封装代码SS)

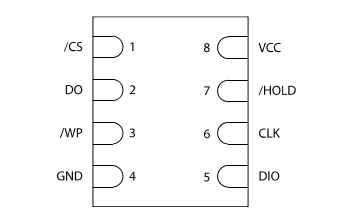

销配置WSON 6X5-MM

图1b.W25X16针分配,8针WSON(包装代码ZP)

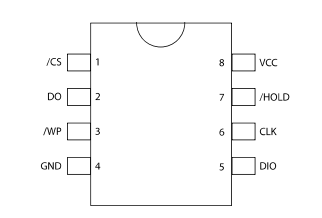

引脚配置PDIP 300-MIL

图1c.W25X16、W25X32、W25X64引脚分配、8引脚PDIP(封装代码DA)

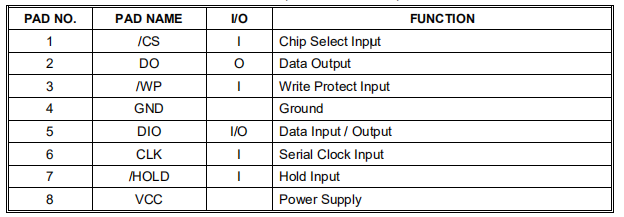

引脚说明SOIC 208-MIL、PDIP 300-MIL和WSON 6X5-MM

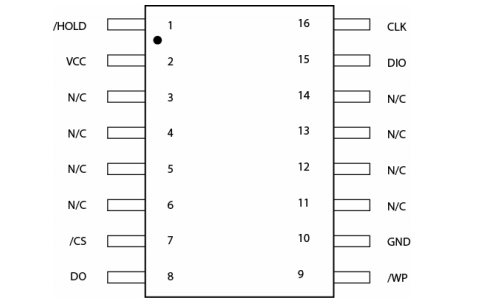

引脚配置SOIC 300-MIL

包装类型

在发布此数据表时,并非所有包类型都已完成。在按照本规范进行设计之前,请与Winbond联系以确认这些包的可用性。W25X16和W25X32采用8针208mil宽的塑料SOIC(封装代码SS)。W25X16 in 6x5 mm WSON(包装代码ZP)和25X32和25X64 in 8x6 mm WSON。(包装代码ZE)。25X16、W25X32和W25X64采用16针塑料300 mil宽SOIC(封装代码SF)和300 mil DIP(封装代码DA)。参见图1a-d。包装图和尺寸如本数据表末尾所示。

芯片选择(/CS)

SPI Chip Select(/CS)管脚启用和禁用设备操作。当/CS为高时,设备被取消选择,串行数据输出(DO)引脚处于高阻抗。当取消选择时,除非正在进行内部擦除、程序或状态寄存器循环,否则设备功耗将处于待机状态。当/CS降低时,将选择设备,功耗将增加到活动级别,可以向设备写入指令并从设备读取数据。通电后,/CS必须从高转换到低,才能接受新指令。/CS输入必须跟踪通电时的VCC电源电平(参见“写保护”和图20)。如果需要,可以使用/CS上的上拉电阻器来完成此操作。

串行数据输出(DO)

SPI串行数据输出(DO)管脚提供了一种从设备串行读取(移出)数据和状态的方法。数据在串行时钟(CLK)输入引脚的下降沿向外移动。

写保护(/WP)

写入保护(/WP)引脚可用于防止写入状态寄存器。与状态寄存器的块保护(BP2、BP1和BP0)位和状态寄存器保护(SRP)位一起使用,部分或整个存储器阵列可以受到硬件保护。/WP引脚处于低激活状态。

保持(/保持)

/HOLD pin允许在设备处于活动状态时暂停设备。当/HOLD变低时,当/CS变低时,DO管脚将处于高阻抗,DIO和CLK管脚上的信号将被忽略(不要在意)。当/HOLD处于高位时,设备操作可以恢复。当多个设备共享相同的SPI信号时,/HOLD功能非常有用。(“参见保持功能”)

串行时钟(CLK)

SPI串行时钟输入(CLK)引脚提供串行输入和输出操作的定时。(“见SPI操作“)

8.7串行数据输入/输出(DIO)

SPI串行数据输入/输出(DIO)管脚提供了一种将指令、地址和数据串行写入(移入)设备的方法。数据锁定在串行时钟(CLK)输入引脚的上升沿上。在执行快速读取双输出指令时,DIO管脚也用作输出。

方块图

W25X16、W25X32和W25X64框图

功能描述

SPI操作

SPI模式

W25X16/32/64通过一个SPI兼容总线访问,该总线由四个信号组成:串行时钟(CLK)、芯片选择(/CS)、串行数据输入/输出(DIO)和串行数据输出(DO)。支持SPI总线操作模式0(0,0)和3(1,1)。模式0和模式3之间的主要区别在于SPI总线主设备处于待机状态且数据未传输到串行闪存时CLK信号的正常状态。对于模式0,CLK信号通常较低。对于模式3,CLK信号通常为高电平。在这两种情况下,DIO管脚上输入的数据在CLK的上升沿上采样。DO和DIO管脚的数据在CLK下降沿上计时。

双输出SPI

W25X16/32/64在使用“双输出快速读取”(3B hex)指令时支持双输出操作。此功能允许以两倍于标准SPI的速率从串行闪存传输数据。此指令非常适合在通电时将代码从闪存快速下载到RAM(代码阴影)或将代码段缓存到RAM以供执行的应用程序。双输出特性只允许SPI输入管脚在本指令期间也用作输出。所有其他操作都使用带有单个输出信号的标准SPI接口。

保持功能

/HOLD信号允许W25X16/32/64操作在被激活时暂停(当/CS低时)。在SPI数据和时钟信号与其他设备共享的情况下,/保持功能可能有用。例如,当优先级中断需要使用SPI总线时,考虑是否只部分写入了页面缓冲区。在这种情况下,/HOLD函数可以将指令和数据的状态保存在缓冲区中,这样一旦总线再次可用,编程就可以在中断的地方恢复。

要启动a/HOLD条件,必须选择/CS低的设备。如果CLK信号已经很低,A/HOLD状态将在/HOLD信号的下降沿激活。如果CLK还不低,则/保持条件将在CLK的下一个下降沿后激活。如果CLK信号已经很低,/HOLD条件将在/HOLD信号的上升沿终止。如果CLK不低,则/保持条件将在CLK的下一个下降沿之后终止。

在a/HOLD状态下,串行数据输出(DO)为高阻抗,忽略串行数据输入/输出(DIO)和串行时钟(CLK)。芯片选择(/CS)信号应在/HOLD操作的整个持续时间内保持激活(低),以避免重置设备的内部逻辑状态。

写保护

使用非易失性存储器的应用程序必须考虑噪声和其他可能损害数据完整性的不利系统条件的可能性。为了解决这个问题,W25X16/32/64提供了几种保护数据不被意外写入的方法。

写保护特性

•当VCC低于阈值时,设备复位。

•通电后时间延迟写入禁用。

•编写启用/禁用指令。

•程序和擦除后自动写入禁用。

•使用状态寄存器的软件写保护。

•使用状态寄存器和/WP引脚的硬件写保护。

•使用断电指令写入保护

通电或断电时,当VCC低于VWI的阈值时,W25X16/32/64将保持复位状态(参见通电定时和电压水平以及图20)。重置时,将禁用所有操作,并且不识别任何指令。在通电期间以及在VCC电压超过VWI之后,由于tPUW的时间延迟,所有与程序和擦除相关的指令进一步被禁用。这包括写入启用、页面程序、扇区擦除、块擦除、芯片擦除和写入状态寄存器指令。注意,芯片选择引脚(/CS)必须在通电时跟踪VCC电源电平,直到达到VCC最小电平和tVSL延时。如果需要,可以使用/CS上的上拉电阻器来完成此操作。

通电后,设备将自动置于状态寄存器的写禁用状态

写入启用闩锁(WEL)设置为0。在接受页程序、扇区擦除、芯片擦除或写入状态寄存器指令之前,必须发出允许写入指令。完成程序、擦除或写入指令后,写入启用闩锁(WEL)将自动清除为0的写禁用状态。

使用写状态寄存器指令和设置状态寄存器保护(SRP)和块保护(TB、BP2、BP1和BP0)位有助于软件控制的写保护。这些状态寄存器位允许部分或全部存储器配置为只读。与写保护(/WP)管脚一起使用,可以在硬件控制下启用或禁用对状态寄存器的更改。有关更多信息,请参阅状态寄存器。

此外,掉电指令提供了额外的写保护级别,因为除了释放掉电指令之外,所有指令都被忽略。

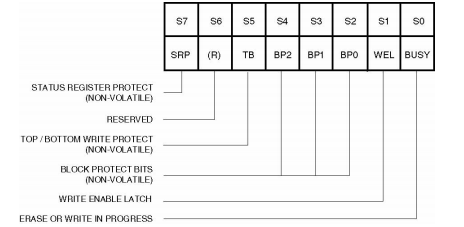

控制和状态寄存器

读状态寄存器指令可用于提供闪存阵列可用性的状态(如果设备已启用或禁用写)和写保护状态。写状态寄存器指令可用于配置设备写保护功能。见图3。

状态寄存器

BUSY是状态寄存器(S0)中的只读位,当设备执行页程序、扇区擦除、块擦除、芯片擦除或写入状态寄存器指令时,该位被设置为1状态。在此期间,设备将忽略除读取状态寄存器指令以外的其他指令(参见交流特性中的tW、tPP、tSE、TBE和tCE)。当程序、擦除或写入状态寄存器指令完成时,忙碌位将被清除到0状态,指示设备已准备好接受进一步指令。

写入启用闩锁(WEL)

写启用锁存器(WEL)是状态寄存器(S1)中的只读位,在执行写启用指令后设置为1。当设备写禁用时,WEL状态位清除为0。在通电时或在以下任何指令之后出现写禁用状态:写禁用、页面程序、扇区擦除、块擦除、芯片擦除和写状态寄存器。

块保护位(BP2、BP1、BP0)

块保护位(BP2、BP1和BP0)是状态寄存器(S4、S3和S2)中提供写保护控制和状态的非易失性读/写位。可以使用写状态寄存器指令设置块保护位(见交流特性中的tW)。所有、无或部分存储器阵列都可以免受程序和擦除指令的保护(参见状态寄存器存储器保护表)。块保护位的出厂默认设置为0,没有受保护的数组。如果状态寄存器保护(SRP)位设置为1且写入保护(/WP)引脚低,则无法写入块保护位。

顶部/底部块保护(TB)

上/下位(TB)控制块保护位(BP2、BP1、BP0)是从数组的顶部(TB=0)还是底部(TB=1)进行保护,如状态寄存器内存保护表所示。TB位是非易失性的,出厂默认设置为TB=0。TB位可以用Write Status Register指令设置,前提是已发出Write Enable指令。如果状态寄存器保护(SRP)位设置为1且写入保护(/WP)引脚低,则无法写入TB位。

保留位

状态寄存器位位置S6留作将来使用。当前设备将为此位位置读取0。建议在测试状态寄存器时屏蔽保留位。这样做将确保与未来设备的兼容性。

状态寄存器保护(SRP)

状态寄存器保护(SRP)位是状态寄存器(S7)中的非易失性读/写位,可与写保护(/WP)引脚一起使用,以禁用对状态寄存器的写操作。当SRP位设置为0状态(出厂默认值)时,/WP pin对状态寄存器没有控制权。当SRP引脚设置为1时,当/WP引脚低时,写状态寄存器指令被锁定。当/WP引脚高时,允许写入状态寄存器指令。

说明

W25X16/32/64的指令集由15个基本指令组成,这些指令通过SPI总线完全控制(请参阅指令集表)。使用芯片选择的下降沿(/CS)启动指令。进入DIO输入的数据的第一个字节提供指令代码。DIO输入数据在时钟上升沿采样,最高有效位(MSB)在前。

指令的长度从一个字节到几个字节不等,后面可能是地址字节、数据字节、伪字节(不必在意),在某些情况下,可能是一个组合。使用edge/CS的上升沿完成说明。图4到图19中包括了每条指令的时钟相关时序图。所有读取指令都可以在任何计时位之后完成。但是,所有写入、编程或擦除的指令都必须在字节边界上完成(在一个完整的8位时钟后,CS驱动高),否则指令将终止。此功能进一步保护设备免受意外写入。此外,当存储器被编程或擦除时,或当状态寄存器被写入时,除读取状态寄存器外的所有指令都将被忽略,直到程序或擦除周期完成。

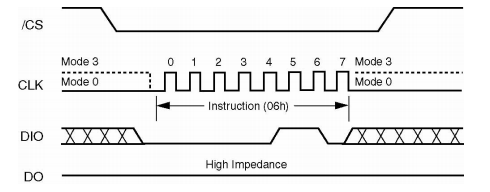

允许写入(06h)

Write Enable指令(图)将状态寄存器中的Write Enable闩锁(WEL)位设置为1。WEL位必须在每个页面程序、扇区擦除、块擦除、芯片擦除和写入状态寄存器指令之前设置。通过驱动/CS low,将指令代码“06h”移到CLK上升沿上的数据输入(DI)管脚中,然后驱动/CS high来输入Write Enable指令。

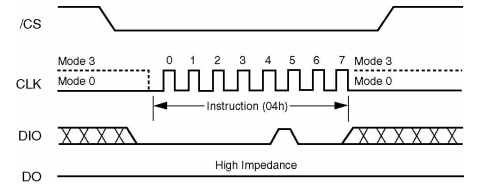

禁止写入(04h)

Write Dissable指令(图)将状态寄存器中的Write Enable闩锁(WEL)位重置为0。通过driving/CS low,将指令代码“04h”移到DIO pin,然后driving/CS high来输入写禁用指令。请注意,WEL位在通电后和写入状态寄存器、页面程序、扇区擦除、块擦除和芯片擦除指令完成后自动重置

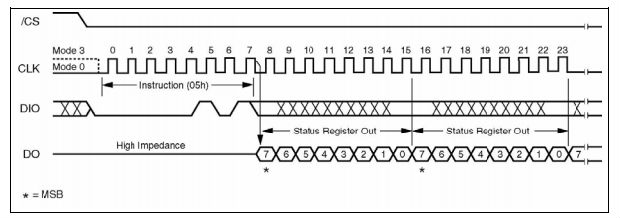

读取状态寄存器(05h)

读取状态寄存器指令允许读取8位状态寄存器。通过驱动/CS low并将指令代码“05h”移入CLK上升沿上的DIO引脚来输入指令。然后,状态寄存器位在CLK下降沿的DO管脚上向外移位,最有效位(MSB)首先如图所示。状态寄存器位如图3所示,包括BUSY、WEL、BP2-BP0、TB和SRP位(参见本数据表前面对状态寄存器的描述)。

状态寄存器指令可以在任何时候使用,即使程序、擦除或写入状态寄存器周期正在进行。这允许检查忙状态位,以确定周期何时完成以及设备是否可以接受另一条指令。状态寄存器可以连续读取,如图所示。该指令通过驱动/CS high完成。

写入状态寄存器(01h)

写入状态寄存器指令允许写入状态寄存器。必须先执行写启用指令,设备才能接受写状态寄存器指令(状态寄存器位WEL必须等于1)。一旦启用写操作,通过驱动/CS low输入指令,发送指令代码“01h”,然后写入状态寄存器数据字节,如图7所示。状态寄存器位如图3所示,并在本数据表的前面描述。

只能写入非易失性状态寄存器位SRP、TB、BP2、BP1和BP0(位7、5、4、3和2)。所有其他状态寄存器位位置都是只读的,不会受到写入状态寄存器指令的影响。

CS管脚必须在最后一个字节的第八位被锁定后被驱动到高位。如果不这样做,写状态寄存器指令将不会被执行。在/CS被高驱动后,自动定时写入状态寄存器周期将开始,持续时间为tW(见AC特性)。当正在进行写入状态寄存器周期时,仍可访问读取状态寄存器指令以检查忙位的状态。在写入状态寄存器周期中,忙碌位是1;在周期结束并准备再次接受其他指令时,忙碌位是0。写入寄存器循环完成后,状态寄存器中的写入启用闩锁(WEL)位将清除为0。Write Status Register指令允许设置块保护位(TB、BP2、BP1和BP0),以保护所有、部分或无内存不受擦除和编程指令的影响。保护区变为只读(见状态寄存器内存保护表)。写入状态寄存器指令还允许设置状态寄存器保护位(SRP)。此位与写保护(/WP)引脚一起使用,以禁用对状态寄存器的写操作。当SRP位设置为0状态(出厂默认值)时,/WP pin对状态寄存器没有控制权。当SRP引脚设置为1时,当/WP引脚低时,写状态寄存器指令被锁定。当/WP引脚高时,允许写入状态寄存器指令。写状态寄存器指令序列图

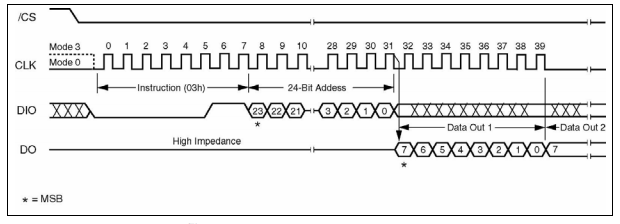

读取数据(03h)

读取数据指令允许从存储器中顺序读取一个以上的数据字节。该指令通过将/CS pin低驱动,然后将指令代码“03h”后跟24位地址(A23-A0)移入DIO pin来启动。代码和地址位锁定在CLK引脚的上升沿上。接收到地址后,地址存储器位置的数据字节将在CLK下降沿的DO管脚上移位,最高位(MSB)优先。在每个字节的数据被移出允许连续的数据流之后,地址自动递增到下一个更高的地址。这意味着只要时钟继续,整个存储器可以用一条指令访问。该指令通过驱动/CS high完成。读取数据指令序列如图8所示。如果在执行擦除、程序或写入周期(BUSY=1)时发出读取数据指令,该指令将被忽略,并且不会对当前周期产生任何影响。读取数据指令允许从直流到最大fR的时钟速率(见交流电气特性)

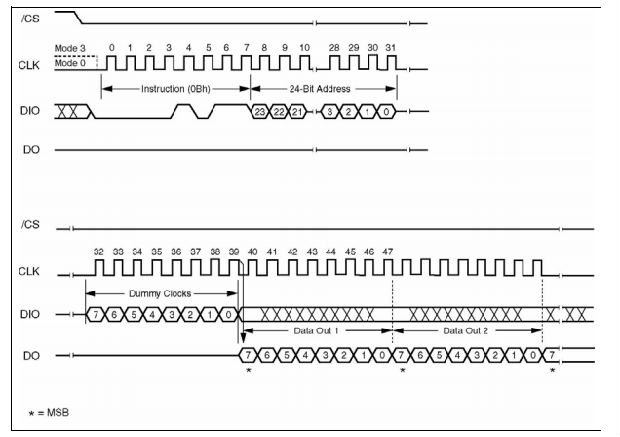

快速读取指令序列图

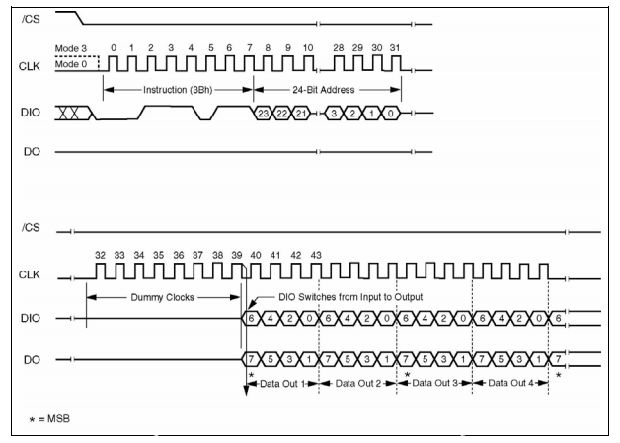

快速读取双输出(3Bh)

快速读取双输出(3Bh)指令与标准快速读取(0Bh)指令类似,只是数据输出在DO和DIO两个管脚上,而不是只输出DO。这允许以两倍于标准SPI设备的速率从W25X16/32/64传输数据。快速读取双输出指令非常适合在通电时从闪存快速下载代码到RAM,或用于将代码段缓存到RAM以供执行的应用程序。

与快速读取指令类似,快速读取双输出指令可以在FR的最高可能频率下工作(参见交流电气特性)。这是通过在24位地址之后添加8个“虚拟”时钟来实现的,如图10所示。虚拟时钟允许设备的内部电路有额外的时间来设置初始地址。在虚拟时钟期间的输入数据是“不在乎”。然而,在第一个数据输出时钟的下降沿之前,DIO管脚应该是高阻抗的。

快速读取双输出指令序列图

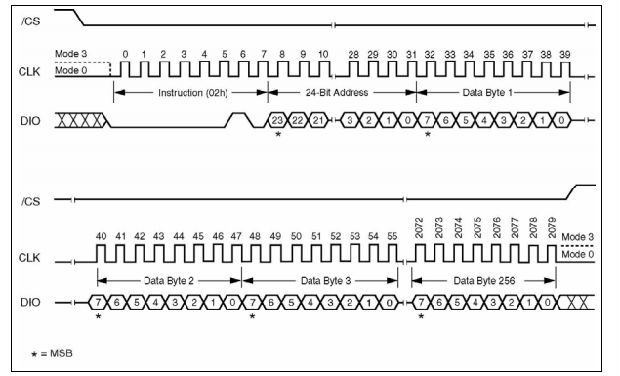

页面程序(02h)

页面编程指令允许在先前擦除的所有1s(FFh)内存位置编程多达256字节的数据。在设备接受页面程序指令(状态寄存器位WEL必须等于1)之前,必须执行写启用指令。通过驱动/CS pin低位,然后将指令代码“02h”后跟24位地址(A23-A0)和至少一个数据字节移入DIO pin来启动指令。当数据发送到设备时,/CS管脚必须在指令的整个长度内保持低位。

如果要对整个256字节的页面进行编程,则最后一个地址字节(8个最低有效地址位)应设置为0。如果最后一个地址字节不为零,并且时钟数超过了剩余的页面长度,则寻址将自动换行到页面的开头。在某些情况下,少于256个字节(一个部分页面)可以编程,而不会对同一页面内的其他字节产生任何影响。执行部分页面程序的一个条件是时钟的数目不能超过剩余的页面长度。如果发送到设备的字节数超过256,寻址将自动换行到页面的开头并覆盖以前发送的数据。

与write和erase指令一样,在最后一个字节的第八位被锁定后,/CS管脚必须被驱动到高位。如果不这样做,页面程序指令将不会被执行。在/CS被高驱动后,自计时页程序指令将在tpp的一段时间内开始(见AC Characteristics)。当页程序周期正在进行时,仍然可以访问读状态寄存器指令来检查忙位的状态。在页面程序周期中,忙碌位是1,当周期结束且设备准备好再次接受其他指令时,忙碌位变为0。页面程序循环完成后,状态寄存器中的写入启用闩锁(WEL)位清除为0。如果编址页受块保护(BP2、BP1和BP0)位保护(见状态寄存器存储器保护表),则不会执行页程序指令。

页面程序指令序列图

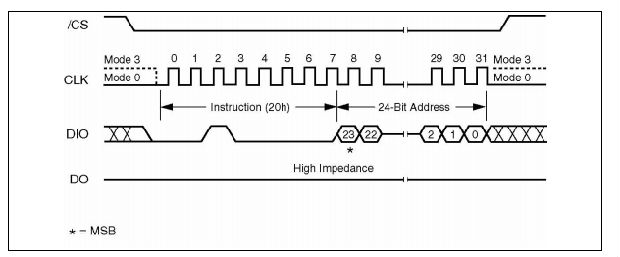

扇区擦除(20h)

扇区擦除指令将指定扇区(4K字节)内的所有内存设置为所有1s(FFh)的擦除状态。在设备接受扇区擦除指令(状态寄存器位WEL必须等于1)之前,必须执行写启用指令。该指令通过驱动/CS引脚低位并在24位扇区地址(A23-A0)后移动指令代码“20h”来启动(见图)。

/CS管脚必须在最后一个字节的第八位被锁定后被驱动到高位。如果不这样做,扇区擦除指令将不会执行。在/CS被高速驱动后,自计时扇区擦除指令将在tSE的一段时间内开始(见AC特性)。当扇区擦除周期正在进行时,仍然可以访问读取状态寄存器指令以检查忙位的状态。在扇区擦除周期中,忙碌位为1,当周期结束且设备准备好再次接受其他指令时,忙碌位变为0。扇区擦除循环完成后,状态寄存器中的写入启用闩锁(WEL)位清除为0。如果寻址页受块保护(TB、BP2、BP1和BP0)位保护(请参阅状态寄存器内存保护表),则不会执行扇区擦除指令。

块擦除(D8h)

块擦除指令将指定块(64K字节)内的所有内存设置为所有1s(FFh)的擦除状态。在设备接受块擦除指令(状态寄存器位WEL必须等于1)之前,必须执行写启用指令。该指令通过驱动/CS引脚低位并在24位块地址(A23-A0)后移动指令代码“D8h”来启动(见图)。

/CS管脚必须在最后一个字节的第八位被锁定后被驱动到高位。如果不这样做,块擦除指令将不会执行。在/CS被高驱动之后,自计时块擦除指令将在tBE的一段时间内开始(参见AC特性)。当块擦除周期正在进行时,仍可以访问读取状态寄存器指令以检查忙位的状态。在块擦除周期中,忙碌位是1,在周期结束且设备准备好再次接受其他指令时变为0。块擦除循环完成后,状态寄存器中的写入启用闩锁(WEL)位清除为0。如果地址页受块保护(TB、BP2、BP1和BP0)位保护(见状态寄存器内存保护表),则不会执行块擦除指令

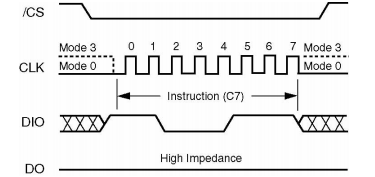

芯片擦除(C7h)

芯片擦除指令将设备内的所有存储器设置为所有1s(FFh)的擦除状态。一个

写入启用指令必须在设备接受芯片擦除指令之前执行(状态寄存器位WEL必须等于1)。该指令通过将/CS管脚压低并移动指令代码“C7h”来启动。

在锁定第八个位后,必须将/CS引脚驱动到高位。如果不这样做,芯片擦除指令将不会执行。在/CS被高驱动后,自计时芯片擦除指令将在tCE的一段时间内开始(见AC特性)。当芯片擦除周期正在进行时,仍然可以访问读取状态寄存器指令来检查忙位的状态。在芯片擦除周期中,忙位为1,完成后变为0,设备准备再次接受其他指令。在芯片擦除周期结束后,状态寄存器中的写入启用闩锁(WEL)位被清除为0。如果任何页受到块保护(BP2、BP1和BP0)位的保护(参见状态寄存器存储器保护表),则不会执行芯片擦除指令。

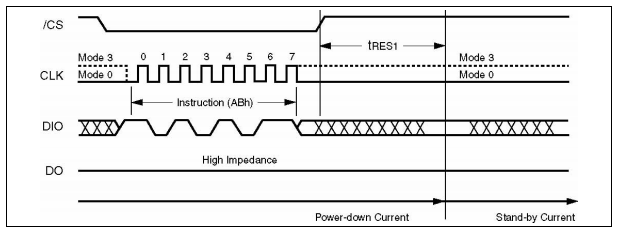

4断电(B9h)

虽然正常运行时的备用电流相对较低,但随着掉电指令的执行,备用电流可以进一步降低。较低的功耗使得掉电指令对于电池供电的应用特别有用(参见AC特性中的ICC1和ICC2)。如图所示,通过低驱动/CS引脚并移动指令代码“B9h”来启动指令。

在锁定第八个位后,必须将/CS引脚驱动到高位。如果不这样做,就不会执行断电指令。在/CS被驱动高之后,在tDP的持续时间内进入掉电状态(见交流特性)。当处于关机状态时,将只识别从关机/设备ID指令中释放,该指令将设备恢复到正常操作。忽略所有其他指令。这包括读取状态寄存器指令,它在正常操作期间始终可用。忽略除一条指令以外的所有指令会使关机状态成为确保最大写保护的有用条件。装置在正常运行时,总是以ICC1的备用电流通电。

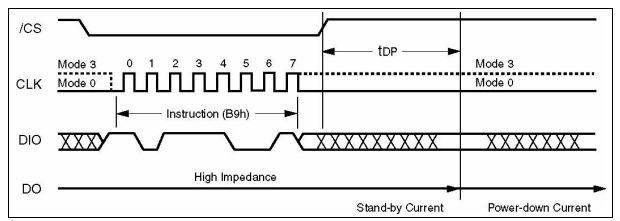

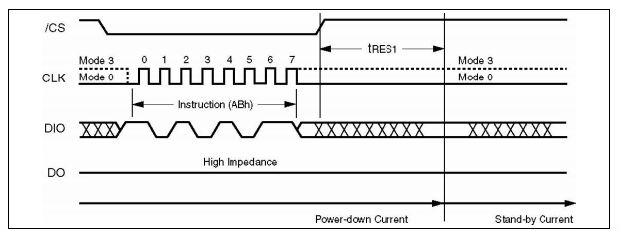

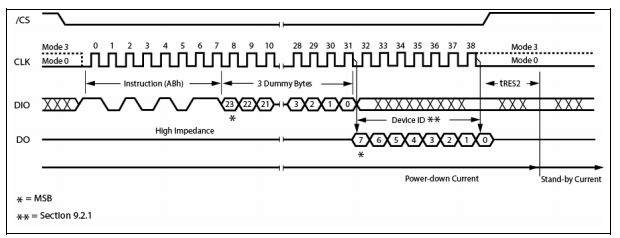

释放掉电/设备ID(ABh)

断电释放/设备标识指令是一个多用途指令。它可以用来解除设备的断电状态,获取设备的电子标识(ID)号码或两者兼而有之。

当仅用于将设备从断电状态释放时,通过驱动/CS pin low、移动指令代码“ABh”和驱动/CS high来发出指令,如图16所示。在tRES1(见交流特性)持续时间后,设备将恢复正常运行,并接受其他指令。/CS引脚在tRES1持续时间内必须保持高。

当仅用于在非断电状态下获取设备ID时,通过将/CS pin低驱动并将指令代码“ABh”后跟3个伪字节移位来启动该指令。然后,设备ID位在CLK的下降沿上向外移动,首先是最高有效位(MSB),如图17所示。W25X16、W25X32和W25X64的设备ID值列在制造商和设备标识表中。可以连续读取设备ID。该指令通过驱动/CS high完成。

当用于将设备从断电状态释放并获取设备ID时,该指令与前面描述的和图17所示的相同,只是/CS被高驱动后,它必须在tRES2的时间内保持高电平(参见AC特性)。在此时间之后,设备将恢复正常操作,并接受其他指令。

如果在执行擦除、程序或写入周期(当BUSY等于1时)时发出断电/设备ID指令,则该指令将被忽略,并且不会对当前周期产生任何影响

释放断电/设备ID指令序列图

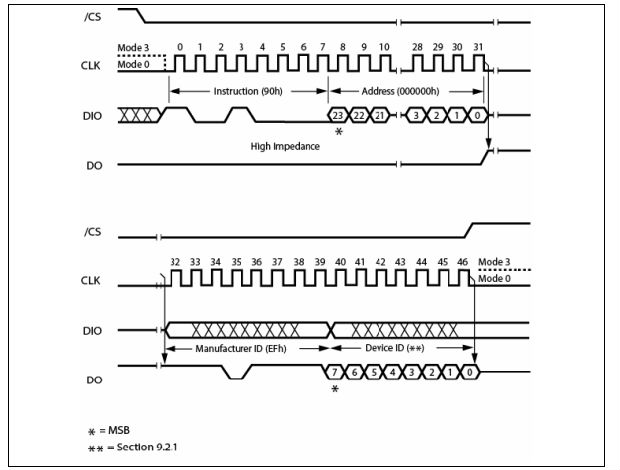

读取制造商/设备ID(90h)

读取制造商/设备ID指令是断电释放/设备ID指令的替代,该指令提供JEDEC分配的制造商ID和特定设备ID。

读取制造商/设备ID指令与断电释放/设备ID指令非常相似。指令通过将/CS pin低驱动并移动指令代码“90h”,然后移动24位地址(A23-A0)000000 h来启动。之后,Winbond(EFh)的制造商ID和设备ID在CLK的下降沿上向外移动,最有效位(MSB)在前,如图所示。W25X16、W25X32和W25X64的设备ID值列在制造商和设备标识表中。如果24位地址最初设置为00000 1h,则首先读取设备ID,然后读取制造商ID。可以连续读取制造商和设备ID,从一个到另一个交替读取。该指令通过驱动/CS high完成。

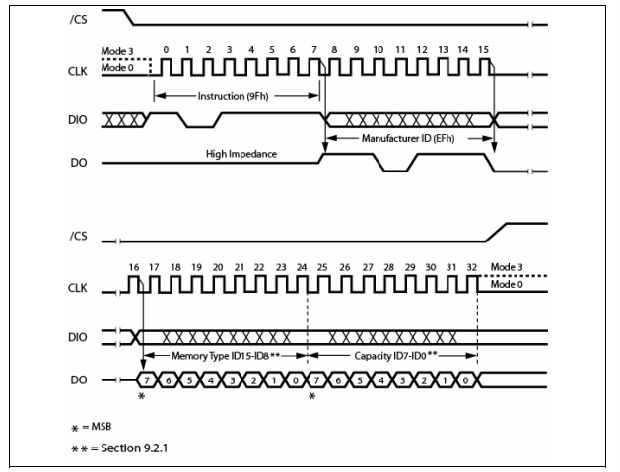

读取制造商/设备ID图

出于兼容性的原因,W25X16/32/64提供了一些以电子方式确定设备标识的说明。Read JEDEC ID指令与2003年采用的SPI兼容串行存储器JEDEC标准兼容。

该指令通过将/CS管脚压低并移动指令代码“9Fh”来启动。然后,JEDEC为Winbond(EFh)分配的制造商ID字节和两个设备ID字节、内存类型(ID15-ID8)和容量(ID7-ID0)将在CLK的下降沿上移位,首先是最高有效位(MSB),如图所示。有关存储器类型和容量值,请参阅制造商和设备标识表。