24V点击型号即可查看芯片规格书

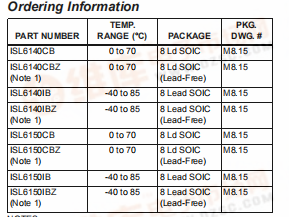

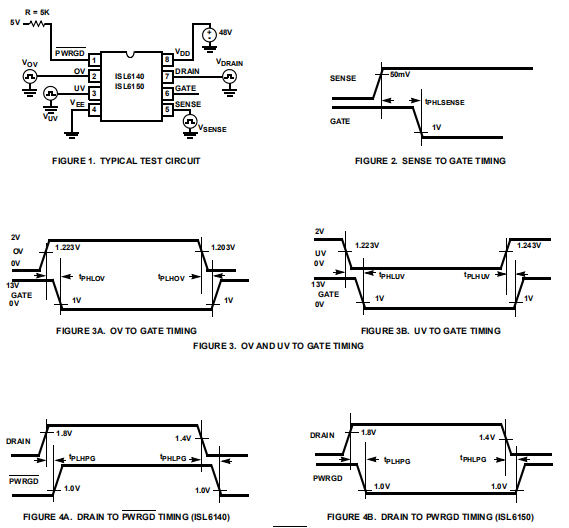

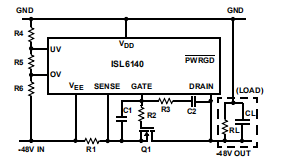

ISL6140是一个8针、负电压热插拔控制器使电路板能够安全地从带电背板。励磁涌流限制在可编程范围内通过控制外部N通道晶体管。如果输入电压低于欠压阈值,或大于过电压阈值。可编程的电子断路器防止系统短路。激活的低PWRGD信号可用于直接启用电源模块(低启用输入)ISL6150是相同的部分,但有一个活动的高PWRGD信号。

100536.png" />

100536.png" />

笔记:

1.Intersil无铅产品采用特殊无铅材料组套;模塑料/模贴材料和100%哑光镀锡板终端饰面,与SnPb和无铅焊接操作兼容。Intersil无铅产品为MSL在无铅峰值回流焊温度下分类超过IPC/JEDEC J Std-020B的无铅要求。

2.在磁带和卷盘的零件号上添加后缀“-T”。

特征

低端外部NFET开关

在-10V到-80V之间运行(-100V绝对最大额定值)或+10V至+80V(+100V绝对最大额定值)

可编程励磁涌流

可编程电子断路器(过电流关闭)

可编程过电压保护

可编程欠压锁定

功率良好的控制输出-PWRGD Active High:(H版本)ISL6150-PWRGD活动低:(L版本)ISL6140

可选无铅

应用

VoIP(互联网语音协议)服务器

电信系统-48V

负电源控制

+24V无线基站电源

相关文献

ISL6140/50EVAL1板组,文件#AN9967

ISL6116热插拔控制器,文件#FN4778

管脚说明

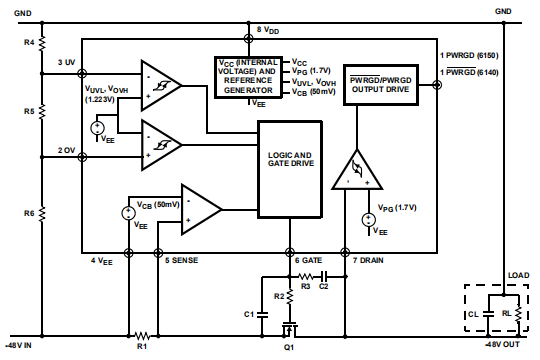

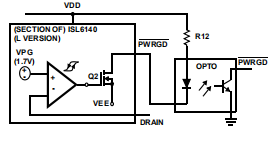

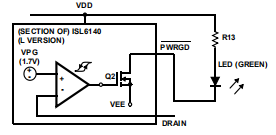

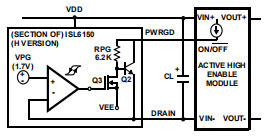

PWRGD(ISL6140;L版本)引脚1-此数字输出为一种开放式排水下拉装置。权力善比较器查看漏极引脚电压与内部VPG参考(VPG为标称1.7V);这基本上测量通过外部的电压降场效应晶体管和感应电阻。如果电压降很小(<1.7V正常),PWRGD引脚拉低(转向);这可以是用作外部模块的有效低启用。如果电压降太大(>1.7V表示某种短路或过载情况),下拉装置关闭,并且引脚变为高阻抗。通常,用某种形式的外部拉起将销钉拉高(许多砖监管者有一个内置的上拉功能。PWRGD(ISL6150;H版本)引脚1-此数字输出为一种开放式排水下拉装置的变体。权力好的比较器和上面描述的一样,但是输出极性颠倒,如下所示:如果通过场效应管的电压降过大(>1.7V),则打开漏极下拉装置,将电流汇至放油销。如果电压降很小(<1.7V),则与6.2K电阻器串联的下拉装置(标称)将电流转换为V型;如果外部上拉电流低足够(<1毫安,例如),通过电阻将足够大,看起来像逻辑高信号(in本例中,1毫安*6.2千欧=6.2伏)。因此,该销可以用作外部模块的激活高启用信号。注意,对于这两个版本,虽然这是一个数字管脚从功能上讲,逻辑高级是由外部上拉装置和它所连接的电源已连接;IC不会将其钳制到低于VDD电压。

因此,如果外部设备没有自己的夹钳,或者如果它会被高压损坏,那么可能需要外夹OV(过电压)引脚2-此模拟输入比较引脚上的电压与内部电压基准(标称1.223伏)。当输入高于参考值时(低至高跃迁),表示过电压状态,门销立即被拉低至关闭外部FET。因为有20毫伏的标称电压迟滞内建,门将保持关闭,直到OV引脚低于1.203V(标称)高-低阈值。一个典型应用将使用外部电阻分压器VDD到VEE,根据需要设置OV电平;三个电阻除法器可以设置OV和UV。紫外线(欠压)引脚3-此模拟输入比较引脚上的电压与内部电压基准(标称1.223伏)。当输入低于参考值时(高到低转换),表示紫外线(欠电压)状态,门销立即被拉低至关闭外部FET。因为有20毫伏的标称电压迟滞内建,栅极将保持关闭,直到紫外线针高于1.243V(标称)的低至高阈值。一个典型应用将使用外部电阻分压器将VDD转换成VEE,根据需要设置UV电平;三个电阻除法器可以设置OV和UV。如果存在过流情况,门钉将被锁定关闭,然后使用紫外线管脚重置过电流插销;插销必须从外部拉到其触发点以下,为了打开大门返回(假设故障条件已消失)。V形管脚4-这是最负的电源电压,例如和-48V系统一样。其他信号大多是相对于此pin引用,即使它可能很远远离被认为是GND参考的地方。

检测引脚5-此模拟输入测量电压降通过外部感测电阻器(感测和VEE),以确定电流是否超过过电流跳闸点,等于标称值(50mV/Rsense)。噪音峰值过滤掉小于2微秒;如果需要更长的峰值过滤后,可以将额外的RC时间常数添加到延长时间(参见图;注意FET必须能够处理额外时间的高电流)。到禁用过流功能,连接检测引脚转向。

门引脚6-此模拟输出驱动用作晶体管的外部场效应管。门钉是当紫外管脚高(高于其触发点)时,高(FET打开);OV引脚低(低于其触发点),没有过电流情况(VSENSE-VEE<50mV)。如果有3个违反条件时,门销将被拉低至关掉场效应管。栅极由微弱的(标称值为-45微安)上拉驱动电流源,以便慢慢打开场效应管。它是被驱动的通过一个强大的(标称32mA)下拉装置降低,以便如果发生过电流,请迅速关闭场效应管或短路。漏极引脚7-此模拟输入比较外部FET漏极到内部VPG基准(标称1.7V),用于功率良好的功能。注意,功率良好比较器不会关闭门钉。但是,当闸门关闭时OV,UV或SENSE),功率良好的比较器通常然后切换到电源不好的状态,因为一个关场效应管会有电源电压通过。VDD引脚8-这是最正极的电源引脚。它电压范围为+10至+80V(相对于V型)。中频操作预计在10V以下,用户应小心选择一个场效应晶体管来匹配降低的栅极电压如规格表所示。

绝对最大额定值热信息

电源电压(VDD至V型)。-0.3V至100V

漏极,PWRGD,PWRGD电压。-0.3V至100V

UV,OV输入电压。-0.3V至60V

感应,栅极电压。-0.3V至20V

静电放电额定值

人体模型(根据MIL-STD-883方法3015.7)。2000伏

操作条件

温度范围(工业)。-40°C至85°C

温度范围(商用)。0°C至70°C

电源电压范围(典型)。36V至72V

热阻(典型,注3)θJA(摄氏度/瓦)8铅SOIC。95个

最高结温(塑料包装)。150摄氏度

最高储存温度范围。-65°C至150°C

最高引线温度(焊接10s)。300摄氏度

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作

在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

笔记:

3.θJA是用安装在自由空气中的高效热导率测试板上的元件测量的。详见技术简报TB379。

4.典型值取决于VDD电压;见图13,“VGATE vs VDD”(<20V)。

5.PWRGD指排水管;VPWRGD-VDRAIN=0V

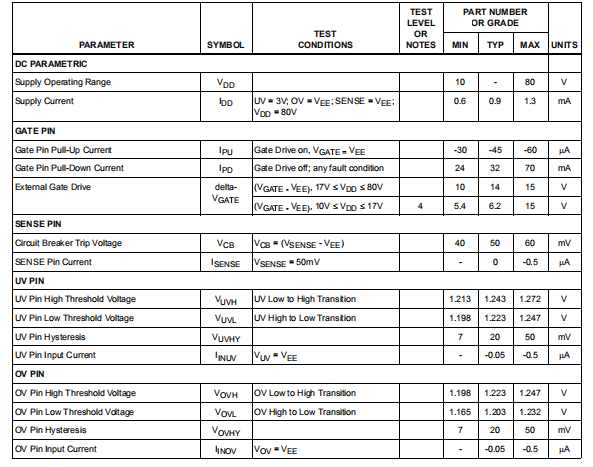

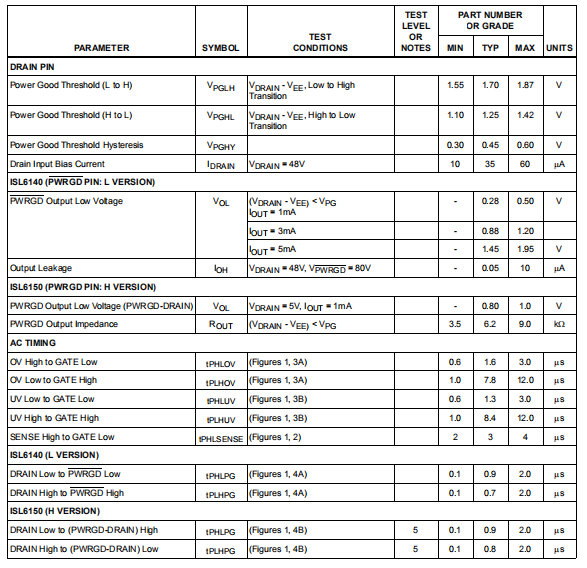

电气规范VDD=+48V,VEE=+0V,除非另有规定。所有测试都超过了整个温度范围;或者商用(0°C至70°C)或工业(-40°C至85°C)。典型规格为25°C。

电气规范VDD=+48V,VEE=+0V,除非另有规定。所有测试都超过了整个温度范围;或者商用(0°C至70°C)或工业(-40°C至85°C)。典型规格为25°C(续)

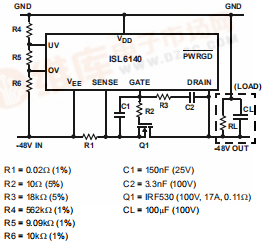

代表性系统的典型值

假设:

36V至72V供电范围;48标称值;紫外线=37V;紫外线=71V

1A典型电流消耗;2.5安培过电流

负载电容(CL)的100μF;等效RL为48Ω

(R=V/I=48V/1A)

R1:0.02欧(1%)

R2:10欧(5%)

R3:18千欧(5%)

R4:562kΩ(1%)

R5:9.09kΩ(1%)

R6:10kΩ(1%)

C1:150nF(25V)

C2:3.3nF(100伏)

问题1:IRF530(100伏,17安,0.11欧)

应用程序:快速选择指南

分量值

(参考框图)

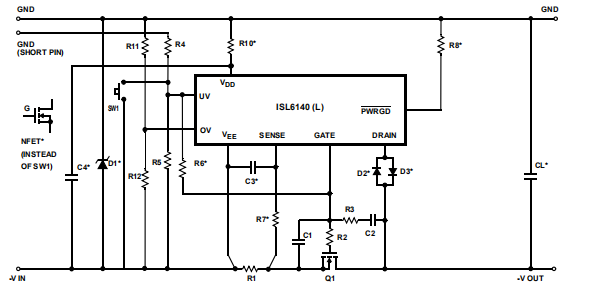

本节将描述所需的最小组件对于典型的应用程序,将演示如何选择组件值。(注意,“典型”值只能是很适合这个应用程序;用户可能必须选择一些与系统匹配的组件值)。每个街区然后详细解释它是如何工作的,以及选择。

R4,R5,R6-一起设置欠压(紫外线)和过压(OV)触发点。当电源上升时向下,这些跳闸点(和它们的标称20毫伏滞后)将决定何时允许闸门开启关闭(UV和OV不影响PWRGD输出)。输入电源被划分为引脚等于跳闸点(标称值为1.223V)比较器将切换。

VUV=1.223(R4+R5+R6)/(R5+R6)

VOV=1.223(R4+R5+R6)/(R6)

R4=562K、R5=9.09K和R6=10K的值将给出UV=37V和OV=71V的触发点。

Q1-是将输入电源电压连接到正确启用时的输出负载。它需要被选中基于以下几个标准:最大期望电压输入电源(包括瞬态)以及输出端;期望的最大电流;功率消散和/或安全操作区注意事项(到期对于快速过流锁存器,功耗通常是与电流限制为使用;但是,最坏情况下的功率通常是低于过电流停机)。其他注意事项包括影响rDS的门电压阈值(开)(反过来,在正常运行),以及允许的最大栅极电压(IC钳位输出钳位至~14V)。

R1-是过电流检测电阻器;如果输入电流为足够高,使得R1上的电压降超过感应比较器跳闸点(标称50mV),栅极引脚将变低,关闭场效应管,以保护负载过大的电流。R1的典型值为0.02Ω;这是设置过电流跳闸点I=V/R=0.05/0.02=2.5A。因此,要选择R1,用户必须首先确定在哪个级别它应该会跳闸。考虑到最坏的情况跳闸点的变化(50mV±10mV=±20%)和R1抗性(通常为1%或5%)。注意在正常情况下在这种情况下,电阻上会有电压降(V=IR),所以电阻值越高电压降。还应注意,应设置过电流高于励磁涌流水平(加上负载电流);否则,它将在这段时间内锁定(另一种方法是进一步降低浪涌电流)。一个经验法则是过电流比正常电流高2-3倍。R1=V/Ioc=0.05V/Ioc(典型值=0.02Ω)

CL-是所有负载电容的总和,包括负载的输入电容本身。它的价值通常由负载电路的需要,而不是热插拔(尽管可以有互动)。例如,如果荷载是调节器,则电容可根据该电路的输入要求(在电流尖峰或负载、滤波噪声等)选择会影响励磁涌流的控制方式。注意,对于调节器,可能有电容器也在那个电路的输出端;需要添加这些在涌流过程中的电容计算(除非调节器被PWRGD信号延迟工作,例如)。RL-是负载的等效电阻值;它确定通过场效应晶体管。它也会影响一些动态条件(例如断电时负载电容器的放电时间。典型值可能为48Ω(I=V/R=48/48=1A)。R2,C1,R3,C2-与门驱动器有关,因为它控制涌流。

R2防止高频振荡;10Ω是典型的价值。R2=10欧姆。R3和C2作为反馈网络控制涌流当前。I涌流=(Igate*CL)/C2,其中CL是荷载电容(包括模块输入电容)和Igate是栅极引脚充电电流,名义上为45微安。所以选择系统可接受的涌流值,然后解决指挥与控制。所以I=45微安*(CL/C2)。或C2=(45μA*CL)/I。C1和R3防止Q1在先通电。如果没有他们,指挥控制系统就会打开大门电压约等于v*C2/Cgs(Q1)(其中Cgs是FET栅源电容)在ISL6140可以通电并主动拉低栅极。地点C1与Q1的栅极电容并联;隔离它们从C2到R3。C1=(Vinmax-Vth)/Vth*(C2+Cgd)-其中Vth是场效应管的最小栅阈值,Vinmax是最大值工作输入电压,Cgd是FET栅漏电容。R3=(Vinmax+deltaVgate)/5mA-其值不重要;a典型值为18kΩ

应用:涌流ISL6140热插拔控制器的主要功能是控制励磁涌流。当电路板插入带电背板,板电源的输入电容器供电电路可以产生大电流瞬变充电。这可能会导致系统电源出现故障供应(可能影响其他板!),也可能是对电源造成永久性损坏。让电路板插入现场的关键然后,背板将在控制方式,通常通过限制允许的电流流过场效应管开关,直到输入电容完全充电。在那一点上,场效应管完全打开,最小的通过它的电压降。除了控制浪涌电流外,ISL6140还保护电路板不受过电流、过电压、欠电压的影响,当输出电压在预期范围(PWRGD)。注意,虽然这个集成电路是为-48V系统设计的,但是也可用作正极48V的低压侧开关系统;操作和组件通常相似。一个可能的区别是可能需要将逻辑信号与紫外线输入接口(重置锁存)或PWRGD输出。例如,许多集成电路功能参考IC基板,连接到V形销。但这个引脚可能被认为是-48V或GND,取决于系统的极性。输入或输出逻辑(在5V或3.3V或更低电压下运行)可能是外部参照集成电路的VDD或VEEGND的

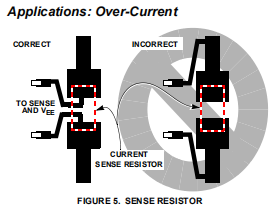

R1感测电阻器的物理布局是避免假过电流发生的可能性。因为它在主输入输出路径,跟踪应该很宽足以支持正常电流过电流跳闸点。理想情况下,R1之间的跟踪路由电阻器和ISL6140/ISL6150(针脚4(V形)和针脚5(感应)是直接的,并且在零电流的情况下尽可能短从意义上讲。(见图5)。比较器上有一个短滤波器(标称值为3微秒);电流短于此的峰值将被忽略。再长一点脉搏就会关闭输出,要求用户关闭电源系统(低于紫外线电压),或将紫外线管脚拉到触发点(通常与外部晶体管)。如果预期电流脉冲超过3微秒,则需要要过滤,则额外的电阻器和电容器可以添加。如图29所示,R7和C3充当低通滤波器,以使感测管脚上的电压不会上升同样快,有效地延迟了关闭。自从ISL6140/ISL6150在检测引脚,不存在与额外的电阻。建议R7较小,100Ω为a价值很高。延迟时间由增加的RC时间近似常数,由相对于触发点的因子修改。t=-R*C*ln[1-(V(t)-V(t0))/(Vi-V(t0))]

其中V(t)是跳闸电压(名义上为50mV);V(t0)是检测电阻上的标称电压降过电流条件;Vi是施加过电流时检测电阻。例如:一个系统有一个正常的1A电流负载,和20mΩ感应电阻器,用于2.5A过电流。它需要滤除5A时50微秒的电流脉冲。因此,

V(t)=50mV(根据规范)

V(t0)=20毫伏(V=IR=1A*20毫欧)Vi

=100mV(V=IR=5A*20mΩ)

如果R7=100Ω,则C3约为1μF。

注意,场效应晶体管必须额定以处理更高的电流更长的时间,因为集成电路不做电流限制;RC只是在延迟过电流关机。

应用:OV和UVUV和OV输入管脚是高阻抗的,所以对于输入电流。因此,下一步要考虑的是电流;电阻总是吸取电流,等于电源电压除以R4+R5+R6的总和;因此应选择足够高的值以获得可接受的当前。但是,在一定程度上电源可以传输到引脚,电阻值可能会被选在较低的位置。从紫外线到如果某些瞬态需要被过滤掉。(注意,即使是一些瞬变暂时关闭大门可能恢复得足够快这样栅极或输出电流甚至看不到中断)。

最后,考虑电阻值是否现成的,或需要定制的。公差建议精度为1%。注意,对于一个典型的48V系统(36V至72V范围),36V或72V被分成1.223V,一个显著的比例因子。对于紫外线,这个比率大约是30倍;每3毫伏改变一次紫外线管脚表示电源的大约0.1V变化电压。相反,误差为3mV(由于电阻器,例如)导致电源跳闸的误差为0.1V要点。OV比在60左右。所以电阻起作用。比较器的滞后(标称20毫伏)也是乘以紫外线管脚的比例因子30(30*20mV=0.6V电源滞后)和60对于OV引脚(60*20mV=1.2V的滞后功率供应)。对于这三个电阻,紫外方程基于简单电阻分压器:1.223=真空紫外*(R5+R6)/(R4+R5+R6)或VUV=1.223(R4+R5+R6)/(R5+R6)同样,对于OV:1.223=VOV*(R6)/(R4+R5+R6)或VOV=1.223(R4+R5+R6)/(R6)

注意,有两个方程,但有3个未知数。因为在比例因子中,R4必须比另一个大得多2;首先选择其值,以设置当前值(例如,50V/500kΩ引出100微安),然后另两个将进入10kΩ范围。在两个未知数下解这两个方程。注意,可能需要一些迭代来选择值符合要求,并且随时可用标准值。

建议使用三个电阻器(R4、R5、R6)大多数情况下采用的方法。但如果可接受的值不能找到,然后考虑两个单独的电阻分压器(一个用于每个管脚;从VDD到VEE)。这也允许用户单独调整或微调任一触发点。注意,电阻分配器的顶部如图所示29作为接地(短销)。在插卡系统中插入背板(或插脚插入的任何其他情况用户可能需要引脚接触顺序的优点。通常情况下,卡两端的插针先接触(尽管你可能不知道哪一端是第一个)。如果你把它结合起来在中心附近指定一个引脚作为短引脚GND,把它比其他的短一点,那么它应该是最后一个触针。

这样做的好处:VDD和VEE-pin首先进行连接。集成电路通电了,但是电阻分压器的顶部仍然打开,紫外线和OV销被拉低到VEE,这将保持门关闭。这允许IC时间初始化,也允许为任何输入电容充电的电源。由电阻分压器接触电源的时间卡上的电压大概是稳定的,而IC准备好响应;当紫外线针到达适当位置时电压,集成电路将打开场效应晶体管的栅极,并启动可控涌流充电。

注意,这不是一个要求;如果IC在和其他一样,它应该能够合理控制励磁涌流。但如果更好的控制是需要考虑的变量有很多:连接器中的管脚数;管脚的长度;以及插针与连接器接口中的机械间隙量;相对于较短的针长,额外的时间量输入电容量与功率的关系供应以收取费用;制造成本加法器(如有)不同长度的针;等。

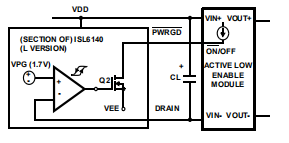

应用:PWRGD/PWRGDPWRGD/PWRGD输出通常用于直接启用电源模块,如DC/DC转换器。这个PWRGD(ISL6140)用于有源低电平模块启用(L版本);对于活动的高启用(H版本)。模块通常有一个上拉设备内置,以及内部夹具。如果没有,一个可能需要外部上拉电阻器,因为输出是打开排水管。如果不使用销,可以保持打开状态。对于这两种版本,PG比较器比较了漏极pin到VEE(连接到FET源);如果电压降超过VPG(1.7V标称值),这意味着场效应管的压降太大,PWRGD管脚应该启动(电源不好)。ISL6140(L型;图6):正常情况下(排水<VPG),Q2 DMOS将打开,拉动PWRGD低,启用模块。

当排放过高时,第二季度的DMO将关闭(高阻抗),销将被外部模块(或可选的上拉电阻器或等效),禁用模块。如果上拉电阻器使用时,它可以连接到任何电源电压超过高端IC引脚的最大额定值,但是高到可以接受的逻辑水平发出它正在行驶的信号。可以使用外部夹来限制范围。

PWRGD还可以驱动光耦(例如4N25),如图7或LED(图8)所示。两者都有情况下,当电源良好时,它们处于开启(活动)状态。电阻器根据电源电压选择R12或R13,以及负载所需的电流量。

ISL6150(H版;图9):正常情况下(排水<VPG),Q3 DMO将开启,短路内部电阻底部转向,并关闭Q2。如果外部模块的上拉电流足够高,6.2kΩ电阻器上的电压降看起来像逻辑高(相对于漏极)。注意,模块仅指排水管,不是V型(但在正常情况下,场效应管打开了,漏极和V型管几乎一样电压)。

当漏极电压高于VPG时,Q3DMOS关闭,电阻器和Q2夹住PWRGD管脚到一个二极管的电压降(~0.7V)高于漏极管脚。这个应该能够拉低模块上拉电流,并禁用模块

应用:门销为了保护外部FET,栅极引脚的输出内部夹持;高达80V电源,将不会高于15V(标称14V)。从约18伏降到10V,栅极电压将比电源低4V左右电压;在10V电源下,最小栅极电压为5.4V(最坏情况是-40°C)。

应用程序:可选组件除了典型的应用,还有已经提到了,还有一些其他的可能可能在特定情况下使用的组件。见图29显示了一些可能性。如果输入电源超过100伏绝对电压最大额定值,即使是短暂的瞬态,也可能导致对集成电路和其他部件造成永久性损坏在黑板上。如果不能保证,电压建议使用抑制器(如SMAT70A、D1)。当从VDD放置到板上的V形时,它将夹紧电压。当电源靠近OV或UV触发点,即门可以瞬间打开或关闭。一个可能的解决方案是通过隔离电阻,在VDD引脚上增加一个过滤帽C410兰特。R10的大值比较适合过滤,但是注意它的电压降。例如,1kΩ电阻,1毫安的IDD会有1伏通过它消散1mW。因为UV和OV比较器关于VEE供给,他们不应该受影响。但是栅极箝位电压可以通过额外电阻上的电压。

如果排水销上有负瞬变,阻塞二极管可以帮助限制注入集成电路基板。通用二极管(如1N4148)可以使用。请注意,ISL6140(L版本)需要一个二极管,而ISL6150(H版)需要两个二极管。增加二极管的一个结果是VPG电压被每一个二极管的压降所抵消。开关SW1显示为一个简单的按钮。可能是被一个活动的开关所代替,如NPN或NFET原理是一样的,将UV节点拉到其触发点以下,然后释放它(低切换)。连接NFET,用于例如,排水管进入紫外线;源转向,以及gate是输入;如果它变高(相对于VEE),它将打开NFET,紫外线被拉低。只要确保NFET与电阻分压器相比,电阻较低,因此对它没问题。R8是PWRGD的上拉电阻,如果没有其他的用作上拉装置的部件。R8的值是取决于当拉低时你需要多少电流(也受VDD电压的影响);你想拉它低到一个好的逻辑低水平。LED也可以如果需要,与R8串联。在这种情况下,标准是LED亮度与电流的关系。R7和C3用于延迟过电流关机,如在OV和UV部分中描述。

应用:“砖头”调节器使用的典型负载之一是直流/直流调节器,一些通常被称为“砖头”监管机构(部分原因是形状,因为它可以被视为“积木”一个系统)。对于给定的输入电压范围,有通常是不同输出电压和当前范围。也有各种标准尺寸从最初的“满”砖块开始越来越小(半砖和四分之一砖现在普通)。其他常见功能包括:所有组件(除一些滤波电容器外)独立于模压塑料包装.连接用外销通常是一个使能输入管脚来打开或关闭它。一个热插拔集成电路,例如ISL6140,经常被用来将能量传送到砖块上,以及打开它。许多砖块都有两个可用的逻辑极性(启用Hi或低输入);选择ISL6140(L版本)和ISL6150(H版本)匹配。他们之间没有什么区别,尽管L版本的输出通常更易于接口。使能输入通常有一个上拉电阻或电流源,或内置的等效设备;必须注意给定电流将创建的ISL6150(H版本)输出足够高的输入电压(记住RPG 6.2kΩ电阻器产生高电压电平;参见图9)。

选择砖块的输入电容来匹配其系统要求,如过滤噪音,以及在不同负载下保持调节。注意这个输入电容显示为ISL6140/ISL6150。砖的输出电容也由系统,包括负载调节注意事项。然而,它会影响ISL6140/ISL6150,具体取决于启用。例如,如果PWRGD信号不用于启用砖块时,可能会发生以下情况。期间的某个时候主电源启动时的浪涌电流时间给砖块输入电容充电,砖块本身就会启动工作,并开始对其输出电容器和负载充电;该电流必须加到涌流中。在一些情况下,总和可能超过过电流关机,这会关闭整个系统!因此,只要可行,使用PWRGD是有利的输出以保持砖块关闭,至少直到输入上限充电,然后启动砖块为其输出充电。典型的砖块调节器包括Lucent等型号JW050A1-E或Vicor VI-J30-CY。这些是标称-48V输入,和5V输出,输入之间有一定的隔离以及输出。

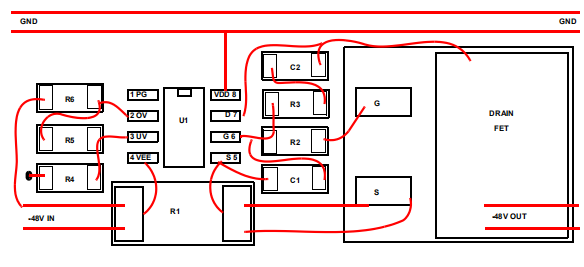

应用程序:布局注意事项对于最小应用,只有6个电阻,2个电容器,一个集成电路和一个场效应管。示例布局如所示图30。它假设集成电路是8-SOIC;场效应管是D2PAK(或类似的SMD-220包装)。虽然GND平面在多层印刷电路板中很常见一个-48V系统,-48V轨道(输入和输出)动作更像是GND而不是顶部的0V轨道(主要是因为IC信号主要参考下轨)。所以如果每个电压的单独平面不是一个选项,请考虑首先确定底部轨道的优先级。注意,在所示的位置上,大多数信号线都很短,应该不会有太多的相互作用他们。尽管集成电路电源引脚上的去耦电容器通常情况下,建议不要使用此应用程序需要一个,甚至不能容忍一个。首先,脱钩cap会增加(或被其他任何输入淹没)电容;当电源应用。但更重要的是,没有高速任何)需要调节的IC输入信号。如果仍然需要时,考虑隔离电阻R10,如图29

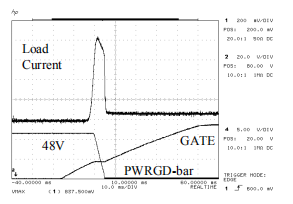

涌流

在图26的例子中,电源电压为48V负载电阻(RL)为620Ω,持续约80毫安。负载电容为100μF(100V)。感测电阻器(R1)为0.02Ω(跳闸点为2.5A;远高于此处的励磁涌流)。注意,负载电流从0开始(FET断开);达到当栅极电压逐渐升高并开启时,~850mA的峰值场效应管缓慢地,然后在80毫安时稳定下来,一旦CL完全充电到48V。浪涌电流的宽度脉冲宽度为8毫秒。作为比较,同样条件,但没有栅控场效应管,电流在130微秒的脉冲中超过20A。

电源斜坡

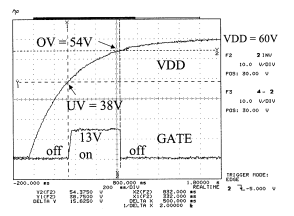

图27显示了电源电压(到VDD引脚,关于V形销处的接地)上升。在这个例,选择的值为R4=562K;R5=5.9K;R6=13.3K;将紫外线触发点设置为38V左右,并且OV触发点为54V。注意门从0V开始,并且保持在那里,直到超过紫外线触发点(38V);然后坡道(根据所选外部组件缓慢)高达13V左右,夹持在那里;直到电源在54V(门)时超过了OV跳闸点关机比开机快得多)。总时标是2秒;VDD斜坡速度只是基于所用特定电源的固有特性。2.3A时的过电流

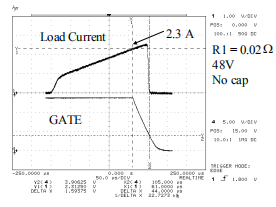

在图28中,电子负载发生器用于增加负载电流;空载电阻或电容器有联系的。感测电阻器R1为0.02Ω;这应该使标称过电流跳闸点为2.5A。栅极很高(钳制在13V左右),保持当电流开始从零上升时,场效应管打开当负载降低时,栅极开始变低(关闭场效应晶体管)电流达到2.3A。注意,栅极只需44微秒关闭场效应管(当负载电流等于零时)。请记住,感测电阻器的公差(1%和IC过电流跳闸电压(VCB)影响触发点的准确性;这就是为什么触发点不必须等于2.5A设计目标。涌流铜

可选组件(应在何时使用,请参阅文本)D1是电压抑制器;SMAT70A或同等产品。D2和D3是漏极二极管;ISL6150(H型)使用D2和D3;ISL6140(L版)仅使用D2。如果两者都不是用来连接将销排放到C2和Q1。1N4148是典型的二极管。SW1是一个按钮开关,可以手动重置过电流关机后的故障锁存。也可以是换成晶体管开关。R10和C4用于过滤VDD电压,以便输入电源上的小瞬变不会触发UV或OV。R7和C3用于延迟过电流关机。7兰特如果不使用,应该短路。见过流部分更多细节。

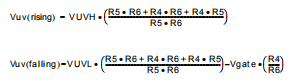

R8是PWRGD的上拉电阻,如果没有其他的用作上拉装置的部件。LED也可以如果需要,与R8串联。见图8。CL是任何额外的输出负载电容,也可以是考虑外部模块的输入电容。R6被用来增加更多的滞后到紫外线阈值,它已经有一个内置的20毫伏磁滞。有了R6有上升和下降输入的新阈值是:

由于R6直接连接到门输出,它将降低可用的栅极电流,这将降低dv/dt通过MOSFET,从而产生浪涌电流。这个R6的值应尽可能高(大于建议500K),这样就不会拖累栅极电压低于确保MOSFET完全增强。

笔记:

1.布局比例是近似的;布线只是为了说明用途;它们不一定符合普通印刷电路板设计规则。大电流母线更宽,显示为并联线。

2.上述布局的大致尺寸为1.6 x 0.6英寸;几乎一半的面积只是场效应晶体管(D2PAK或类似的SMD-220包装)。

3.R1感测电阻器的尺寸为2512;显示的所有其他R和C为如果需要的话,他们都可以使用更小的足迹。

4.布局图上未显示RL和CL。

5.R4使用一个过孔连接到板底部的GND;所有其他路由可以在顶层。(甚至可以消除通孔,用于所有顶级路线)。

6.此处不使用PWRGD信号。

7.物料清单

R1=0.02欧(5%)

R2=10Ω(5%)

R3=18千欧(5%)

R4=562kΩ(1%)

R5=9.09kΩ(1%)

R6=10千欧(1%)

C1=150nF(25V)

C2=3.3nF(100伏)

Q1=IRF530(100伏,17安,0.11欧)