24V点击型号即可查看芯片规格书

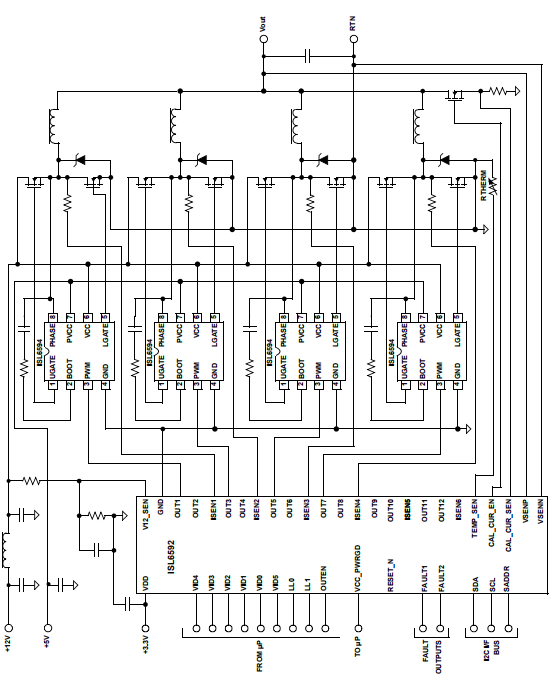

ISL6594A和ISL6594B是高频MOSFET专为驱动上下功率而设计的驱动器同步整流buck中的N沟道mosfet转换器拓扑。这些驱动程序与ISL6592数字多相降压型脉宽调制控制器N沟道mosfet形成一个完整的核心电压先进微处理器的调节器解决方案。ISL6594A驱动上栅极至12V,而下栅极栅极可以在5V到5V的范围内独立驱动12V.ISL6594B驱动上下栅极5V到12V的范围。此驱动电压提供优化应用所需的灵活性,包括门电荷和传导损耗之间的权衡。自适应零穿透保护集成到防止上下mosfet传导同时尽量减少死区时间。这些产品增加了操作过电压保护功能在VCC超过其开启阈值之前相节点连接到低压侧的栅极MOSFET(LGATE)。转换器的输出电压为然后受到低边MOSFET阈值的限制为微处理器提供一些保护,如果在初始启动期间,MOSFET短路。这些驱动器还具有一个三态PWM输入,与Intersil的多相PWM控制器一起工作,当输出关闭。这个特性消除了肖特基某些系统中用于保护负载的二极管从反向输出电压事件。

特征

同步整流桥用双MOSFET驱动器

可调栅极电压(5V至12V),以获得最佳效率

36V内部自举肖特基二极管

防止自举电容器过充

支持高开关频率(高达2兆赫)-3A下沉电流能力-快速上升/下降时间和低传播延迟

输出级关闭的三态脉冲宽度调制输入

三态脉冲宽度调制输入滞后功率排序要求

预过电压保护

VCC欠压保护

底部可膨胀铜垫,增强热量下沉

双扁平无铅(DFN)封装-接近芯片规模的封装尺寸;改善了PCB高效减薄型材

提供无铅(符合RoHS)

应用

英特尔和AMD微处理器的核心调节器

大电流DC/DC转换器

高频高效VRM和VRD

相关文献

技术简介TB363“处理和加工湿敏表面贴装器件(SMDs)“

动力传动系技术简报TB400和TB417设计、布局指南和反馈补偿

绝对最大额定值热信息

电源电压(VCC)。15伏

电源电压(PVCC)。VCC+0.3伏

启动电压(VBOOT)。36伏

输入电压(VPWM)。接地-0.3V至7V

磨损。V相-0.3VDC至VBOOT+0.3V

V相-3.5V(<100ns脉冲宽度,2μJ)至VBOOT+0.3V

藻类。接地-0.3VDC至VPVCC+0.3V

GND-5V(<100ns脉冲宽度,2μJ)至VPVCC+0.3V

阶段。接地-0.3VDC至15VDC(VPVCC=12V)

接地-8V(<400ns,20μJ)至24V(<200ns,VBOOT-相=12V)

静电放电额定值。一级JEDEC STD

推荐操作条件

环境温度范围。0°C至85°C

最大工作结温度。125摄氏度

电源电压,VCC。12V±10%

电源电压范围,PVCC。5V至12V±10%

热阻θJA(℃/W)θJC(℃/W)

SOIC封装(注1)。100牛顿/年

DFN包(注2、3)。48 7个

最高结温(塑料包装)。150摄氏度

最高储存温度范围。-65°C至150°C

最高引线温度(焊接10s)。300摄氏度

(SOIC-仅限铅头)

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

笔记:

1.θJA是用安装在自由空气中的高效热导率测试板上的元件测量的。

2.θJA是在自由空气中测量的,该部件安装在具有“直接连接”特性的高效热导率测试板上。见技术简报TB379。

3.对于θJC,“外壳温度”位置是包装底部外露金属垫的中心

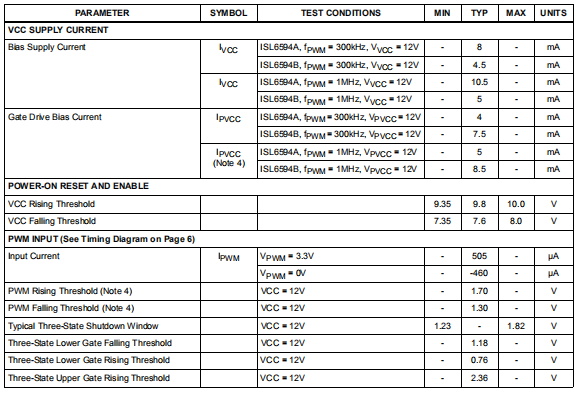

电气规范推荐的操作条件,除非另有说明。

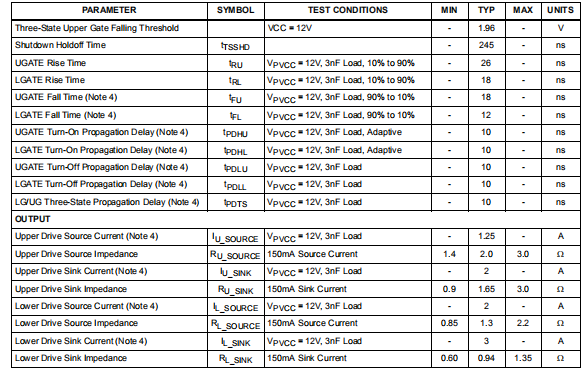

电气规范推荐的操作条件,除非另有说明。(续)

注:

4.由设计保证。不是100%的生产测试。

操作

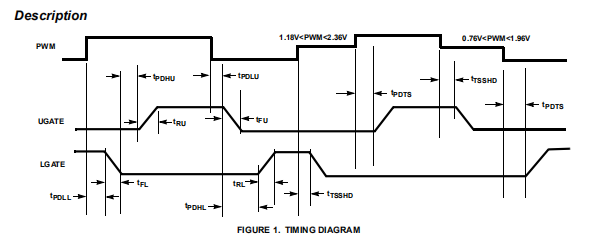

ISL6594A和ISL6594B MOSFET驱动器控制半桥动力传动系的高侧和低侧N通道FET外部提供的脉冲宽度调制信号。在VCC超过其POR水平之前,Pre-POR过电压保护功能在初始阶段激活启动;上浇口(UGATE)保持在低位闸门(LGATE),由预过电压控制保护电路,连接到相位。一旦VCC电压超过VCC上升阈值(参见电气规格),由脉宽调制信号控制门转换。脉宽调制上升沿启动关闭较低的MOSFET(见时序图)。过了一会儿传播延迟[tPDLL],较低的门开始下降。典型的跌落时间[tFL]在电气系统中提供规范部分。自适应直通电路监视LGATE电压并确定上栅极延迟时间[tPDHU]。这样可以防止上下同时进行的mosfet。一旦延误周期结束,上浇口驱动开始上升[tRU]上面的MOSFET打开了。脉宽调制的下降过渡导致上MOSFET和下MOSFET的开启。短发传播延迟[tPDLU]在大门开始倒塌。再一次,适应性射击电路决定下栅极延迟时间tPDHL。这个监测相电压和磨损电压,以及当相位降到a以下时,允许下栅极上升磨蚀电压达到一定水平取决于当前方向(参见下一节详细信息)。然后下闸上升[tRL],打开下闸MOSFET。

自适应过零死区控制

这些驱动器包含一个自适应死区时间控制使死区时间最小化,从而提高效率的技术从较低mosfet的自由转动时间减少体二极管导通,防止上下同时进行的mosfet。这是通过确保任一上升门开启具有最小和足够延迟的MOSFET已关闭。在关闭较低的MOSFET时,LGATE电压为一直监测到低于1.75V,此时传播延迟20ns后,UGATE释放上升。一旦相位很高,自适应射击就可以通过电路监测相位和磨损电压脉冲宽度调制下降沿和随后的磨损关闭。如果磨蚀电压降到相位上方小于1.75V或者相位降到小于+0.8V,则LGATE为释放以打开。

三态PWM输入

这些驱动程序和其他Intersil驱动程序的一个独特特性是在脉宽调制输入端增加一个关闭窗口。如果脉冲宽度调制信号进入并保持在关闭窗口内对于设定的延迟时间,驱动器输出被禁用,并且两个MOSFET栅极都被拉低并保持在低位。关闭当脉冲宽度调制信号移到关闭窗口。否则,PWM上升和下降电气规范中概述的阈值确定何时启用上下闸门。此功能有助于防止输出出现负瞬态关闭输出时的电压,消除肖特基二极管,用于某些系统的保护反向输出电压事件的负载。此外,超过400毫伏的磁滞也包括进入三态关断窗口消除脉宽调制由电容负载引起的输入振荡通过控制器的PWM体二极管的PWM输入上电和/或断电顺序时的输出需要驱动器和PWM控制器的偏置电源。

上电复位(POR)功能在初始启动期间,监控VCC电压上升。一旦上升的VCC电压超过9.8V(通常情况下),驱动器的操作已启用,并且脉宽调制输入信号控制栅极驱动器。如果VCC低于下降阈值为7.6V(通常),驾驶员的操作为已禁用。

预过电压保护

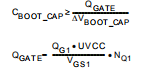

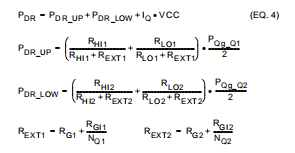

在VCC超过其POR水平之前,保持上浇口低闸和低闸由过电压控制初始启动时的保护电路。阶段是连接到低边MOSFET(LGATE)的栅极,它为微处理器提供一些保护,如果上MOSFET在初始启动时短路。为了完全保护,低侧MOSFET应该有栅极阈值远低于负载/微处理器。当VCC下降到其POR水平以下时,两个门都拉低预过电压保护电路启动,直到VCC复位。内部引导设备两个驱动器都有一个内部自举肖特基二极管。只需在开机时增加一个外部电容器相位管脚完成引导电路。鞋带还设计了防止自举电容器由于在相位节点的后缘。这会降低电压应力在引导到相位引脚上。自举电容器必须具有最大电压额定值在UVCC+5V以上,其电容值可以是从下列方程式中选择:

其中QG1是每个上MOSFET的栅极电荷量在VGS1栅极源电压下,NQ1是控制mosfet。ΔVBOOT_CAP项定义为上浇口驱动轨道允许下垂。例如,假设选择两个IRLR7821 FET作为上MOSFETs。门电荷,QG,来自数据在4.5V(VGS)栅极电源电压下,薄板为10nC。然后对于UVCC,QGATE计算为53nC(即PVCC inISL6594B,ISL6594A中的VCC)=12V。我们假设在脉宽调制周期内,驱动电压下降200毫伏。我们发现需要至少0.267μF的自举电容。

栅极驱动电压通用性ISL6594A和ISL6594B在选择栅极驱动电压进行效率优化。ISL6594A上栅极驱动器固定在VCC[+12V]上,但是下驱动轨的电压范围从12伏到5伏取决于施加到PVCC的电压。这个

ISL6594B将上下驱动轨连接在一起。

在PVCC上简单地施加5V到12V的电压

两个栅极驱动轨电压同时。

功耗

封装功耗主要是

开关频率(FSW),输出驱动阻抗

外栅电阻,以及所选的MOSFET

内部栅极电阻和总栅极电荷。精明的

所需应用的驱动器中的功耗为

对确保安全运行至关重要。超过最大值

允许的功耗水平将推动IC超过

最大建议工作结温度

125°C。最大允许IC功耗

SO8机组在室温下约为800mW,

而DFN封装中的功耗容量,

带外露散热垫,大于2W

分别为1.5瓦。DFN包更适合于

高频应用。参见布局注意事项

段为传热改进建议。

在将驱动程序设计为应用程序时,它是

建议采用以下计算方法

确保以所需频率安全运行

精选的mosfet。由于

mosfet的栅极电荷和驱动器内部

电路及其相应的平均驱动电流用等式估计。分别是2和3,

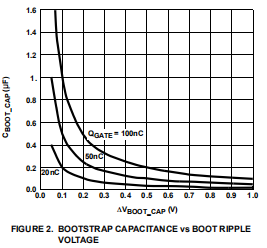

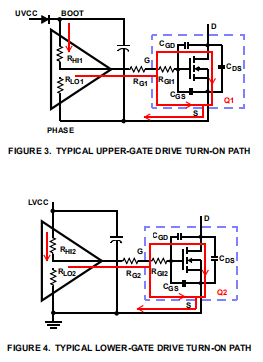

其中栅极电荷(QG1和QG2)定义为中的特定门到源电压(VGS1和VGS2)相应的MOSFET数据表;IQ是驱动器的总数两个驱动输出端无负载的静态电流;NQ1NQ2是上下mosfet的数目,UVCC和LVCC分别是分别为上、下胎。智商*VCC产品是无需电容性负载,在300kHz时通常为116mW。总栅极驱动功率损耗在沿过渡路径的电阻元件。驱动器电阻消耗了总栅极驱动功率的一部分损失,其余将由外门消散电阻器(RG1和RG2)和内部栅极电阻器(RGI1和RGI2)大多数胎儿。图3和图4显示典型的上下栅极驱动开启过渡路径。驱动器上的功耗大致可以是估计为:

布局注意事项

为了散热,把铜放在集成电路下面它是否有暴露的垫子。铜区可以是超出IC底部区域和/或通过热通孔连接到埋地铜平面。这个垂直散热孔组合,延长铜板和埋在地下的散热板使集成电路达到其全部热电势。将每个通道电源组件放置在靠近每个其他尽可能减少PCB铜损耗和PCB,寄生菌:上部FET排水管之间的最短距离以及低场效应晶体管的来源下部FET和电源接地的排水管。因此,更小正负振铃的振幅在切换相位节点的边。不过,有点空间在这两者之间,电力元件是必须的气流。从司机到FET的痕迹应该是保持短而宽以减少痕迹的电感促进清洁驾驶信号。