说明

专为便携式数字音频应用而设计。该设备集成了立体声或单声道的完整接口麦克风和立体声耳机。外部组件由于没有单独的需要麦克风或耳机放大器。

先进的片上数字信号处理性能图形均衡器、三维声音增强和自动麦克风或线路输入的电平控制。WM8750L可以作为主设备或从设备使用各种主时钟频率,包括12或24MHzUSB设备或标准256fs速率为12.288MHz和24.576兆赫。不同的音频采样率,如96kHz,48kHz,44.1kHz由主机直接产生无需外部PLL的时钟。

WM8750L在1.8V以下的电源电压下工作,尽管数字核心可以在低至

1.42V省电,所有电源的最大值为

3.6伏。芯片的不同部分也可以通电

在软件控制下。

WM8750L提供的是一个非常小和薄的5x5mmQFN包装,非常适合手持式和便携式

系统。

特征

DAC SNR 98dB(“A”加权),THD-95B,48kHz,3.3V

ADC信噪比95dB(“A”加权),THD-90dB,48kHz,3.3V

完整的立体声/单声道话筒接口

-可编程自动高度控制/噪声门

片上400兆瓦BTL扬声器驱动器(单声道)

片上耳机驱动程序

-16Ω/3.3V时输出功率大于40mW

-20mW时THD–80dB,16Ω负载时SNR 90dB

-无需直流闭锁电容器(无电容模式)

单独混合单声道输出

数字图形均衡器

低功率

-7mW立体声播放(1.8V/1.5V电源)

-14mW录制和回放(1.8V/1.5V电源)

低电源电压

-模拟1.8V至3.6V

-数字核心:1.42V至3.6V

-数字I/O:1.8V至3.6V

256fs/384fs或USB主时钟频率:12MHz、24MHz

音频采样率:8、11.025、16、22.05、24、32、44.1、48,

88.296kHz由主时钟内部产生

5x5x0.9mm QFN封装

应用

MP3播放器/录音机

AAC/WMA/多格式播放器/录音机

迷你光盘播放器/录音机

便携式数字音乐系统

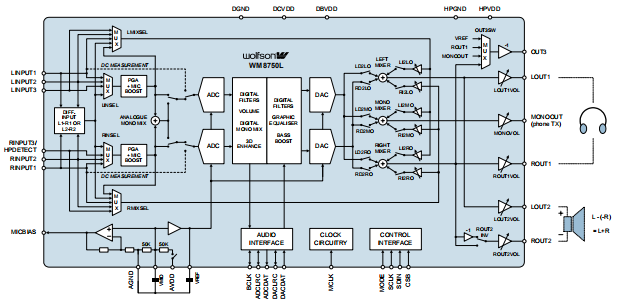

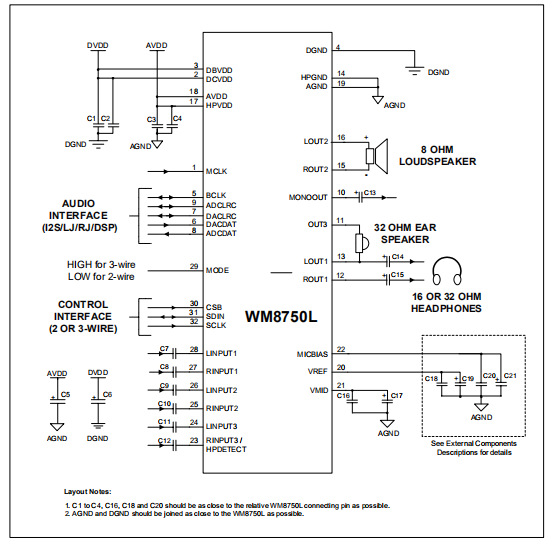

方块图

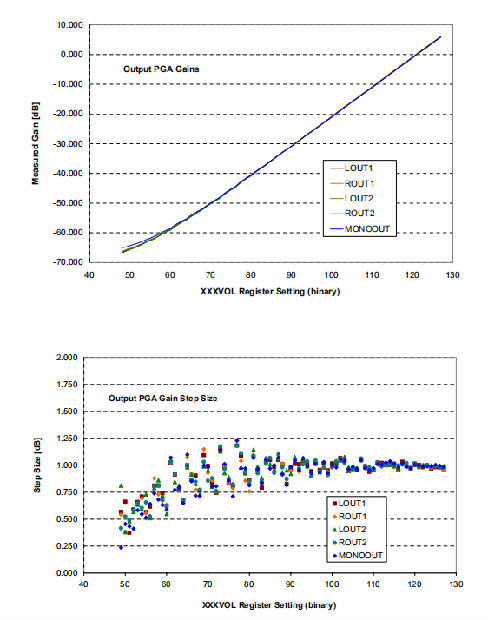

输出PGA线性度

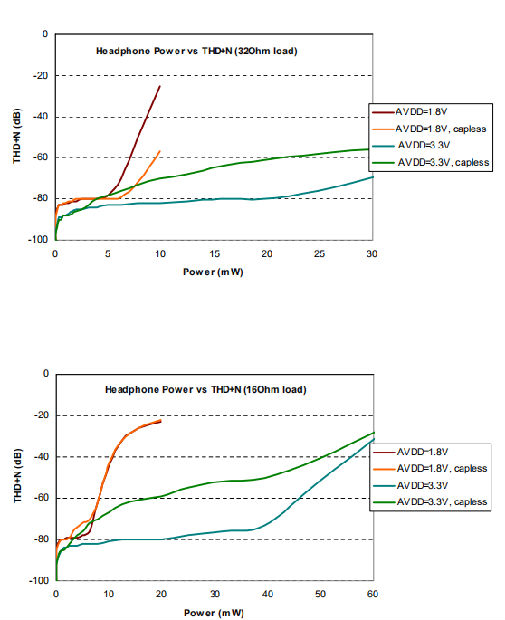

耳机输出THD与功率

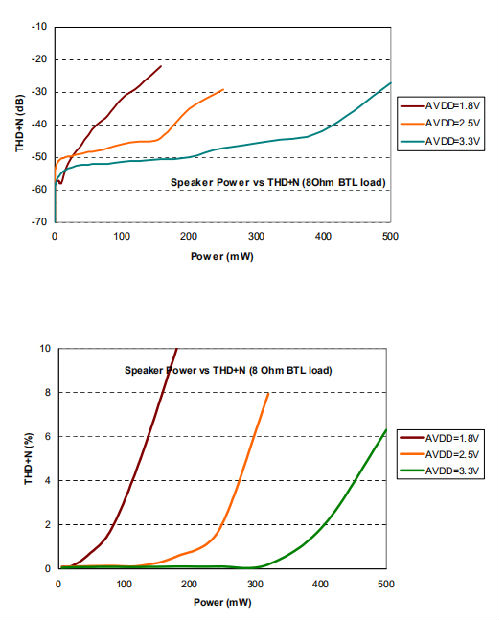

扬声器输出THD与功率

设备描述

导言

WM8750L是一款低功耗音频编解码器,提供高质量音频和高级音频的组合特点,低功耗,体积小。这些特性使其成为便携式数字音频的理想选择应用程序,如MP3和微型磁盘播放器/录音机。

该设备包括三个立体声模拟输入,可以内部切换。每个都可以使用作为线路电平输入,作为麦克风输入或作为单差分输入。一个可编程增益放大器与自动电平控制(ALC)保持记录体积恒定。

片上立体声ADC和DAC采用多位、低阶过采样,具有很高的质量以低功耗提供最佳性能的体系结构。

DAC输出信号首先进入模拟混频器,其中模拟输入和/或后ALC信号可以加上去。此混音可在线和耳机输出。

WM8750L有一个可配置的数字音频接口,ADC数据可以读取和数字音频回放数据馈送至DAC。它支持多种音频数据格式,包括I2S、 数字信号处理器模式(帧同步加上2个数据压缩字传输的突发模式),MSB优先,左先对齐和MSB,右对齐,可以在主模式或从模式下操作。

WM8750L使用了一种独特的时钟方案,可以生成许多常用的音频12.00MHz USB时钟或行业标准256/384 fs时钟的采样率。这个该特性消除了应用中对外部锁相环(PLL)的一般要求其中主时钟不是采样率的整数倍。采样率为8kHz,11.025kHz、12kHz、16kHz、22.05kHz、24kHz、32kHz、44.1kHz、48kHz、88.2kHz和96kHz生成。用于记录和回放的数字滤波器针对每个采样率进行了优化使用。

为了让全软件控制其所有功能,WM8750L提供了2线或3线MPU的选择控制接口。它完全兼容,是广泛行业标准的理想合作伙伴微处理器、控制器和数字信号处理器。

WM8750L的设计在不降低功耗的前提下表演。它在非常低的电压下工作,包括关闭软件控制的电路,包括待机和关机模式。

输入信号路径

每个通道的输入信号路径包括一个开关,用于在三个模拟输入之间进行选择,然后是PGA(可编程增益放大器)和可选的麦克风增益增强。一个也可以选择(LINPUT1–RINPUT1)或(LINPUT2–RINPUT2)的差分输入。

PGA的增益可以由用户或芯片ALC功能控制(参见自动水平控制)。

然后,信号进入一个ADC,并数字化。或者,这两个通道也可以混合在模拟域中,在一个ADC中数字化,而另一个ADC关闭。这个单声道混音信号出现在两个数字输出通道上。

信号输入

WM8750L有三组高阻抗、低电容交流耦合模拟输入,LINPUT1/RINPUT1、LINPUT2/RINPUT2和LINPUT3/RINPUT3。LINSEL和RINSEL控件比特在它们之间选择。这些输入可以配置为麦克风或线路输入,通过启用

或者禁用麦克风增益增强。差分输入,LINPUT1-RINPUT1或LINPUT2-也可以使用L/RINSEL和DS选择RINPUT。

信号输入内部偏向参考电压VREF。当线路输入为静音或设备进入待机模式时,使用特殊的防重击电路。这样可以减少更换时可能听到的任何咔嗒声输入。

WM8750L为每个通道使用一个多位、过采样的sigma-delta ADC。多位的使用反馈和高过采样率减少了抖动和高频噪声的影响。这个ADC满标度输入电平与AVDD成正比。在3.3V电源电压下,满标度电平为1.0伏r.m.s.任何大于满标度的电压都可能使ADC过载并导致失真。

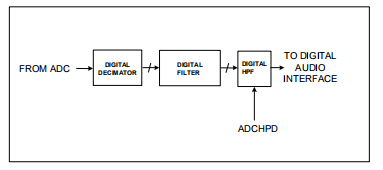

模数转换器数字滤波器

ADC滤波器执行真正的24位信号处理,以转换原始的多位过采样数据从ADC到数字音频接口上输出的正确采样频率。

来自ADC数字

ADC数字滤波器

ADC数字滤波器包含一个数字高通滤波器,可通过软件控制进行选择。高通滤波器响应在数字滤波器特性部分有详细说明。当高通滤波器启用-连续计算直流偏移量并从输入信号中减去。通过设置HPOR,当高通滤波器被禁用时,将存储最后计算的直流偏移值,并将继续从输入信号中减去。如果更改了DC偏移量,则存储除非启用高通滤波器,否则减去的值不会更改。此功能可用于校准目的。

输出数据格式可由用户编程以适应立体声或单音记录两个输入。输出信号的极性也可以在软件下改变控制。

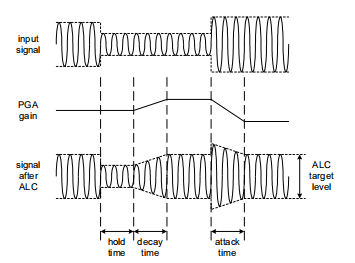

自动高度控制(ALC)

WM8750L有一个自动电平控制,旨在保持恒定的记录音量与输入信号电平无关。这是通过不断调整PGA增益来实现的ADC输入端的信号电平保持恒定。数字峰值检测器监测ADC输出必要时改变PGA增益。注意,当自动高度控制功能启用时寄存器0和1(LINVOL、LIVU、LIZC、RINVOL、RIVU和RIZC,但不包括LINMUTE和RINMUTE)被忽略。

自动高度控制操作使用ALCSEL控制位启用ALC功能。启用时,录制音量可使用ALCL寄存器在-6dB和-28.5dB(相对于ADC满刻度)之间编程。PGA增益的上限可以通过设置最大增益控制位来施加。

HLD、DCY和ATK分别控制保持、衰减和攻击时间:保持时间是检测到的低于目标的峰值电平和PGA增益之间的时间延迟开始加速。它可以编程为2(2n)次方)步进,如2.67ms,5.33ms,10.67ms等,最多43.7s。或者,保持时间也可以设置为零。只有等待时间适用于增益递增,当信号电平为高于目标。

衰减(增益递增)时间是指PGA增益在其90%范围内递增所需的时间范围(例如从-15B到27.75dB)。录制级别返回其目标所需的时间因此,值取决于衰减时间和所需的增益调整。如果收益调整很小,会比衰减时间短。衰减时间可编程为二次方)步进,从24ms、48ms、96ms等到24.58s。

攻击(增益下降)时间是PGA增益下降90%所需的时间其范围(例如,从27.75dB到-15B增益)。录制级别返回所需的时间因此,它的目标值取决于攻击时间和所需的增益调整。如果增益调整很小,会比攻击时间短。攻击时间可以是以2(2n)的幂进行编程)台阶,从6ms、12ms、24ms等到6.14s。

立体声工作时,峰值检测器取左右声道峰值的最大值值和任何新的增益设置都将应用于左右两侧的PGA,以便立体图像保存。但是,ALC功能也只能在一个通道上启用。在这种情况下,只有一个PGA由ALC机制控制,而另一个通道独立运行通过控制寄存器设置的PGA增益。

当一个ADC通道未使用或用于直流测量时,峰值检测器忽略频道。当两个ADC输出在数字域,但在进入ADC之前,如果它们在模拟域中混合成单声道,则不适用。

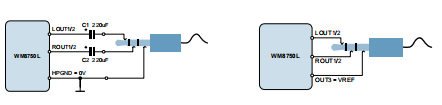

耳机输出

模拟输出LOUT1/ROUT1、LOUT2/ROUT2和OUT3可驱动16Ω或32Ω耳机负载,可以通过直流闭锁电容器,也可以通过无电容器的直流耦合。

使用直流阻塞的耳机输出电容器直流耦合耳机输出(输出3SW=00)

推荐的耳机输出配置

当使用直流阻塞电容器时,它们的电容和负载电阻一起确定下限截止频率fc。增加电容降低fc,提高低音回应。电容值越小,低音响应越小。假设16欧姆负载和C1,C2=220微F:

fc=1/2πRLC1=1/(2πx 16Ωx 220μF)=45赫兹在直流耦合配置中,耳机“接地”连接到OUT3引脚,该引脚必须通过设置OUT3=1和OUT3SW=00启用。当OUT3引脚产生直流电压时AVDD/2(=VREF),在LOUT1/ROUT1和OUT3之间没有DC偏移,因此没有DC需要阻塞电容器。这在便携式应用中节省了空间和材料成本。

建议仅将直流耦合耳机输出连接到耳机,而不要连接到另一个设备的线路输入。尽管内置的短路保护可以防止任何损坏对于耳机输出,这种连接可能有噪音,如果其他设备接地。

扬声器输出LOUT2和ROUT2可以差速驱动单声道8Ω扬声器,如下所示。

扬声器输出连接右声道通过设置ROUT2INV位来反转,以便信号通过扬声器是左右声道的总和。

线路输出

模拟输出LOUT1/ROUT1和LOUT2/ROUT2可用作线路输出。此外,OUT3和MONOOUT可通过设置OUT3SW=11(reg)用作立体声线路输出。24)并确保寄存器38和39(单声道输出混音)的内容与reg相同。34和35(忽略了混合)。推荐的外部组件如下所示。

线路输出推荐电路

直流闭锁电容器和负载电阻共同决定了较低的截止频率,指挥官。假设负载为10千欧,C1,C2=1微F:fc=1/2π(RL+R1)C1=1/(2πx 10.1kΩx 1μF)=16赫兹增加电容会降低fc,提高低音响应。C1和C2的较小值将降低低音响应。R1和R2的功能是保护线路输出不受损坏

如果使用不当。

数字音频接口

数字音频接口用于将DAC数据输入到WM8750L并输出ADC数据

从它。它使用五个管脚:

ADCDAT:ADC数据输出

ADCLRC:ADC数据校准时钟

DACDAT:DAC数据输入

ADCLRC:DAC数据校准时钟

BCLK:位时钟,用于同步

当WM8750L作为

主机,或当它是从机时的输入(见下面的主机和从机模式操作)。

支持四种不同的音频数据格式:

左对齐

右对齐

I2类

S公司

数字信号处理器模式

这四种模式都是MSB优先。它们以音频数据格式描述,如下所示。请参阅定时信息的电气特性部分。

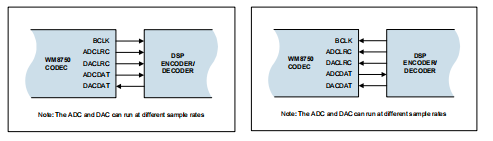

主从模式操作

WM8750L可以配置为主模式或从模式设备。作为主设备WM8750L生成BCLK、ADCLRC和DACLRC,从而控制数据的顺序在ADCDAT和DACDAT上传输。在从机模式下,WM8750L用数据来对其进行时钟响应通过数字音频接口接收。可以通过写入MS位来选择模式(请参见表23)。主模式和从模式如下所示。

音频数据格式

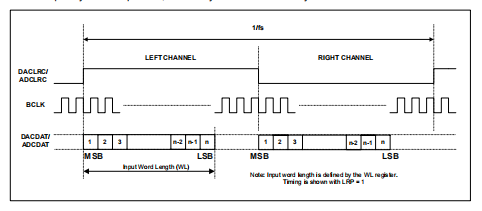

在左对齐模式下,在LRCLK之后的BCLK的第一个上升沿上可以使用MSB过渡。然后按顺序发送LSB之前的其他位。根据字长,BCLK频率和采样率,在每个LRCLK转换之前可能有未使用的BCLK循环。

左对齐音频接口(假定n位字长)

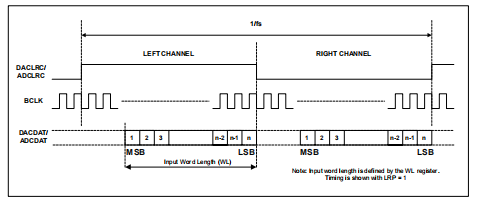

在右对齐模式下,在LRCLK之前的BCLK的最后一个上升沿上可以使用LSB过渡。所有其他位在(MSB优先)之前传输。根据字长,BCLK频率和采样率,在每次LRCLK转换后可能有未使用的BCLK循环。

右对齐音频接口(假定n位字长)在I2中

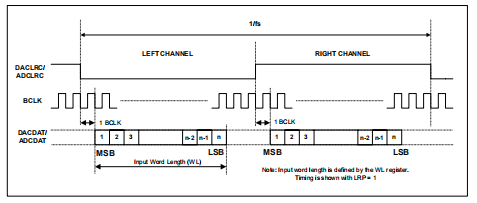

S模式下,MSB在LRCLK转换后的BCLK的第二上升沿上可用。然后按顺序发送LSB之前的其他位。根据字长,BCLK频率和采样率,一个采样的LSB和下一个的MSB。

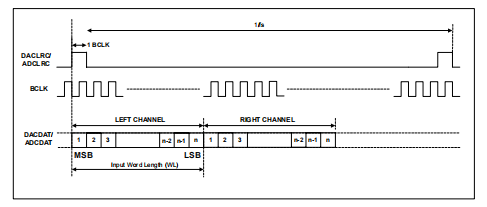

对正音频接口(假定n位字长)在数字信号处理器模式下,左通道主配电板在第一(模式B)或第二(模式A)上升时可用BCLK的边缘(可由LRP选择)跟随LRCLK的上升边缘。立即右声道数据WM8750L产品预览跟随左声道数据。根据字长、BCLK频率和采样率,可能有右通道数据的LSB和下一个样本之间未使用的BCLK循环。

数字信号处理器模式音频接口(模式A,LRP=0)

数字信号处理器模式音频接口(模式B,LRP=1)

控制接口

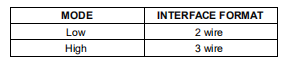

控制方式的选择WM8750L通过串行控制接口写入寄存器来控制。控制字由16位组成。前7位(B15到B9)是选择控制寄存器的地址位已访问。剩下的9位(B8到B0)是数据位,对应于每个控件中的9位登记。控制接口可以作为3线或2线MPU接口运行。模式管脚选择接口格式。

控制接口模式选择

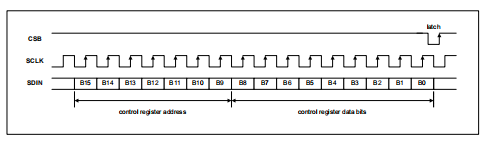

三线串行控制模式在三线模式下,SCLK的每个上升沿从SDIN管脚时钟入一个数据位。上升的边缘CSB锁存在由最后16位组成的完整控制字中。

三线串行控制接口

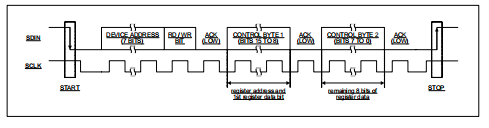

2线串行控制模式WM8750L支持通过2线串行总线进行软件控制。许多设备可以由相同的总线,每个设备都有一个唯一的7位地址(这与7位地址不同在WM8750L中的每个寄存器中)。

WM8750L仅作为从设备运行。控制器指示数据传输的开始SDIN上的从高到低转换,而SCLK保持高。这表示设备地址和接下来是数据。2线总线上的所有设备都对启动条件做出响应,并在接下来的8天内换档SDIN上的位(7位地址+读/写位,MSB优先)。如果接收到的设备地址与WM8750L的地址,R/W位为“0”,表示写入,然后WM8750L通过在下一个时钟脉冲(ACK)上拉低SDIN。如果地址未被识别或R/W位为“1”,WM8750L返回空闲状态并等待新的开始条件和有效地址。

一旦WM8750L确认了正确的地址,控制器就发送控制数据(B15到B8,即WM8750L寄存器地址加上寄存器数据的第一位)。这个然后,WM8750L通过将SDIN拉低一个时钟脉冲来确认第一个数据字节。这个然后,控制器发送控制数据的第二个字节(B7到B0,即寄存器的剩余8位数据),WM8750L再次确认,拉低SDIN。

当SDIN上存在从低到高的转换,而SCLK为高时,数据传输完成。

在接收到完整的地址和数据序列后,WM8750L返回到空闲状态,并等待另一个启动条件。如果在任何一点上检测到启动或停止条件不按顺序在数据传输过程中(即当SCLK高时SDIN改变),设备跳转到空闲状态。

-有线串行控制接口

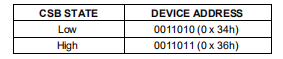

WM8750L有两个可能的设备地址,可以使用CSB引脚选择。

电源

WM8750L最多可使用四个独立的电源:

AVDD/AGND:模拟电源,为除耳机驱动器外的所有模拟功能供电。AVDD的电压范围从1.8V到3.6V,对总功率的影响最大耗电量(耳机耗电量除外)。较大的AVDD略有改善音质。

HPVDD/HPGND:耳机电源,为耳机驱动程序供电。HPVDD的范围可以是1.8V至3.6V。HPVDD通常与AVDD相连,但需要单独布局和分离抑制谐波失真的电容器。配有更大的HPVDD、更大的耳机和扬声器输出可以用较低的失真实现。如果HPVDD低于AVDD,则输出信号可能被剪断。

DCVDD:数字核心电源,为除音频和控制之外的所有数字功能供电接口。DCVDD的电压范围从1.42V到3.6V,对音频质量没有影响。这个DCVDD的返回路径是DGND,它与DBVDD共享。

DBVDD:数字缓冲器电源,为音频和控制接口缓冲器供电。就这样可以在非常低的电压下运行数字核心,节省电力,同时与其他使用更高电压的数字设备。DBVDD比DCVDD消耗更少的功率,并且对音质没有影响。DBVDD的范围从1.8V到3.6Vdgd,它与DCVDD共享。

所有四个都可以使用相同的电源电压。但是,数字和模拟电源应单独布线和解耦,以使数字开关噪声远离模拟信号路径。

应用程序信息

推荐的外部组件

推荐的外部组件图

线路输入配置

当使用LINPUT1/RINPUT1或LINPUT2/RINPUT2作为线路输入时,麦克风将增强和ALC功能通常应禁用。

为了避免剪切,用户必须确保输入信号不超过AVDD。这个在某些应用中可能需要一个分压电路。也建议移除RF使用简单的一阶RC滤波器(如高频)在任何电缆上检测到的干扰否则,输入信号中的组件可能导致音频频带中的混叠失真。交流信号在没有直流偏压的情况下,应通过直流阻塞电容器(例如1μF)馈送至WM8750L。

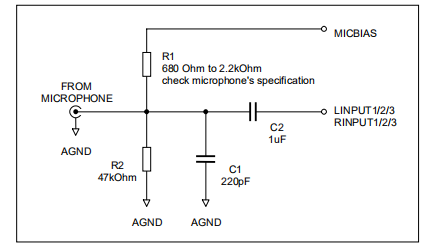

麦克风输入配置

线路输入推荐电路

对于与麦克风的接口,应启用ALC功能并增强麦克风打开。靠近扬声器嘴的麦克风通常使用13分贝的增益设置,而桌面或房间的话筒则需要提高29分贝。

推荐的应用电路如上图所示。R1和R2构成偏置网络的一部分(参见麦克风偏置部分)。只有驻极体类型才需要连接到MICBIAS的R1需要电压偏置的麦克风。R2应始终在场以防止麦克风从充电到高电压的输入可能会损坏连接上的麦克风。R1和R2

应该很大,这样就不会衰减来自麦克风的信号,因为麦克风可能有信号源阻抗大于2kOhm。C1连同麦克风的源阻抗和WM8750L输入阻抗形成射频滤波器。C2是一个直流阻塞电容器,允许麦克风在不同的直流电压下对MICIN信号进行偏置。在模拟输出端最小化弹出噪声为了在系统通电或断电时尽量减少任何弹出或点击噪声,请执行以下步骤是推荐的。

上电

打开电源。默认情况下,WM8750L处于待机模式,DAC为数字静音,音频接口、线路输出和耳机输出全部关闭(DACMU=1电源管理寄存器1和2均为零)。

启用Vmid和VREF,然后等待时间TBD根据需要启用DAC根据需要启用线路和/或耳机输出缓冲器。

将DACMU=0设置为软取消音频DAC静音。

断电

将DACMU=1设置为音频DAC软静音。

禁用所有输出缓冲区,然后等待时间待定。

关闭电源