W83194R-17点击型号即可查看芯片规格书

一般说明

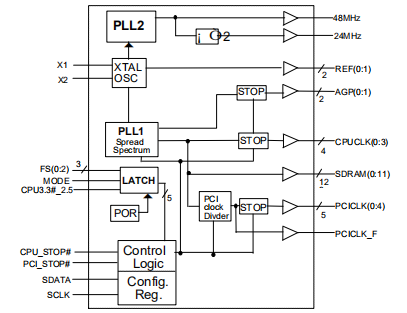

W83194R-17/-17A是一个时钟合成器,它提供高速RISC所需的所有时钟或CISC微处理器,如Intel PentiumII、PentiumPro、AMD或Cyrix。八个不同的CPU、AGP和PCI时钟的频率可通过平滑转换从外部选择。这个W83194R-17/-17A提供AGP时钟,特别是克隆芯片组。最高CPU频率W83194R-17提供的频率高达100MHz,而W83194R-17A提供的频率高达133MHz。

W83193R-17/-17A提供I2C串行总线接口,对寄存器进行编程以启用或禁用每个时钟输出并选择0.5%或1.5%中心型扩频,以减少电磁干扰。

W83194R-17/-17A接受14.318mhz参考晶体作为输入,并在3.3V电压下运行供应。高驱动PCI和SDRAM时钟输出通常提供大于1V/ns的转换速率装入30 pF负载。CPU时钟输出通常提供优于1V/ns的转换率到20pf负载保持50-5%的工作周期。固定频率输出为REF、24MHz和48MHz提供优于0.5V/ns的转换速率。

产品特点

·支持带I2C的奔腾、奔腾Pro、奔腾II、AMD和Cyrix CPU。

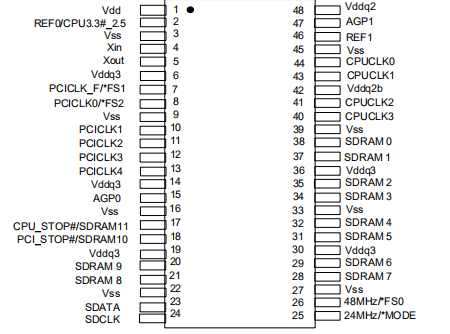

·4个CPU时钟

·12个SDRAM时钟,用于3个dim

·两个AGP时钟

·6个PCI同步时钟。

·可选单一或混合供应:

(Vdd=Vddq3=Vddq2=Vddq2b=3.3V)或(Vdd=Vddq2=Vddq3=3.3V,Vddq2b=2.5V)

·从CPU到PCI时钟的偏差-1到4纳秒,中心2.6纳秒,AGP到CPU同步。偏斜0 ns(250 ps)

·平滑频率开关,可选择60兆赫至133兆赫CPU

·I2C 2线串行接口和I2C读回

·“0.5%或-1.5%中心型扩频功能,降低电磁干扰”

·用于启用/停止每个输出和选择模式的可编程寄存器(三态或正常模式)

·电源管理模式引脚

·48兆赫USB接口

·24 MHz用于超级I/O

·48针SSOP封装

框图

引脚配置

功能描述

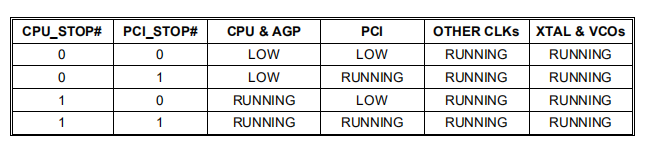

电源管理功能

所有时钟可通过2线控制接口单独启用或禁用。通电时,外部电路应允许VCO在使时钟输出能够确保正确的脉冲宽度之前稳定3毫秒。当MODE=0时,插脚18和17是输入端(PCI_STOP#),(CPU_STOP#),当MODE=1时,这些功能不可用。一个特定的时钟可以启用,因为2线串行控制接口和其中一个管脚都指示应该启用它。

根据下表,可以在低状态下禁用W83194R-17/-17A,以降低功耗。所有时钟在低状态下停止,但在从运行到停止的转换中保持有效的高周期。CPU和PCI时钟在运行和停止之间转换,其方法是等待PCICLK_F上的一个正边,然后等待感兴趣时钟上的负边,然后启用或禁用高级别的输出。

线I2C控制接口

时钟发生器是一个从I2C组件,它可以读取存储在锁存器中的数据进行验证。必须发送所有进行中的字节以更改其中一个控制字节。2线控制接口允许每个时钟输出单独启用或禁用。通电时,W83194R-17/-17A使用默认寄存器设置初始化,然后可选使用2线控制接口。

SDATA信号仅在SDCLK信号低时变化,在正常数据传输期间,SDCLK信号高时稳定。只有两个例外。一种是SDATA上的从高到低的转换,而SDCLK是用来指示数据传输周期开始的高。另一种是SDATA上的从低到高的转换,而SDCLK是高的,用于指示数据传输周期的结束。数据总是作为完整的8位字节发送,然后是生成的确认。

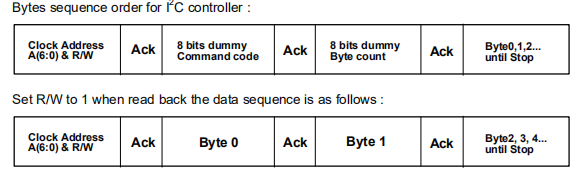

字节写入从一个开始条件开始,然后是7位从机地址和[1101 0010]、命令代码检查[0000 0000]和字节计数检查。在成功接收每个字节后,时钟芯片将在SDATA线上生成一个应答(低)。控制器可以在数据字符串之后开始写入内部I2C寄存器。顺序如下:

I2C控制器的字节序列顺序:

串行控制寄存器

Pin列列出受影响的Pin编号,@power up列给出真正通电时的状态。寄存器设置为仅在真正通电时显示的值。”指令码“字节”和“字节计数”字节必须在地址字节确认后发送。尽管这两个字节中的数据(位)被认为是“无关紧要的”,但它们必须被发送并将被确认。之后,下面描述的序列(寄存器0、寄存器1、寄存器2,…)将有效并得到确认。

电源管理时间

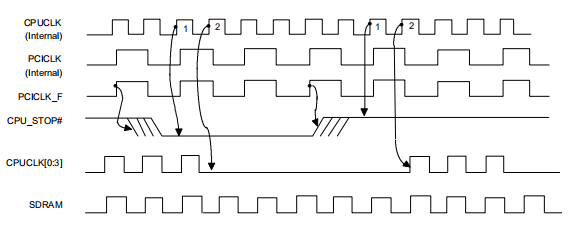

CPU停止时间图

对于同步芯片组,CPU-STOP-pin是一个同步激活的低输入pin,用于在低功耗运行时停止CPU时钟。这个pin由外部控制逻辑在自由运行的PCI时钟(PCICLK_F)的上升沿同步断言。当CPU时钟停止时,所有其他时钟将继续运行。CPU时钟将始终在低状态下停止,并以全脉冲宽度恢复输出。在这种情况下,CPU时钟延迟小于2个CPU时钟,时钟关闭延迟小于2个CPU时钟。

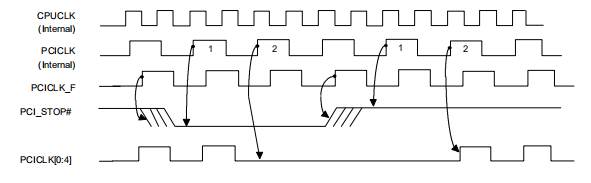

PCI停止时间图

PCICLK[0:4]。这个pin由外部控制逻辑在自由运行的PCI时钟(PCICLK_F)的上升沿同步断言。PCI时钟停止时,所有其他时钟将继续运行。PCI时钟将始终在低状态下停止,并以全脉冲宽度恢复输出。在这种情况下,PCI时钟打开延迟小于1个PCI时钟,时钟关闭延迟小于1个PCI时钟。

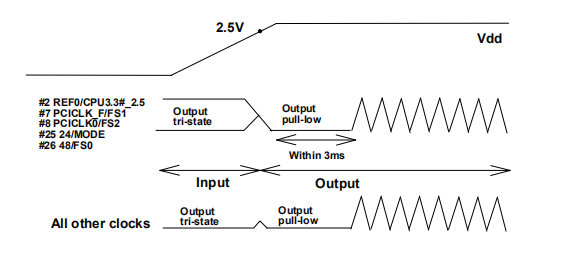

双功能销的操作

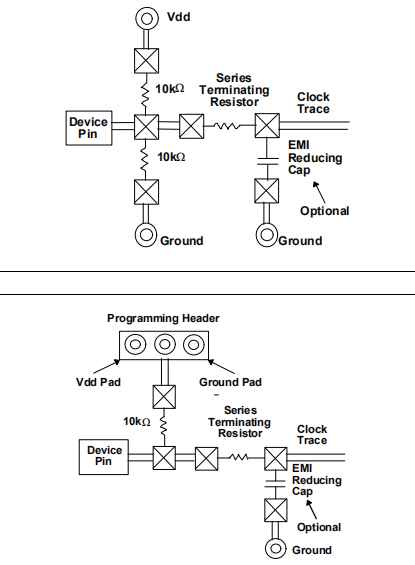

插脚2、7、8、25和26是双功能插脚,用于选择该设备中的不同功能(参见插脚说明)。通电期间,这些管脚处于输入模式(参见图1),因此被视为输入选择管脚。当Vdd达到2.5V时,这些引脚上的逻辑电平被锁存到相应的内部寄存器中。一旦正确的信息被正确锁定,这些引脚将变为输出引脚,并在默认情况下拉低。在通电计时器结束时(3 ms内),输出开始以指定频率切换。

每个引脚内部都有一个大的上拉电阻器(250 kΩ@3.3V)。默认状态为逻辑1,但当这些双功能管脚上出现长轨迹或重载时,内部上拉电阻器可能太大。在这些条件下,如果需要逻辑1,建议将外部10 kΩ电阻器连接到Vdd。否则,如果需要逻辑0,则将10 kΩ电阻器接地。10 kΩ电阻器应放在严重端接电阻器之前。请注意,这些逻辑将仅在初始通电时锁定。

如果需要可选的EMI减小电容器,则应将其放置在尽可能靠近串联端接电阻器和串联端接电阻器之后。这些电容器的典型值在4.7pF到22pF之间

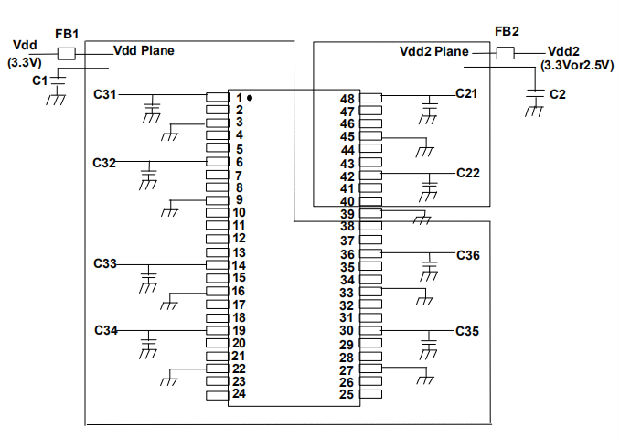

供电建议

1.应在设备周围放置一个坚固的接地平面。接地连接应尽可能短地连接到主接地平面。不得在设备周围的地平面上进行切割。

2.C21、C22、C31、C36是去耦电容器(0.1磅gF表面贴装,低ESR,陶瓷电容器)。它们应尽可能放置在Vdd引脚上,并通过接地。

3.C1和C2是低频电源噪声的电源滤波电容器。建议使用22磅/平方英尺(或10磅/平方英尺)的钽电容器。

4.建议使用铁氧体磁珠(FB),以进一步降低电源噪声。

5.到Vdd管脚的电源线必须足够厚,以便通过跟踪电阻的电压降可以忽略不计。