说明

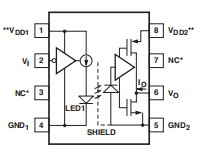

提供8针浸渍或SO-8封装类型分别是HCPL-7710或HCPL-0710光耦利用最新的CMOS集成电路技术,以极低的功耗获得优异的性能。HCPL-x710只需要两个旁路电容器完全兼容CMOS。HCPL-x710的基本构造块是CMOSLED驱动芯片、高速LED和CMOS探测器集成电路。一个CMOS逻辑输入信号控制LED驱动器IC,为LED提供电流。探测器集成电路集成了一个集成光电二极管跨导放大器和电压比较器有一个输出驱动器。

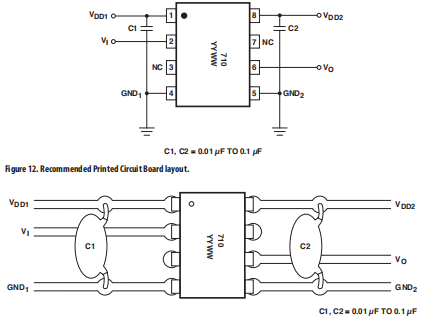

插脚3是内部LED的阳极,必须保留未连接以保证数据表性能。引脚7未在内部连接。必须连接0.1μF旁路电容器插脚1和4之间,以及插脚5和8之间。

特征

+5 V CMOS兼容性

8 ns最大脉宽失真20纳秒最大支柱。延迟偏差高速:12 Mbd40纳秒最大支柱。延迟10千伏/微秒最小共模抑制-40°C至100°C温度范围安全和监管批准UL认可根据UL 1577,3750 Vrms,持续1分钟根据UL 1577(HCPL-7710),5000 Vrms,持续1分钟选项020)CSA部件验收通知#5IEC/EN/DIN标准EN60747-5-5

–对于HCPL-7710选项060,VIORM=630 V峰值

–VIORM=567 V峰值,适用于HCPL-0710选项060

应用

数字现场总线隔离:设备网、SDS、Profibus

交流等离子体显示面板水平移动

多路数据传输

计算机外围接口

微处理器系统接口

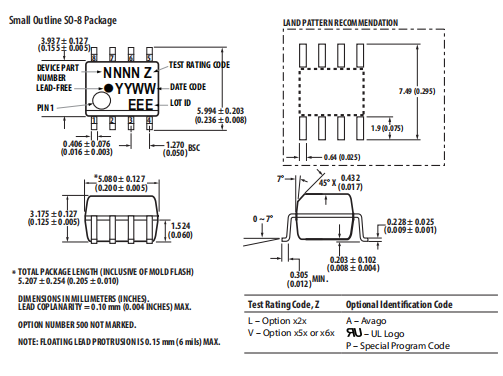

回流焊热曲线

推荐的回流条件符合JEDEC标准J-STD-020(最新版)。应使用非卤化物焊剂。

监管信息

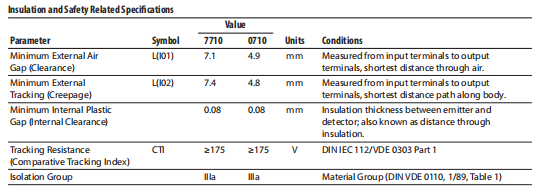

HCPL-x710已由以下组织批准:UL根据UL 1577认证,部件识别程序,文件E55361。CSA根据CSA部件验收通知5批准,文件CA 88324。IEC/EN/DIN标准EN60747-5-5

所有Avago数据表都报告了光耦组件本身固有的漏电和间隙。在确定电路绝缘要求时,这些尺寸是设备设计师需要的起点。但是,一旦安装在印刷电路板上,必须满足最小爬电和间隙要求为单个设备标准规定。对于爬电,沿印刷品表面的最短距离路径必须考虑输入和输出引线焊料嵌条之间的电路板。建议槽和肋等技术,可用于印刷电路板,以达到所需的爬电性能和间隙。爬电距离和间隙距离也会根据污染程度和绝缘水平。

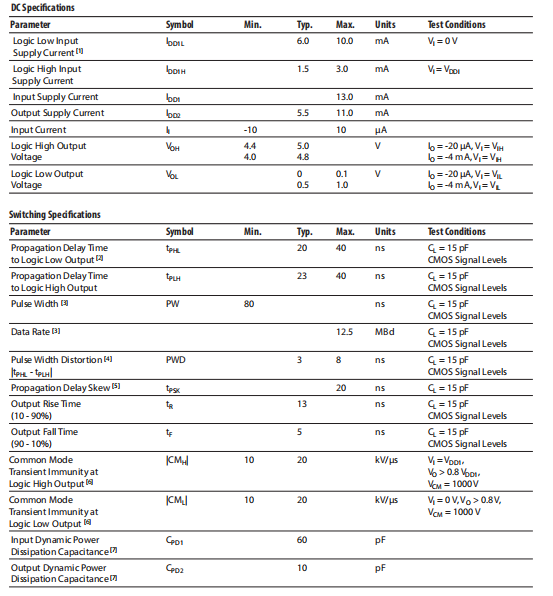

电气规范

未规定的试验条件可在推荐工作范围内的任何地方。所有典型规格均为TA=+25°C,VDD1=VDD2=+5 V。

笔记:

1.当VI当VI很高。

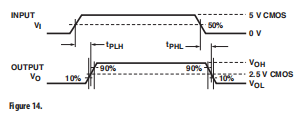

2.tPHL传播延迟是从VI下降沿的50%水平测量的信号至VO信号下降沿的50%水平。tPLH传播延迟是从VI上升沿的50%水平测量的信号至VO信号上升沿的50%电平。

3.MIMIMUM脉冲宽度是最短的脉冲宽度,可以保证10%的最大脉冲宽度失真。最大数据速率为最小脉冲宽度的倒数。在PWD和数据相关的情况下,以高于12.5 MBd的数据速率操作HCPL-x710是可能的应用程序中可以容忍抖动增加和松弛的噪声裕度。例如,如果比特宽度的最大允许变化是30%,最大数据速率变为37.5毫巴。注:Avago不保证HCPL-x710在12.5MBd以上的性能。

4.PWD定义为| tPHL-tPLH |。%PWD(脉冲宽度失真百分比)等于PWD除以脉冲宽度。

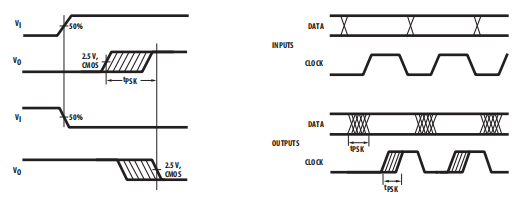

5.tPSK等于在给定温度范围内,机组之间出现的tPHL和/或tPLH最差情况差的大小推荐的操作条件。

6.CMH是在维持VO>0.8 VDD2时可以维持的最大共模电压转换率。CML是最大的共同点保持VO<0.8V时可保持的模式电压转换率。共模电压转换率适用于上升和共模电压边缘下降。

7.空载动态功耗计算如下:CPD*VDD2*f+IDD*VDD,其中f为开关频率,单位为兆赫。

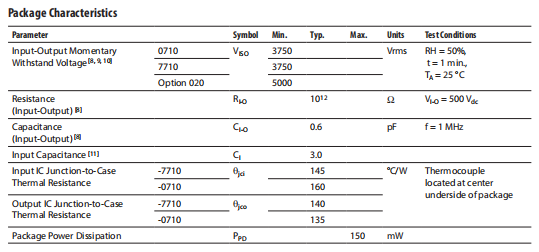

8.被认为是双端装置的装置:引脚1、2、3和4短接在一起,引脚5、6、7和8短接在一起。

9.根据UL1577,每个HCPL-0710通过施加绝缘测试电压≥4500 VRMS 1秒(泄漏检测电流限值,II-O≤5μA)进行验证测试。每个HCPL-7710通过施加绝缘测试电压≥4500 VRMS 1秒(泄漏检测电流限值,II-O≤5μA)进行验证测试。

10.输入输出瞬时耐受电压是介电电压额定值,不应解释为输入输出连续额定电压。有关连续额定电压,请参阅设备级安全规范或Avago应用说明1074“光耦输入输出持续电压。”

11.竞争情报是在引脚2(VI)处测得的电容

应用程序信息

旁路和PC板布局HCPL-x710光耦非常容易使用。不需要外部接口电路,因为HCPL-x710采用高速CMOS集成电路技术,允许CMOS逻辑直接连接到输入端和输出。如图所示,正确操作所需的唯一外部组件是两个旁路电容器。电容值应在0.01μF和0.1μF之间。对于每个电容器,两个电容器之间的总引线长度电容器端部和电源插脚不得超过20 mm。图说明了推荐的HPCL-x710的印刷电路板布局。

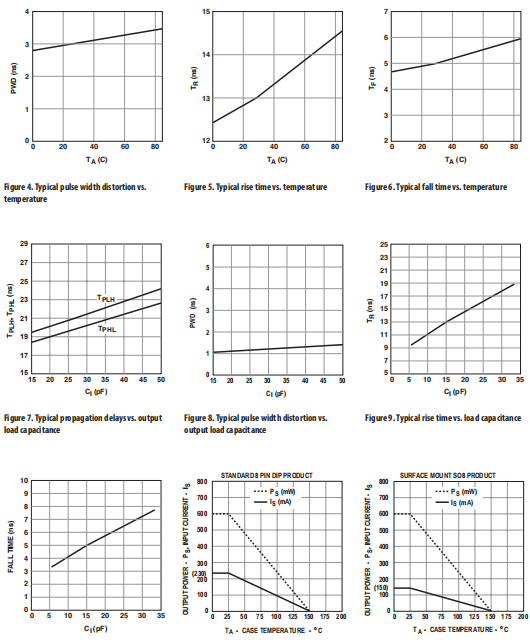

传输延迟、脉冲宽度失真和传输延迟偏差传播延迟是描述逻辑信号在系统中传播速度的一个优点。这个从低到高的传播延迟(tPLH)是输入信号传播到输出,使输出从低变为高。类似地,从高到低的传播延迟(tPHL)是输入信号传播到输出所需的时间量,使输出从从高到低。见图。

脉冲宽度失真(PWD)是TPHL和TPLH,通常决定最大数据传输系统的速率能力。PWD可以是用PWD(ns)除以传输的最小脉冲宽度(单位:ns)。通常情况下,PWD为最小值的20-30%脉冲宽度是可以接受的。PWD规范HCPL-X710在推荐的操作条件下最大为8纳秒(10%)。10%指令最大值根据三个现场总线标准中最严格的一个,现场总线。传播延迟偏差是一个重要的参数考虑在并行数据应用中,并行数据线上的信号同步是一个问题。如果并行数据通过一组光耦合器发送,传输延迟的差异将导致到达光耦合器输出的数据不同的时代。如果传播延迟的差异足够大,它将决定最大速率。哪些并行数据可以通过光耦合器发送。传播延迟歪斜被定义为对于任何给定的组,TPLH或TPHL的最小和最大传播延迟之间的差值。在相同条件下工作的光耦条件(即相同的驱动电流、电源电压,输出负载和工作温度)。如图所示在图中,如果一组光耦的输入同时打开或关闭,tPSK最短传播延迟之间的差异,无论是tPLH还是tPHL,以及最长的传播延迟,tPLH或tPHL正如前面提到的,TPSK可以确定最大值。并行数据传输速率。图是时间一个典型的并行数据应用程序的图表通过光耦合器发送的时钟和数据线。此图显示光耦合器的输入和输出。在这种情况下假设数据从时钟。

传播延迟倾斜表示边缘在发送后可能在哪里的不确定性通过光耦。图显示数据线和时钟线都不确定。这两个不确定领域不能重叠;否则,时钟信号可能会在数据输出已经确定,或者一些数据输出可能在时钟信号之前开始改变已经到了。从这些考虑来看在并行应用中,可以通过光耦合器发送的最小脉冲宽度是tPSK的两倍。谨慎的设计应该使用稍长的脉冲宽度,以确保电路的其余部分不会导致故障。HCPL-x710光耦具有以下优点传播延迟的保证规范,脉冲宽度失真和传播延迟偏差超过推荐的温度和电源范围。

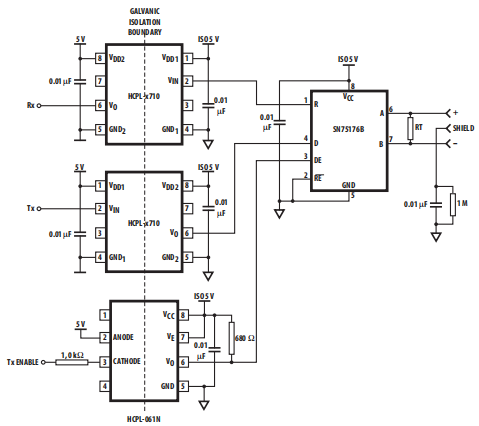

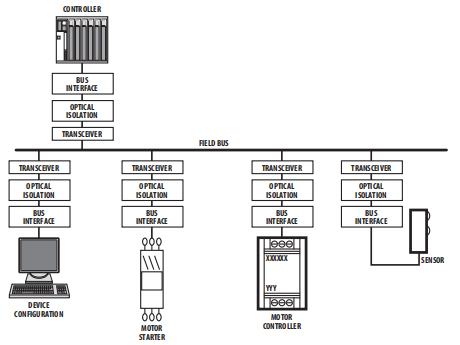

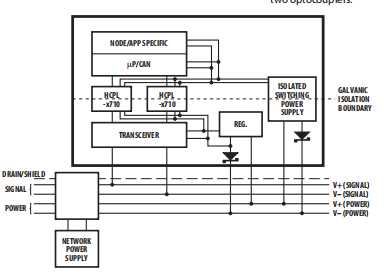

数字现场总线通信网络到目前为止,尽管它有许多缺点,4-20毫安模拟电流环已被广泛接受过程控制系统实施标准。然而,在当今的制造环境中,自动化系统有望帮助管理这个过程,不仅仅是监视它。随着降临数字现场总线通信网络,如设备网、现场总线和智能分布式系统(SDS),信息受限的时代已经一去不复返了。控制器现在可以从现场接收多个读数设备(传感器、执行器等)以及诊断信息。这些数字现场总线的物理模型通信网络非常相似,如图。每个包括一个或多个总线、一个接口单元、光隔离、收发器和传感和/或驱动装置。

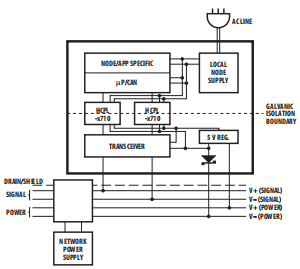

现场总线网络的光隔离为了充分认识到这些网络的好处,Avago建议使用光耦提供电流孤立。因为网络通信是双向的(包括接收和传输数据两个Avago光耦需要。通过提供电流隔离,数据完整性是消声抑伪信号。此外,网络接收最大值。防止电力系统故障和接地回路。在一个孤立的节点内,例如设备网节点如图所示,节点的一些组件是指网络的V-以外的接地。图。典型现场总线通信物理模型这些组件可以包括设备等带串行端口、并行端口、RS-232和RS-485类型港口。如图所示,来自网络的电源是仅用于收发器和光耦合器。连接到三种类型中任何一种的节点的隔离使用HCPL-x710光耦。对于每个网络HCPL-x710满足临界传播延迟和0°C至+85°C温度范围内的脉冲宽度失真要求,以及电源电压范围为4.5V到5.5V。

用HCPL-x710实现设备网和SDS传输速率高达1 Mbit/s时,两个设备网SDS基于相同的面向广播的通信协议-控制器区域网络(CAN)。建议在这些网络上使用三种类型的孤立节点:孤立节点由网络供电(图19),独立节点使用由网络供电的收发器(图20),以及为网络供电的独立节点(图21)。图18。典型的设备网节点。图19。网络供电的独立节点网络供电的独立节点这种类型的节点非常灵活,如图所示。图19被认为是“孤立的”,因为部件具有相同的接地参考。然而,所有组件仍然由网络供电。这个节点包含两个监管者:一个是独立的,为控制器、节点特定应用和隔离(节点)两个光耦的边,而另一个是非孤立的。非隔离调节器提供收发器和两个光耦。

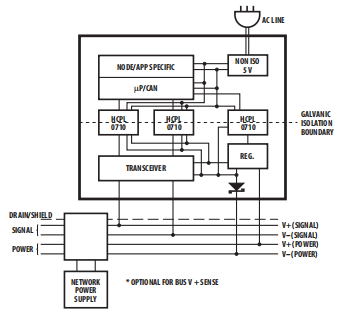

网络供电的带收发器的独立节点图20显示了由两个网络供电的节点还有另一个消息来源。在这种情况下,收发器和两个光耦合器的隔离(网络)侧是由网络提供动力。节点的其余部分是由交流线路供电,在应用程序需要大量的电源。这种方法也很理想,因为它不重负载网络。更重要的是,独特的“双反转”设计确保网络不会“锁定”如果节点的交流线路电源丢失或节点关机。具体来说,当输入功率(VDD1)到排除了位于传输路径中的HCPL-x710,确保了隐性总线状态作为HCPL-x710输出电压(VO)过高。*总线V+感应建议总线V+检测块显示在实施图20。本地供电的节点如果一个未通电的隔离物理层试图传送。总线V+感应信号将用于将DeviceNet对象的BOI属性更改为“自动复位”(01)值。参见第1卷第5.5.3节。这将导致节点持续重置,直到总线检测到电源。一旦检测到电源BOI属性将返回到“hold in bus off”(00)价值。BOI属性不应留在“自动复位”(01)值,因为这会破坏CAN错误限制的jabber保护功能。任何便宜的低频光隔离器都可以用来实现此功能。

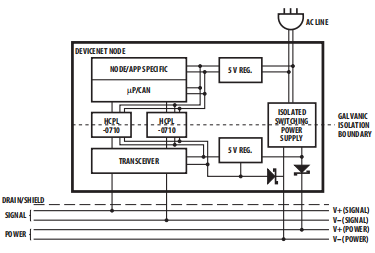

为网络供电的独立节点图21显示了向网络。交流线路为调节器供电,调节器提供局部5 V。交流线路也为隔离的24伏电源供电电源,为网络供电,再加上5伏调节器,依次为收发器和两个光耦合器的隔离(网络)侧。这个当存在一个网络上不需要的设备数强大的动力,从而消除了电源。更重要的是,独特的“双反转”设计确保网络不会“锁定”如果节点的交流线路电源丢失或节点关机。具体来说,当输入功率(VDD1)到排除了位于传输路径中的HCPL-x710,确保了隐性总线状态作为HCPL-x710输出电压(VO)过高。

电源和旁路

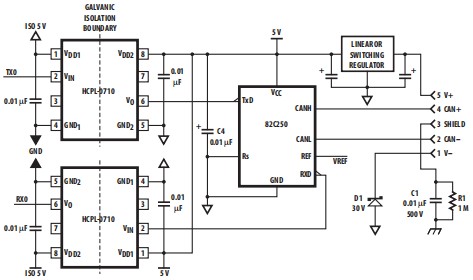

推荐的设备网应用电路是如图22所示。由于HCPL-x710与CMOS逻辑电平信号完全兼容,光耦是直接连接到CAN收发器。双旁路电容器(值在0.01至0.1μF之间)为要求且应尽可能靠近HCPLx710的输入和输出电源引脚。对于每个电容器,在电容器和电源引脚的两端不应超过20 mm。旁路电容器是由于其高速数字特性光耦内部的信号。

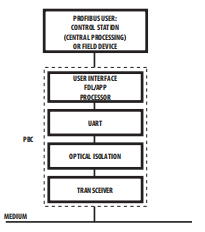

用HCPL-x710实现PROFIBUSPROFIBUS是过程现场总线的缩写,本质上是一个双绞线串行链路,与RS-485非常相似能够实现高达12毫米宽。如图23所示,一个PROFIBUS控制器(PBC)建立现场自动化的连接单元(控制或中央处理站)或字段设备到传输介质。中国人民银行包括线收发器,光隔离,帧特性发射机/接收机(UART)和FDL/APP处理器与PROFIBUS用户的接口。

电源和旁路

推荐的PROFIBUS应用电路是如图24所示。由于HCPL-x710与CMOS逻辑电平信号完全兼容,光耦直接连接到收发器。双旁路电容器(值在0.01至0.1μF之间)为要求且应尽可能靠近HCPLx710的输入和输出电源引脚。对于每个电容器,在电容器和电源引脚的两端不应超过20 mm。旁路电容器是由于其高速数字特性光耦内部的信号。与多站RS485系统非常相似HCPL-061N光耦提供传输禁用使公共汽车在每个主/从传输周期。具体来说HCPL-061N禁用线路驱动器的发送器将其置于高状态模式。另外HCPL-061N将RX/TX驱动IC切换到侦听模式。HCPL-061N提供HCMO兼容性和高CMR性能(VCM=1000 V时为1千伏/微秒)在工业通信接口中必不可少。