ADS7869点击型号即可查看芯片规格书

VECANA01点击型号即可查看芯片规格书

应用

电动机控制

说明

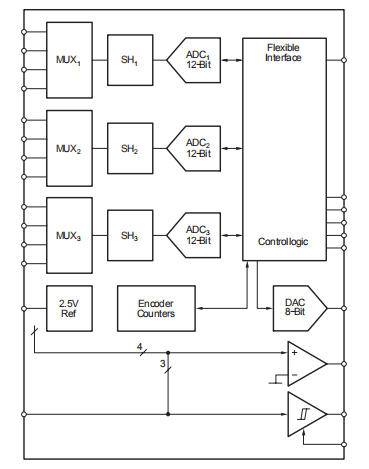

ADS7869是一个马达控制前端,包括三个模数转换器(ADC),共有七个采样和保持电容和12个全差分输入通道。有四个符号比较器连接到四个输入通道。另外还有三个全差分输入;每个输入都连接到一个窗口比较器和一个符号比较器。

此外,ADS7868还提供了一个非常灵活的数字接口,具有可配置为不同标准的并行端口。此外,还提供了串行外围接口(SPI)和具有三条数据线的专用串行接口(VECANA01模式)。这允许ADS7869与大多数数字信号处理器(DSP)或微控制器接口。该芯片专门用于电机控制应用。为了进行位置传感器分析,在硅上增加了两个上下计数器。此功能确保编码器的模拟输入与计数器值保持在同一时间点。

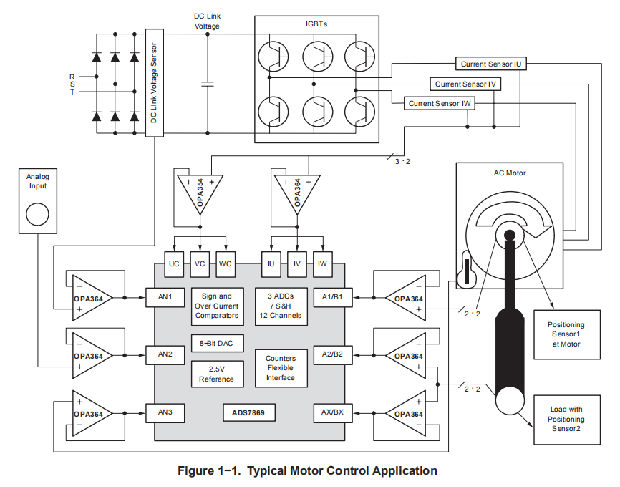

典型应用电路

图1-1显示了典型电机控制电路的示例。IU、IV和IW通道测量电机的电流。电机的位置(速度)和负载分别由A1、B1和A2、B2使用旋转变压器或模拟编码器传感器同时测量。异步输入AX和BX可以用来捕获编码器的参考信号,从而得到绝对位置。通道AN1测量差分直流链路电压。AN3测量马达的温度。辅助电压可以用通道AN2测量。计数器输入连接到适当的比较器输出(A1到CNTA1、B1到CNTB1等等)。窗口比较器的电平输入DAIN应该连接到8位DAC输出DAOUT。

模拟段

模拟部分处理模数转换器,包括增益和偏移调整。还讨论了模拟输入、七符号比较器、三窗口比较器、8位数模转换器(DAC)、参考电压、接地和电源电压。

全差分模拟输入

模数转换器输入

adc的12个输入以及比较器的3个输入(U_C、V_C和W_C)是完全差分的,在50kHz时提供60dB的良好共模抑制。这对于在恶劣环境中抑制噪声非常重要。

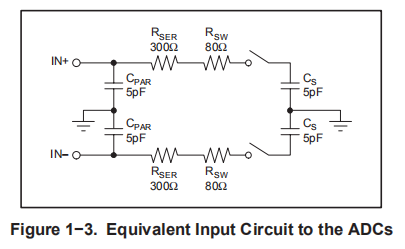

来自ADC的七个采样和保持电路包含一个5pF电容器(图1-3中的C),该电容器通过开关连接到模拟输入端。打开开关保存数据。转换完成后,开关关闭。然后,电容器被加载到初始电压,该电压等于ADC处的参考电压,该参考电压是通过增益调整选择的。

当输入开关闭合时,输入引脚的电压通常不同于样品电容器的电压。样品电容器需要在至少200ns的采集时间(t)内充电至12位精度,即最低有效位(LSB)的一半。逆商

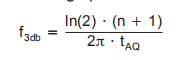

驱动运算放大器的最小-3dB带宽可以计算为:

当n等于12时,ADC的分辨率(对于ADS7869)。当t=200ns时,驱动放大器的最小带宽为7MHz。如果应用程序增加了采集时间,则可以放宽带宽。

建议使用德克萨斯仪器公司的OPA364;除了必要的带宽外,它还以低价在小包装中提供低偏移。

驱动运算放大器的相位裕度通常由ADC的采样电容来减小。电容器和放大器之间的电阻降低了这种影响;因此,内部300Ω电阻(RSER)与开关串联。闭合开关(RSW)的电阻约为80Ω。见图1-3。

ADC的差分输入范围(正负输入)是±REF_ADC,转换器的基准,通过增益调整选择。

重要的是,所有输入端的电压不得超过模拟电源上方0.3V或地面下方0.3V。输入端没有直流电流。只有在给样品和保持电容器充电时,才需要电流。

窗口比较器输入

为窗口比较器选择了一种采样结构。采样时间为两个时钟周期,最小t(见方程式1)为125ns。必要的精度为10毫伏(见8位DAC部分),输入范围为5伏。驱动放大器所需带宽为8.8MHz(见方程式1)。建议使用德克萨斯仪器公司的OPAx354。

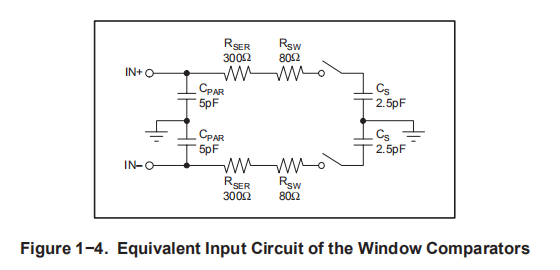

窗口比较器的输入电路类似于ADC输入。唯一的区别是采样电容器降低到2.5pF。(见图1-4。)

符号比较器输入

四个符号比较器连接到ADC输入端(A1、B1、A2和B2);三个符号比较器连接到窗口比较器输入端(U_C、V_C和W_C)。

adc和窗口比较器的采样电容会产生电压故障,因此,低阻抗输入的驱动是非常重要的。

差分输入的较低电压应保持在0至AV−1.8V的范围内。

模数转换器

ADS7869包括三个SAR型1MSP、12位ADC和三对S/H电容器,它们分别连接到ADC1和ADC2。单个S/H电容器连接到ADC3。增益和偏移调整被添加到每个ADC。(

保持1,保持2

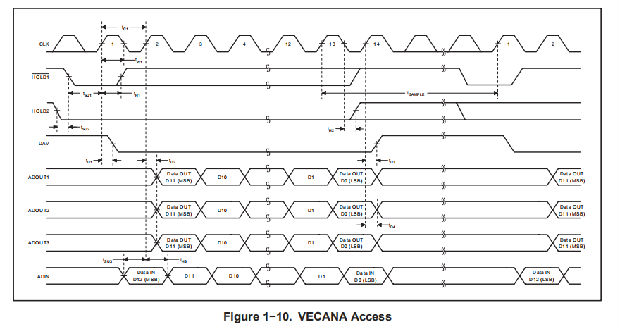

当HOLDx信号变低时,模拟输入保持不变。同步器的电荷样品和货舱(S/H)冻结在货舱1的下降沿上。相对于系统时钟的上升沿,HOLD1的设置时间通常为25ns。转换将在时钟的下一个上升沿自动开始。转换完成后,S/H切换回采样模式,12时钟1-5个以后循环。这个时间点由DAV表示。(参见第26页图1-10。)转换开始后,HOLD1最迟必须在第13个下降时钟处升高。

异步采样和保持(S/H)由激活的低保持2信号触发。设置时间6-7个紧靠支架1下降边缘的支架2为0ns;见图1-10。当通过数字接口选择这些S/H电路并且HOLD1信号变低时,这些S/H电路的转换被启动。当HOLD2信号变高时,输入端被连接回S/H电容器。在整个转换过程中HOLD2需要低。可以将保持架1和保持架2连接在一起。

时钟

ADC使用外部时钟CLK,它需要在1MHz到16MHz的范围内。转换需要12个时钟周期,采集至少需要4个时钟周期。因此,1MSPs的最大吞吐率是以16MHz时钟和每个完整转换周期的16个时钟周期来实现的。占空比应为50%;但是,ADS7869仍将正常工作,占空比介于30%和70%之间。

复位

重置条件停止任何正在进行的转换,并将同步S/Hs重新连接到输入;请参阅重置部分。

增益调整

12位DAC(REF_ADC)的输出用作ADC的参考电压。每个ADC有一个DAC。电压范围在0V(代码000H)和2.5V的REFIN(代码FFFH)之间。如果所选电压在0.5V至2.5V范围内,则ADC工作正常。DAC的输出电压设置ADC的差分输入范围,即±REF_ADC。所需的输入范围可按1.22mV的步进进行调整。

在VECANA模式下,数字输入字ADIN中包含的增益信息自动设置DAC值。有关更多信息,请参阅Vecana接口部分。

在所有其他模式中,数字接口内的每个输入通道都有一个寄存器,用于存储任何给定通道的增益信息。当应用程序选择特定信道时,该寄存器的值自动写入DAC,DAC输出调整为所需值。DAC在250 ns(相当于最小采集时间)内沉降到该值。

当复位条件发生时,寄存器内的增益信息被设置为零。在使用ADC之前,需要将这些寄存器设置为选定的值。

在VECANA模式下,DAC最初设置为满标度,差分输入范围等于±(REFIN引脚处的电压)。

注意:当采样电容器A2和B2(或AX和BX)上保持数据并且在转换特定信道A2和B2(或AX和BX)之前在中间转换中修改ADC的增益时,会发生基本的偏移误差。这种偏移误差在两种情况下都是可能的:

1、数据可以通过HOLD2信号保存在异步采样和保持电容器AX和BX上。其他信道可以在异步信号AX和BX之前转换。如果在这些转换过程中增益发生变化,则会发生偏移误差。

2、使用输入命令4-6,通道A1和B1与A2和B2保持在一起。通道A1和B1将首先转换。在该转换或进一步的中间转换期间,如果在信道A2和B2的转换之前修改增益,则发生偏移误差。

抵销调整

与增益类似,偏移量可以相对于ADC的实际输入电压范围调整为12位电平。例如,如果输入范围为±1V,偏移量可以在488×V的增量中进行调整,最大调整为输入范围的±12.5%。

每个输入通道的数字接口内都有一个寄存器。该寄存器存储每个通道的偏移调整值。选择要转换的通道时,将自动调整偏移。在转换过程中,不得更改所选通道和相关寄存器信息。

将寄存器设置为201H会导致-12.5%的调整,000H不会导致调整,1fh会导致+12.5%的调整。不允许偏移调整值200H。

偏移调整不能在VECANA模式下使用。重置条件会将偏移调整设置为零。

过渡噪声

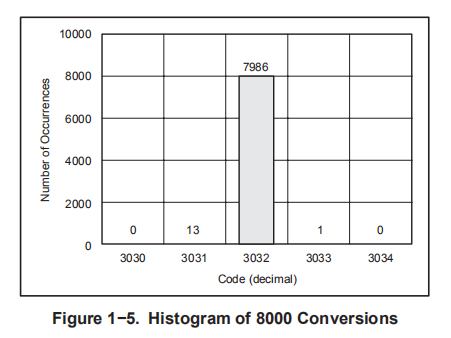

ADS7869本身的转换噪声很低,如图1-5所示。应用低噪声直流输入并启动8000次转换生成此直方图。

符号比较器

ADS7869包括两组不同滞后的符号比较器。第一组用于马达控制应用中的位置传感器输入,连接到输入A1、B1、A2和B2。这些比较器的磁滞通常为75mV。在电机控制应用中,这些比较器用于测量位置传感器输入信号的符号。

第二组与U C;、V C;和W C管脚处的窗口比较器并联。这些元件的磁滞通常为10毫伏。在电机控制应用中,这些比较器被用来测量主电流的符号。

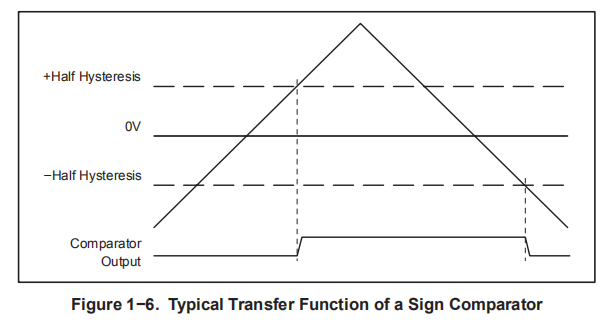

如果差动输入电压高于磁滞的+1/2,则符号比较器从0切换到1。如果输出为1,如果差分输入电压低于滞后的-1/2,则符号比较器切换回0。见图1-6。

比较器的输入范围是有限的。差分输入的较低电压应始终在0至AV−1.8V的范围内。

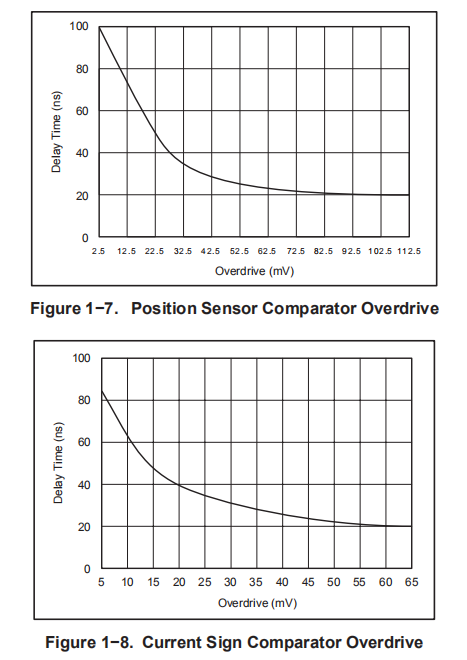

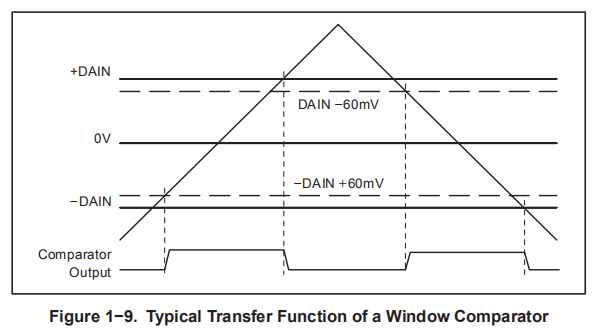

在每个比较器上,输出延迟到输入电压。此延迟取决于比较器输入的过驱动。超速档是输入电压(VIN)减去磁滞的一半。

如果位置传感器符号比较器的差分输入电压从-40 mV切换到+40 mV(步进功能,2.5 mV超速),则输出的延迟时间通常为100 ns。如果比较器在-100mV和+100mV(72.5mV超速)之间切换,则延迟通常减少到25ns。对于不同超速档下的延迟时间与步长的函数关系,请参见图1-7和图1-8。

窗口比较器

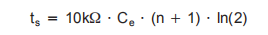

窗口比较器测试输入电压是否在一定范围内;该范围为±(施加到DAN的电压,引脚30)。如果差分输入电压保持在此范围内,则窗口比较器的输出为1。如果电压超出此范围,则输出设置为0。窗口比较器有一个滞后,当输出为0时该滞后被打开。当输入电压在±(DAIN-60mV)范围内时,比较器输出切换回1。(见图1-9。)DAIN处的电压需要在0.5V到2.5V的范围内。

窗口比较器具有开关电容电路,类似于ADC结构,但不同于其他窗口比较器。这种设计大大提高了精度;由于额外的精度,需要一个适当的输入信号前端。(参见窗口比较器输入部分。)

两个时钟周期用于采样输入。接下来的两个时钟周期用于测试电压下限和上限。每四个时钟周期(或每250ns,16MHz时钟)更新窗口比较器的输出。在最坏的情况下,窗口比较器需要六个时钟周期来检测电流限制。窗口比较器需要连续时钟才能正常工作。

在电机控制应用中,窗口比较器用于监测主电流的故障。

位数模转换器

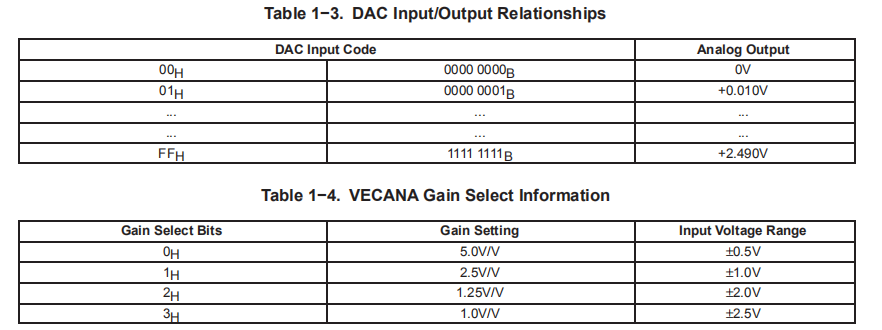

DAIN(引脚30)需要0.5V到2.5V之间的电压来设置窗口比较器的范围;这可以通过8位DAC来实现。DAC值通过数字接口编程。

00H对应于0V的DAC输出电压。满标度值(FFH)为2.49V(内部参考减去1LSB)。

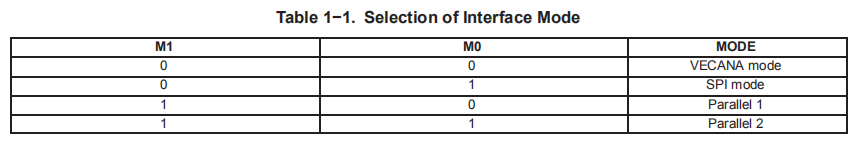

输出阻抗通常为10kΩ;输出阻抗与输出电压无关。DAC输出连接到DAOUT(引脚29)。稳定时间(t)取决于该引脚上的外部电容(C),可计算为:

在这个方程中,n等于8,DAC的分辨率。输出阻抗也限制了输出电流。该电流不应超过0.5微安(0.5微安10kΩ=5mV)。

道特和丹可以做空。电容器(通常为0.1μF)可用于低通DAC输出;但是,不需要这种低通配置。

内部参考

内部基准REFOUT(引脚96)提供REFIN(引脚97)处ADC基准输入所需的2.5V电压。具有高阻抗输出的内部缓冲器驱动参考输出引脚。此内部缓冲区经过优化,可排除参考管脚处的故障。任何一个电容器都可以连接到复位管脚,以减少噪音。建议将0.1μF电容器连接在重新输出(插脚96)和SGND(插脚13)之间。信号接地SGND在内部用作负参考。参考电压被认为是该接地和再输出之间的差分电压。

正常情况下,REFOUT和REFIN引脚均短路。内部基准提供良好的温度漂移,通常为20ppm,25°C时的初始精度为2.5V±20mV。如果这不能提供应用所需的精度,则可以将外部基准连接到REFIN引脚。

接地

最佳测试结果是在一个坚实的地面上实现的:线性,偏移和噪声性能都显示出改善。在印刷电路板布局过程中,应注意回路电流不会穿过任何敏感区域或信号。

与ADS7869接口的数字信号参考固体接地平面。ADS7869内部的ESD保护二极管在接地分离且数字输入低于-0.3V时开始导电;这包括短路故障。电流将流经ADS7869的基板,并干扰模拟性能。

供应

ADS7869有两个独立的电源,BV(引脚48和78)和AV(引脚8、18、28、85和98)。

BV仅用作数字键盘电源,电压范围为2.7V至5.5V。这使得ADS7869能够与所有最先进的处理器和控制器进行接口。为了限制从外部数字电路到ADS7869的噪声能量,必须对BV进行滤波。通过BV的电流远低于5mA;根据外部负载,可以在外部数字电路和ADS7869之间放置一个10Ω至100Ω的电阻器。旁路电容器(两个0.1μF和一个10μF)应放置在两个BVDD引脚和接地平面之间。

AV为内部电路供电,范围从4.5伏到5.5伏不等。由于ADS7869的供电电流通常为45毫安,因此无法在应用程序的数字板电源和AV管脚之间使用无源滤波器。为了为ADS7869和必要的模拟前端产生模拟电源电压,建议使用线性调节器(7805系列)。应在所有AV引脚和接地平面之间放置0.1μF的旁路电容器。应在两个AV引脚和接地平面之间放置10μF的旁路电容器。

数字部分

简介

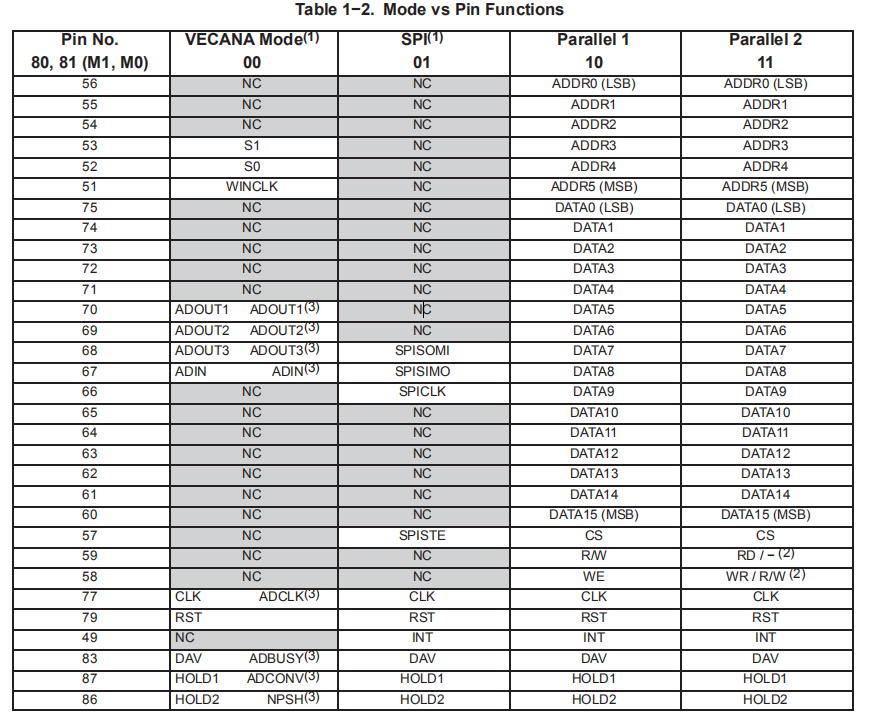

ADS7869可以通过四种不同的方式与DSP或μC接口。M1和M0引脚决定ADS7869将在哪种模式下通信;见表1-1。它可以作为标准的VECANA01接口、SPI或两个不同的并行接口连接。

作为所选模式的一个功能,一些管脚将具有不同的分配,如表1-2所示。表1-2。

(1)、NC表示无连接。VECANA01和SPI模式下的NC引脚应使用下拉电阻器接地。

(2)、对于并行模式11,有一个子模式与TMS320c54xx DSP系列兼容;参见模式11总线访问(TMS320c54xx DSP系列兼容模式)一节。

(3)、原始VECANA01管脚名称。

VECANA接口

ADS7869接口的VECANA01模式与原始的VECANA01接口完全相同。为了向后兼容,此模式被添加到ADS7869中。VECANA01接口是一个具有一个串行输入和三个串行输出的专用串行接口。

采样和转换由HOLD1和CLK输入控制。ADS7869设计用于在CLK输入端提供外部时钟的情况下工作。这允许转换与系统时钟同步,从而减少瞬态噪声影响。DAV信号指示用低电平脉冲进行转换的时间。DAV信号相当于VECANA01中的ADBUSY信号。

规定精度的典型时钟频率为16MHz。这将导致一个完整的转换周期,S/H采集和1微秒的模数(a/D)转换循环并在下一次转换开始时再次启动(在HOLD1变低之后);参见WINCLK选择部分。

当对ADS7869通电时,在第二个周期上传输有效数字数据之前,初始化需要一个转换周期。通电后的第一次转换是用输入设置寄存器中的不确定配置值执行的。第二个转换使用这些值执行正确的转换并从每个adc输出有效的数字数据。

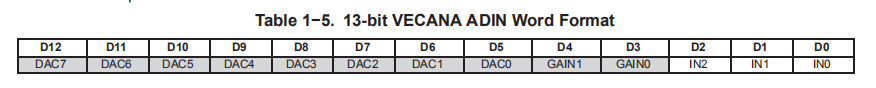

ADS7869接收的设置字用于下一个转换周期,而adc在一个转换周期中转换和传输其串行数字数据。13位字被提供给ADIN(pin 67),并存储在缓冲输入设置寄存器中。

配置参数为:DAC输出电压;可编程增益/输入电压范围;输入多路复用器;以及样本和保留选择。

ADI字的DAC输入部分(位DAC[7…0])确定DAC输出电压的值;见表1-5。8位DAC有256个可能的输出阶跃,从0V到+2.490V。1LSB的值为9.76mV(输入/输出关系见表1-3)。

表1-3至表1-6显示了有关这些参数的信息。

增益选择部分(比特增益[1..0])确定ADIN字的可编程增益;参见表1-5。所有三个ADC的增益由一个增益输入参数设置。增益值和允许的满标度输入如表1-4所示。

ADC3处的通道AN1、AN2和AN3的增益设置和输入电压范围始终为相对于±2.5V的1.0V/V。

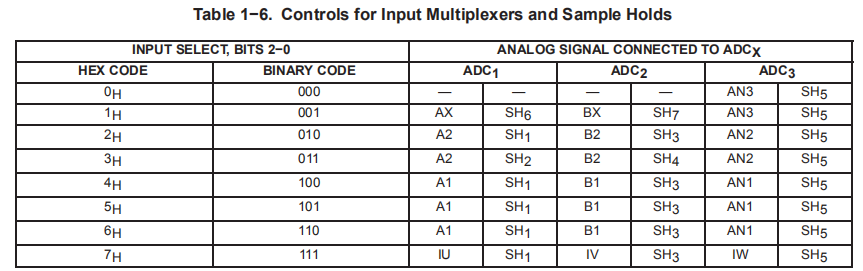

输入通道选择

表1-6显示了输入选择位的值与被转换的输入信道之间的关系。

输入选择=0H

同步采样保持,SH,采样AN3(仅),然后ADC3在信号保持1上转换它。输入选择=1H5,AX由异步采样保持SH6和信号保持2进行采样;ADC1在,信号保持1。BX由异步采样保持SH7和信号保持2进行采样;ADC2在信号保持1上对其进行转换。AN3被同步采样并保持,SH5然后ADC3在信号保持1上转换它。

在整个转换过程中,信号保持2必须低。如果在转换开始前保持2为高,则ADC1和ADC2将不转换。

输入选择=2H

A2由同步采样保持SH采样;ADC1在信号保持1上转换它。B2由同步采样保持SH进行采样;ADC2在信号保持1上对其进行转换。AN2由同步采样保持SH进行采样;ADC3在信号保持1上对其进行转换。

输入选择=3H

A2由信号保持架1上的ADC1转换。A2在输入的前一转换中在SH上采样选择4H、5H或6H。信号保持架1上的B2由ADC2转换。在前面的转换中,B2在SH上采样,输入选择4H、5H或6H。AN2由同步采样和保持(SH;ADC3)采样在信号保持架1上转换。

输入选择=4H、5H和6H

A1由同步采样保持SH采样;ADC1在信号保持1上转换它。B1由同步采样保持SH采样;ADC2在信号保持1上对其进行转换。AN1由同步采样保持SH进行采样;ADC3在信号保持1上对其进行转换。A2由同步采样和保持,SH,信号保持1。B2由同步采样并保持,信号保持架1上的SH4。

输入选择=7H

IU由同步采样保持SH采样;ADC1在信号保持1上转换它。IV由同步采样保持SH进行采样;ADC2在信号保持1上对其进行转换。IW由同步采样保持SH采样;ADC3在信号保持1上转换它。

VECANA定时特性(一)

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。

WINCLK选择

在VECANA01模式下,可以在WINCLK(引脚51)上为窗口比较器应用单独的时钟。通过使用管脚S0(管脚52)和S1(管脚53)作为解码器输入,可以为窗口比较器提供系统时钟、外部时钟(由WINCLK提供)和两个分开的外部时钟。

CLK(引脚77)提供的系统时钟在其它模式(SPI和并行模式)下驱动窗口比较器。

窗口比较器时钟WINCLK必须与CLK(引脚77)提供的系统时钟同步。当系统以15MHz时钟运行时,可为窗口比较器提供6MHz时钟。

为了提供具有1μs检测时间的最大窗口比较器,必须提供6MHz的最小时钟。请参阅窗口比较器部分。必须用连续时钟操作窗口比较器。

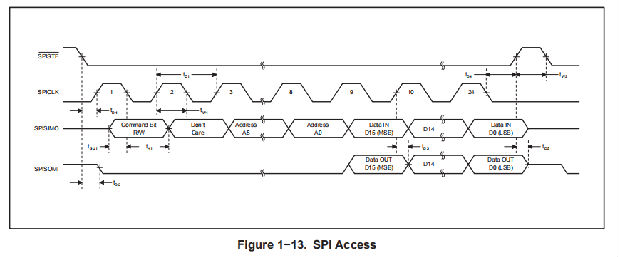

串行外围接口(SPI)

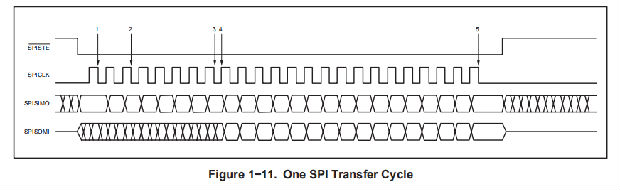

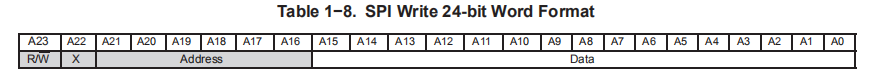

SPI与系统的其余部分完全异步运行。SPI的四个信号是SPICLK,SPISIMO,SPI的最大速度是25MHz。当选择信号SPISTE为高时,除地址和数据寄存器外,整个SPI处于复位状态。SPI时钟SPICLK和串行当SPISTE高时,数据输入SPISIMO被禁用。输入的数据由SPICLK下降沿上的SPI触发。输出数据放在SPICLK上升沿的输出SPISOMI上(见图1-11)。对于一个16位数据字的传输,需要24位。ADS7869的第一个输入位确定整个传输是读操作还是写操作。“1”表示读取,“0”表示写入操作。有七个地址位,但只使用六个lsb。然后发送或接收16个数据位。

完成一个16位传输,如下所示:

1、在SPICLK的第一个下降沿上,读/写位被冲程。

2、在SPICLK的第三个下降沿上,地址(位5)的MSB被选通。

3、在SPICLK的第八个下降沿上,地址(位0)的LSB被选通,并且读取寄存器映射的相应数据。

4、在第九上升沿上,从寄存器映射读取的数据被锁存到移位寄存器中,并在SPICLK的每个上升沿上移动一个位置。即使执行了写入操作,也始终会发送此数据。

5、在SPICLK的第24个下降沿上,如果执行了写入操作,则最后一个数据位从SPISIMO移入,并生成写入脉冲将数据写入寄存器映射。

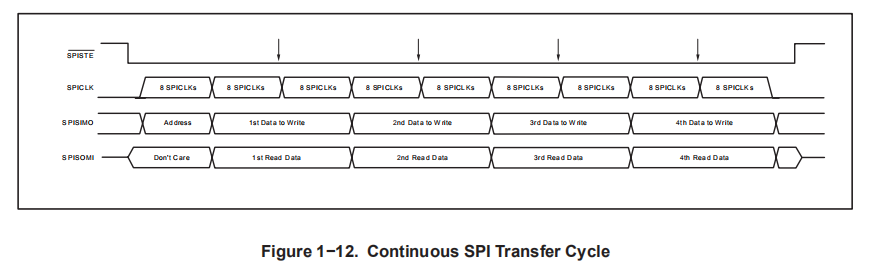

在连续读或写期间(参见图1-12),地址在每次读或写之后递减;参见指示箭头。当地址设置为00H时,在开始时,FIFO可以快速读出。这个数据被写入数据字的第16个SPICLK上的寄存器映射。如果SPISTE在数据字中的第16个SPICLK之前处于非活动状态,则数据不会写入寄存器映射;因此,数据丢失。

定时特性

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。

并行接口

并行接口具有以下主要功能:

1、数据词:

(1)、支持宽度为16位的数据路径。

2、总线握手:

(1)、分离RD和WR型控制信号。

(2)、分离R/W和WE型控制信号。

3、映射

(1)、ADS7869显示为内存映射外设。

(2)、内部寄存器直接映射到外部总线地址空间中的连续位置。

并行读写控制

从ADS7869读取和写入由芯片选择输入(CS,引脚57)控制,写入输入(WR,引脚58)和读取输入(RD,引脚59)。模式11有一个控制位,可以复位以激活特殊的兼容模式。(请参阅模式11总线访问[DSP兼容模式]部分。)根据主机处理器的需要,读/写引脚可以配置为组合读/写和写启用。模式管脚M0和M1决定主机访问ADS7869的方法。

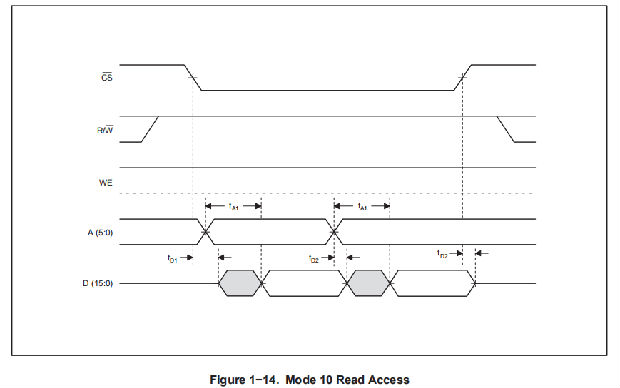

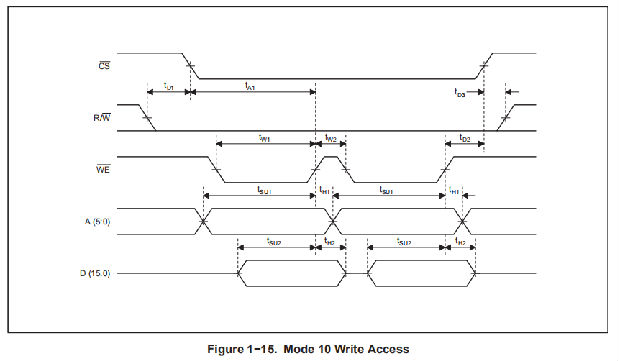

模式10总线接入

当M1=1和M0=0(模式10)时,主机端口使用RD(引脚59)作为读/写信号(R/W),并且WR(引脚58)作为写入使能信号WE。仅当ADS7869的芯片选择输入CS(引脚57)处于低激活状态时,才处理当前周期。

R/W决定总线周期内传输的方向;见图1-14。当R/W高时,数据是由ADS7869放在数据库上,根据地址,只要CS低。

对于写入周期,低电平信号(在WE上)向ADS7869指示总线上的数据有效。与数据的上升沿被锁在ADS7869中。当主机将CS设置为低时,检测到对ADS7869的有效访问(见图1-15)。

读取定时特性

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。

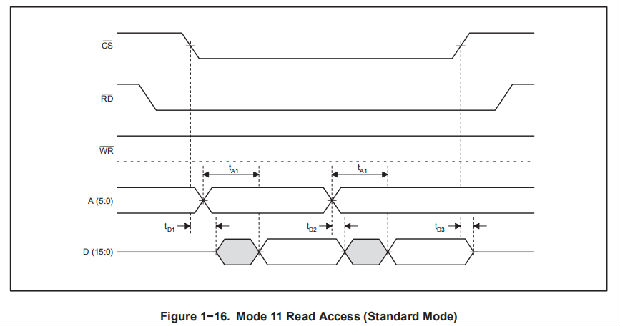

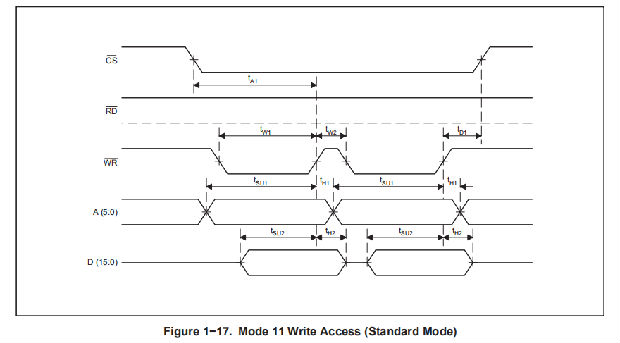

模式11总线接入(标准模式)

当M1=1和M0=1(模式11)时,主机端口使用WR(引脚58)和RD(引脚59)对ADS7869进行独立的读写访问。仅当ADS7869的CS(引脚57)输入为有效低电平时,才处理当前周期。并行寄存器的位0(地址27 h)必须具有1的重置值才能使用标准模式。

在模式11操作中,RD向ADS7869指示主机处理器已请求数据传输(见图1-16)。ADS7869向主机输出数据。地址可以在CS低周期内更改,并且可以读取多个数据。

为了配置ADS7869中的寄存器,主机发出一个WR信号,指示有效数据可用

在公共汽车上。随着WR的上升沿,数据被锁存到ADS7869中;见图1-17。地址因为ADS7869必须在写入操作发生之前有效。CS信号可以在两次连续写入之间保持低位。

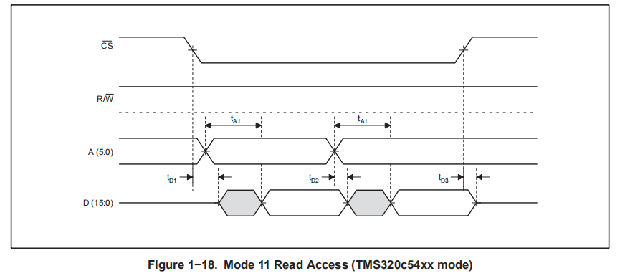

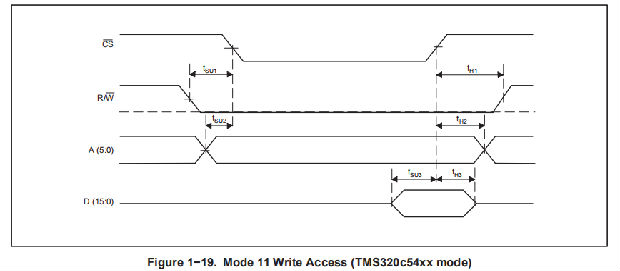

模式11总线访问(TMS320c54xx DSP系列兼容模式)

在TMS320c54xx DSP系列兼容模式(M1=1和M0=1)中,主机端口使用CS(引脚57)与W R(pin 57)一起作为对ADS7869的独立读写访问的R/W。并行寄存器(地址27)的位0必须具有0的值才能使用这种兼容模式。

在此模式下,CS与R/W(保持高)一起向ADS7869指示主机处理器已请求读取数据传输(见图1-18)。只要CS是活动低电平,ADS7869就会向主机输出数据。

为了配置寄存器,在ADS7869中,主机将R/W信号设置为低,以指示总线上有可用的有效数据。随着CS的上升沿,数据被锁存到ADS7869中(见图1-19)。在CS设置为低之前,ADS7869的地址必须有效。

在使用此模式之前,必须重置地址27H处的寄存器位0。由于写入访问与模式11的写入访问相似,因此可以使用原始模式11的TMS320C54xx DSP写入操作来执行复位。(见模式11总线访问[标准模式]部分。)如上文所述,在重置位0后,此模式可以执行读取操作。

先进先出数据寄存器(00H)

FIFO数据寄存器位于寄存器映射中的地址00H。FIFO的输出字是16位格式。ADC的分辨率为12位。每个adc的输出数据都是二进制2的补码格式。四个msb用于通道标识。

每个转换都有三个单词存储在FIFO中。必须对该寄存器进行三次读取访问,才能从FIFO中获取所有三个转换值。

偏移寄存器(01H至0CH)

偏移寄存器存储在地址01H到0CH处。偏移寄存器宽10位,用两个补码格式表示。符号位被复制到位位置15到10。此复制仅由读取访问执行(即,不能正确设置位15到10,以实现符号位的复制)。有效的偏移调整值是从-511(201H)到+511(1fh)。不允许值–512(200H)。

增益寄存器(0DH至18H)

增益寄存器存储在地址0DH到18H。增益寄存器宽12位。增益值以直接二进制格式存储。

WINDAC寄存器(19H)

WINDAC寄存器位于地址19H。WINDAC寄存器设置窗口比较器使用的8位DAC的输出。这个单词是8位的直接二进制格式。输出电压是寄存器值和内部参考电压的函数。

控制寄存器(1AH)

控制寄存器位于地址1AH。控制寄存器包含输入选择和DAV引脚控制。(有关更多信息,请参阅FIFO部分。)控制寄存器的格式如表1-16所示。有关输入选择的更多信息,请参阅Vecana接口部分。

计数器控制/状态寄存器(1BH)

计数器控制/状态寄存器位于地址1BH。计数器控制/状态寄存器CCTRLSTAT是一个组合控制寄存器,用于计数器的过滤输入,状态寄存器用于计数器的过流或欠流状态以及被HOLD1触发的滤波输入信号。有关此主题的详细信息,请参阅数字计数器部分。

当滤波器位FxxE被设置时,适当的输入与系统时钟同步,并且数字滤波器处理输入信号。如果位被重置,则信号只是同步的。

当适当的计数器达到FFFFH值时,将设置溢出状态EOx/TOx。这表示在16MHz时,输入信号的两个边缘之间的时间大于4ms。只有时间计数器保持其值,直到执行计数器重置。有关更多信息,请参阅重置寄存器部分。

计数器输入CNTA2、CNTA1、CNTB2和CNTB1的滤波值用同步信号保持器1和存储在适当的位FB1、FA1、FB2和FA2中。

边缘计数寄存器(1CH、1DH、20H和21H)

两个边缘计数器有四个阴影寄存器。寄存器SYEDGCNT1和SYEDGCNT2、同步边缘计数1(地址1DH)和同步边缘计数2(地址21H)锁定值,当同步保持信号保持1设置为低时,从边缘计数器。

寄存器ASEDGCNT1、ASEDGCNT2、异步边缘计数1(在地址1CH中)和异步边缘计数2(在地址20H中),在异步保持信号时从边缘计数器锁定值保持2设置为低。

通过写入寄存器SYEDGCNT1,给边缘计数器1 EDGECNT1一个初始值。通过写入寄存器SYEDGCNT2,向边缘计数器2 EDGECNT2提供初始值。

边缘周期寄存器(1EH和22H)

两个边缘周期寄存器有两个只读阴影寄存器。寄存器SYEDGPRD1和SYEDGPRD2、同步边缘周期1(地址1EH)和同步边缘周期2(地址22H),同步保持信号保持1设置为低时,从边缘周期寄存器锁定值。

边缘时间段寄存器(1FH和23H)

两个边缘时间计数器有两个只读阴影寄存器。寄存器SYEDGTIME1和SYEDGTIME2、同步边缘时间1(地址1FH)和同步边缘时间2(地址23H),同步保持信号保持1设置为低时,锁定边缘时间计数器的值。

先进先出测试寄存器(24小时)

地址为24小时的FIFO测试寄存器的目的是在生产测试期间测试FIFO;FIFO通过该寄存器填充定义的模式。内部FIFO结构可以通过读取FIFO数据寄存器的模式来验证。当FIFO测试启用时,多路复用器被切换并将数据(FIFO测试寄存器的)引入FIFO,而不是普通的ADC数据;为了模拟三个ADC,数据被锁存到FIFO中三次。为了区分信道,第一个数据不变以模拟ADC1,第二个数据反转以模拟ADC2,第三个数据的六个lsb反转以模拟ADC3。在启用FIFO测试时,FIFO中总共存储三个数据字,其中一条写指令。为了用测试数据填充整个FIFO寄存器,必须执行10次写入。只有当四个启用位具有AH值时,测试数据才会写入FIFO。此寄存器不应在正常操作中使用。

比较器测试寄存器(25H)

地址25H中的比较器测试寄存器的目的是将定义的模式应用于比较器输出管脚。此功能用于测试DSP中的算法或由比较器输出控制的硬件。要启用比较器测试,寄存器的启用部分必须包含值0CH。此寄存器不应在正常操作中使用。通过读取比较器测试寄存器,比较器输出被发回,以便允许主机在一个周期内读取实际比较器输出。

中断寄存器(26H)

地址26H中的中断寄存器包含中断源和中断控制位。位xOxF是在特定计数器有过流或欠流时设置的。在读取中断寄存器之前,位保持设置;这与计数器的过流或欠流状态是否保持无关。当设置了适当的xOxE位时,计数器过流或欠流中断被启用。

FFF位FIFO full标志将在FIFO已满(或已满)时设置,并在读取中断寄存器之前保持设置,与FIFO是否已满无关。FF位FIFO full表示FIFO是否已满。读取中断寄存器时,FFF位被清除。当设置位FFE(或FIFO full enable)时,FIFO full中断被启用。

FEF位FIFO empty标志将在FIFO为(或曾经为)空时设置,并且在读取中断寄存器之前保持设置,与FIFO是否为空无关。FE位FIFO empty表示FIFO是否为空。读取中断寄存器时,位FEF被清除。当费用位FIFO empty enable被设置时,FIFO empty中断被启用。有关中断管脚的更多信息,请参阅中断部分。表1-24描述了中断寄存器。

并行寄存器(27H)

地址27H中的并行寄存器控制并行接口模式11;请参阅模式11总线访问部分。并行寄存器对模式00、01和10没有影响。并行寄存器中只有一个位,即M位。

复位寄存器(28H)

地址28H中的复位寄存器可以完全复位ADS7869,也可以简单地复位计数器。将AAH模式写入CX位将重置计数器1和计数器2以及与计数器相关的所有寄存器。将AAH模式写入SX位将迫使ADS7869进入复位状态;数字和模拟部分都被复位。复位寄存器是一个只写寄存器。如果读取复位寄存器,将接收数据0000H。输入字的格式如表1-26所示。要复位整个ADS7869,模式AAAAH应写入复位寄存器。

一旦重设寄存器激活系统重设,则不得重写寄存器以停用重设条件。将另一个模式写入CX位(AAH除外)将停用计数器的重置条件或设备的重置条件。

有关重置条件的详细信息,请参阅重置部分。

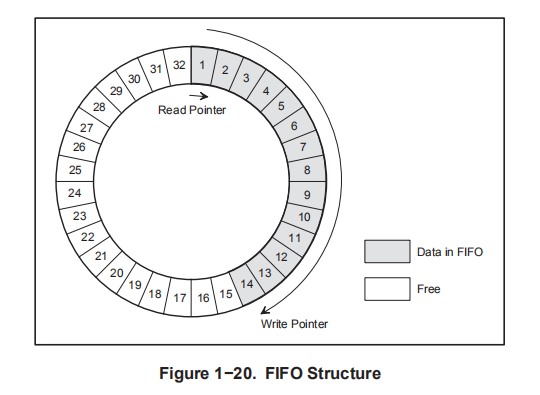

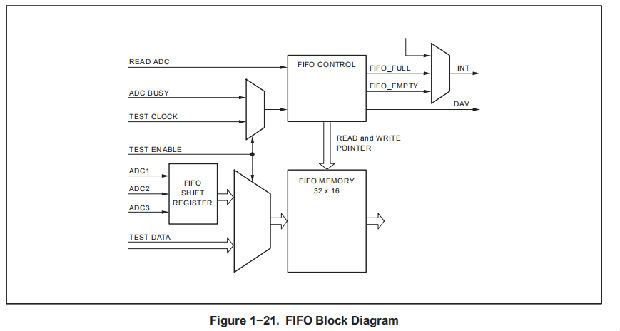

先进先出

ADS7869的FIFO被组织为32字的环形缓冲区,每个字16位,如图1-20所示。转换后的ADS7869数据自动写入FIFO。为了控制写入和读取过程,使用写入指针和读取指针。读取指针始终显示包含上次读取数据的位置。写入指针指示包含上次写入样本的位置。转换后的值以预定义的顺序写入循环缓冲区,从ADC1开始,到ADC3结束。通道号与ADC数据一起存储。FIFO的数据通过地址00H处的FIFO寄存器读取;其格式如表1-27所示。该表显示,已转换的信道数据的信道信息是持续维护的。寄存器映射中的地址00H只显示读取指针指向的数据。

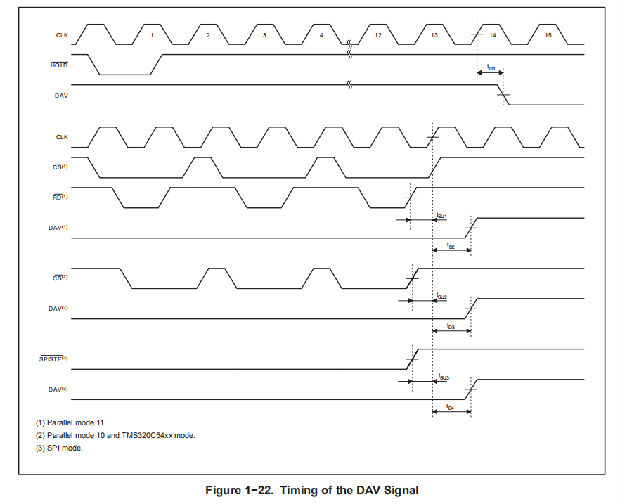

FIFO生成DAV信号;图1-22。在VECANA模式下,该信号为低电平;表示ADS7869正在转换数据。在其他模式下,DAV表示FIFO中的数据可用。DAV信号可以配置为正或负信号;请参阅控制寄存器部分。

当写入指针位于读取指针之前时,DAV信号变为活动状态。当读指针等于写指针时(即,当FIFO为空时),DAV信号再次变为非活动状态。

当adc将数据写入FIFO,并且写入指针比读取指针提前32步以上时,将设置FF(FIFO Full)状态。当执行第一个FIFO读取操作时,FF被清除。要在FF状态后同步指针,应读取FIFO,直到出现FE(FIFO空)。

如果尝试读取,而读指针和写指针相等,则读取指针不会增加;将再次读取相同的数据(具有相同通道号的数据)。发生这种情况时,将设置一个FE状态。当新数据写入FIFO时,FE状态被清除。读指针不会超过写指针。FF和FE都进入中断部分。FIFO的功能框图如图1-21所示。

测试数据的目的是验证应用程序开发的FIFO结构。这在FIFO测试寄存器部分中有描述。此寄存器不应在正常操作中使用。

DAV定时特性

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。

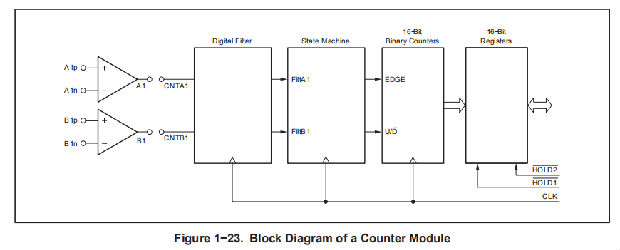

数字计数器模块

用于模拟位置传感器的ADS7869接口具有以下特点:

(1)、最高16MHz工作频率;

(2)、全四象限解码的错误安全状态机•高抗噪性:

-差分信号输入

-带滞后的模拟输入比较器

-施密特触发数字输入:数字噪声滤波器;16位二进制上/下计数器,带过流和欠流检测;与系统时钟同步;在采样和保持ADC值的同时,计数器值的异步和同步闭锁;五个阴影寄存器。

操作

模拟位置传感器在输出端有两个信号,正弦和余弦。两个信号都是差分的,并且彼此之间的位置是90度电。符号比较器通常具有75mV的滞后,处理位置传感器输出的差分信号。这大大降低了电机控制应用中的共模噪声。比较器的数字输出信号连接到计数器输入。使用施密特触发器输入获得额外的噪声抑制。数字信号通过可编程数字滤波器传输。经过过滤的无故障信号由状态机处理,状态机增加或减少计数器。然后计数器值被锁存到相应的通过同步或异步保持信号HOLD1和HOLD2进行寄存器。

每对位置传感器信号(A1、B1和A2、B2)都有一个计数器模块。这些计数器可以向上或向下计数,这取决于位置传感器信号的方向(即,分别为信号A1和B1或A2和B2的相位差)。当ADC通道被采样和保持时,这些计数器值存储在阴影寄存器中。四个位置传感器通道和计数器值在HOLD1或HOLD2信号上同时采样。

使用16MHz的系统时钟,计数器的最大数据速率为2MHz。

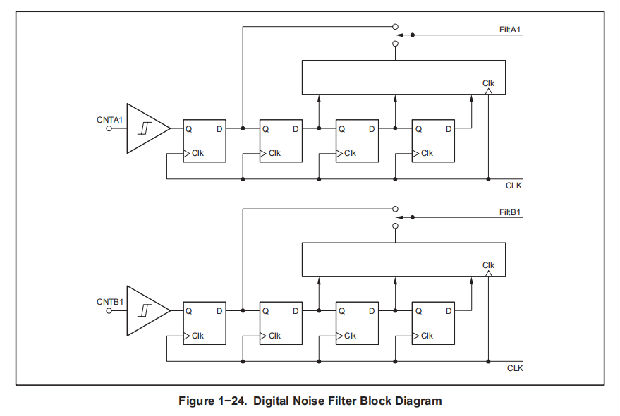

数字噪声滤波器

数字噪声滤波器抑制输入正交信号上的噪声。数字噪声滤波器抑制大、短持续时间的噪声尖峰;由噪声或尖峰触发的假计数也被显著抑制。见图1-24。

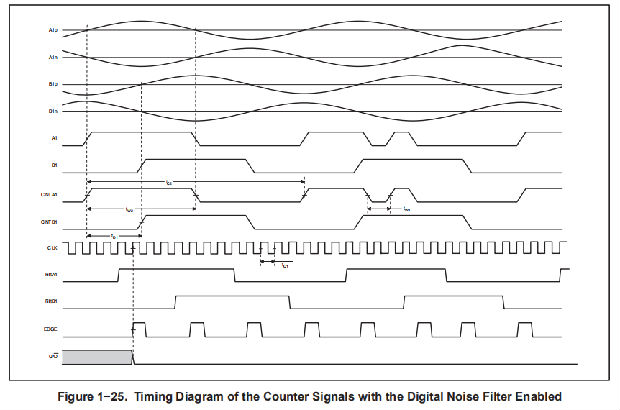

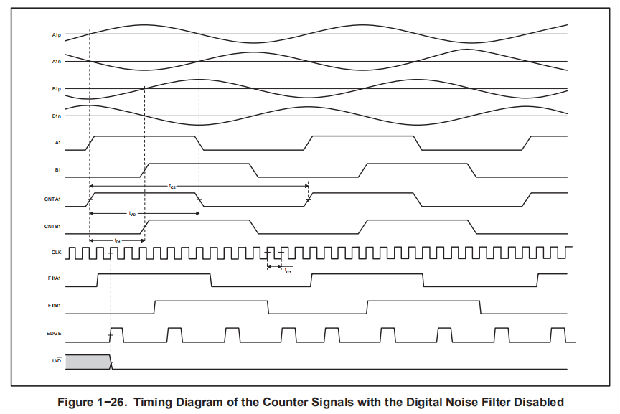

输入信号CntXY在上升时钟边缘采样。在信号被传递到状态机之前,信号必须至少稳定三个连续上升的时钟边缘。短于两个时钟周期的脉冲被拒绝;上升时钟边缘之间的故障也被忽略。见图1-25。

滤波定时特性(一)

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。

二进制计数器和寄存器

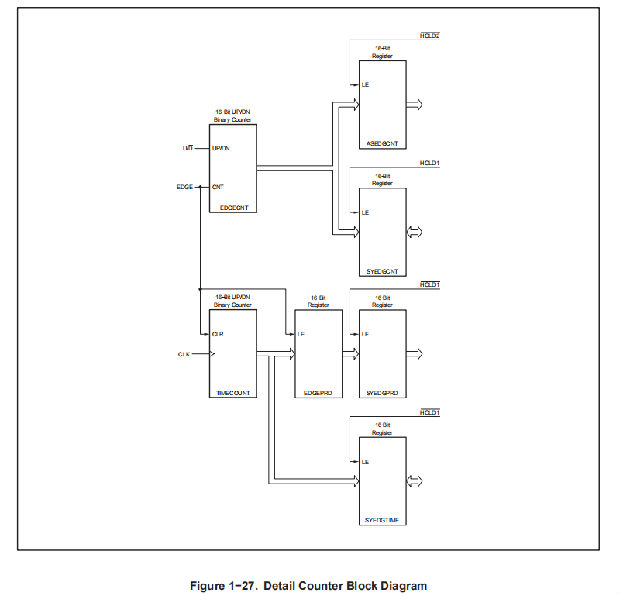

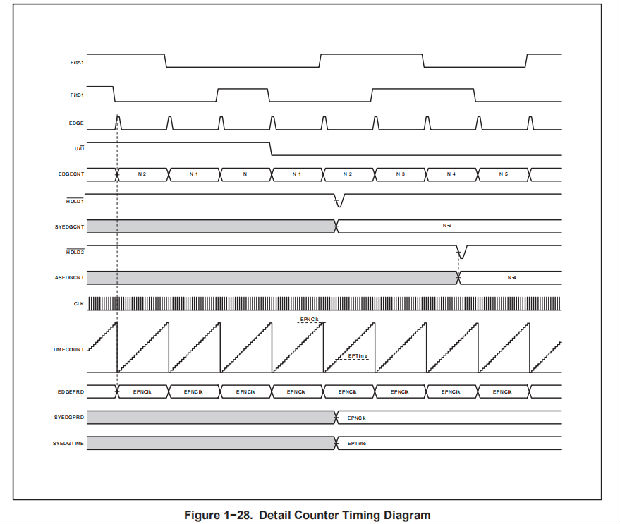

完整的上/下计数器包括两个16位计数器和五个16位阴影寄存器。第一个计数器是一个16位上/下计数器,它根据U/D信号。这是粗角计数器,它被称为EDGECNT。对于精细角度计算,实现了第二个16位计数器TIMECOUNT。此计数器随系统时钟递增,并在边缘信号出现时重置。无法递减TIMECOUNT计数器。系统是如图1-27所示,正时如图1-28所示。U/D信号高,向上计数,当B1在A1之前运行。当A1在B1之前运行时,U/D信号低,向下计数。边缘信号由A1和B1的每个滤波边缘设置。

当EDGECNT引起过流或欠流时,中断寄存器中相应的位被设置。计数器继续递增或递减。当边缘信号上升时,时间计数值锁定在阴影寄存器edgepd中。edgepd的值是比较器输入信号的两个有效边之间的系统时钟数。该值与位置传感器的角速度成正比。edgepd寄存器中的值锁定在SYEDGPRD中在同步保持信号HOLD1上注册。

EDGECNT和TIMECOUNT计数器值存储在阴影寄存器(SYEDGCNT和同步保持信号,HOLD1,对模拟输入进行采样。SYEDGTIME寄存器的值表示最后一个边缘信号和同步保持信号之间的时间保持1。EDGECNT计数器值存储在异步采样信号保持2。

阴影寄存器SYEDGCNT、ASEDGCNT、SYEDGPRD和SYEDGTIME可以通过寄存器映射读取。计数器EDGECNT可以通过寄存器映射中SYEDGCNT寄存器的地址写入。写入数据的14个msb存储在EDGECNT寄存器中。这两个lsb由输入FiltA1和FiltB1确定;请参阅边计数寄存器部分。这是为了防止边缘计数器和位置传感器输入信号的ADC数据之间的不一致。

中断

中断可以有几个来源:

(1)、FIFO完全状态

(2)、FIFO空状态

(3)、两次过流或欠流计数

(4)、两个边缘计数过流或过流

这六个信号源组合成一个中断信号。中断信号为高电平;当中断引脚INT为高电平时,六个源中的一个也为高电平。

要复位中断,必须读取中断寄存器(见中断寄存器部分),以便主机确定是哪个或哪个源引起中断。

复位

ADS7869可以通过三种不同的方式强制进入复位状态:

(1)、打开电源。

(2)、将RST引脚(复位引脚79)拉低。

(3)、写入复位寄存器。

此外,数字计数器可以通过复位寄存器复位,而无需复位整个ADS7869。

在复位状态下,模拟输入被采样,寄存器(在寄存器映射中)被强制进入其复位值,FIFO和计数器被清除。在复位条件下,需要一个上升的时钟脉冲来复位同步计数器。

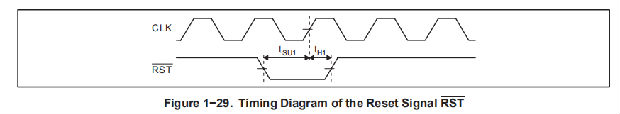

ADS7869在最后一个复位条件被清除后,需要一个时钟周期才能开始正常工作。(见图1-29。)

复位定时特性

超过推荐的工作自由空气温度范围在-40摄氏度到+85摄氏度,平均值=5V,BV=3V−5V。