108点击型号即可查看芯片规格书

AD1938点击型号即可查看芯片规格书

255点击型号即可查看芯片规格书

375点击型号即可查看芯片规格书

512点击型号即可查看芯片规格书

特征

PLL产生或直接主时钟;低电磁干扰设计;108 dB DAC/107 dB ADC动态范围和信噪比;-94分贝THD+N;3.3V单电源;5 V逻辑输入的公差;支持24位和8 kHz至192 kHz的采样率;差分ADC输入;单端DAC输出;具有可伸缩的SPI功能的日志音量控制;软件控制无点击静音;软件关机;右对齐、左对齐、I2S对齐和TDM模式;主/从模式高达16通道输入/输出;48铅LQFP包;适合汽车应用。

应用

汽车音响系统;家庭影院系统;机顶盒;数字音频效果处理器。

一般说明

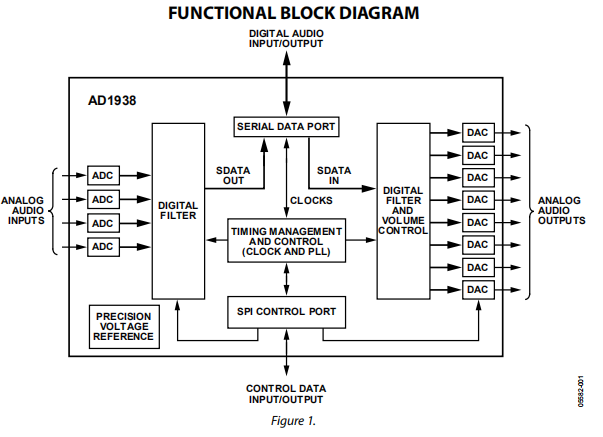

AD1938是一种高性能的单芯片编解码器,它提供四个带输入的模数转换器(ADC)和八个带单端输出的数模转换器(DAC),使用的是analog Devices,Inc.的专利多位sigma-delta(∑-Δ)架构。包括一个SPI端口,允许微控制器调节音量和许多其他参数。AD1938由3.3V数字和模拟电源供电。AD1938采用48引线(单端输出)LQFP封装。此系列的其他成员包括差分DAC输出和IC®控制端口版本。

AD1938是为低电磁干扰设计的。这种考虑在系统和电路设计架构中都是显而易见的。通过使用车载PLL从LR时钟或从外部晶体导出主时钟,AD1938消除了对单独的高频主时钟的需要,并且还可以与抑制位时钟一起使用。dac和adc采用最新的模拟器件连续时间结构设计,以进一步减小EMI。通过使用3.3V电源,功耗最小化,进一步降低排放。

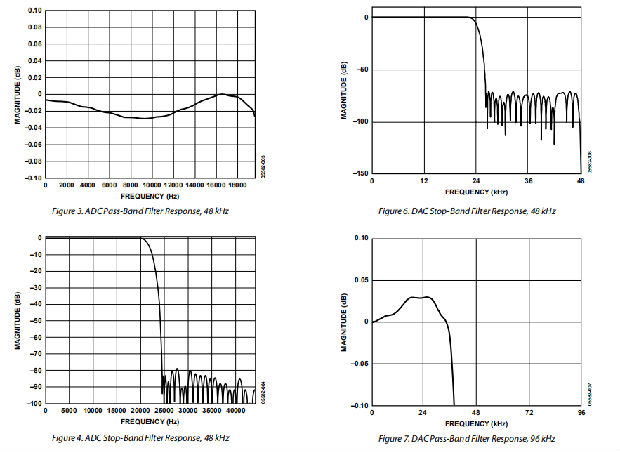

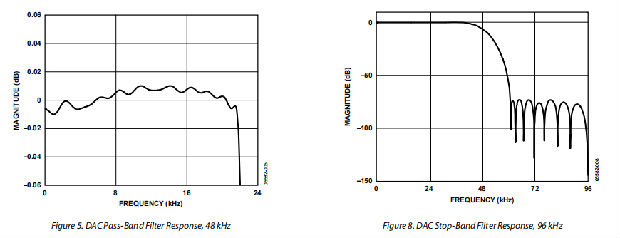

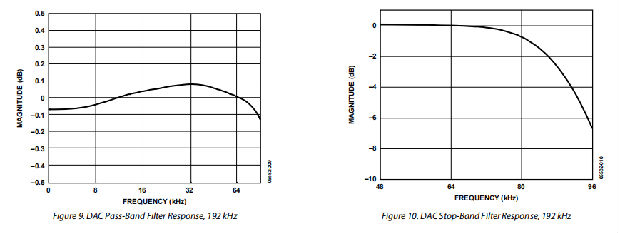

典型性能特征

操作理论

模数转换器(ADC)

AD1938中有四个ADC通道,配置为两个带差分输入的立体声对。adc可以在48khz、96khz或192khz的标称采样率下工作。adc包括具有79db阻带衰减和线性相位响应的车载数字抗混叠滤波器,以128的过采样率(48khz、96khz和192khz模式)工作。数字输出通过两个串行数据输出管脚(每个立体声对一个)和一个公共帧时钟(ALRCLK)和位时钟(ABCLK)提供。或者,TDM模式之一可用于在单个TDM数据线上访问多达16个信道。

ADC必须从差分信号源驱动才能获得最佳性能。ADC的输入引脚连接到内部开关电容器。为了将外部驱动运放与内部开关电容器引起的故障隔离,应使用串联的外部100Ω电阻器和从每个输入接地的1 nF电容器隔离每个输入引脚。这种电容器必须是高质量的,例如陶瓷NPO或聚丙烯薄膜。

差分输入的标称共模电压为1.5 V。共模参考引脚(CM)处的电压可用于偏置外部运算放大器以缓冲输入信号(见电源和电压参考章节)。输入也可以是交流耦合的,不需要外部直流偏压到厘米。

在串行控制下,数字高通滤波器可以与模数转换器(ADC)进行切换,以消除残余的直流偏移。它有一个1.4赫兹,6分贝每倍频程截止在48千赫采样率。截止频率与采样频率成正比。

数模转换器(DAC)

AD1938 DAC通道布置为单端、四对立体声对,为最小外部组件提供八个模拟输出。dac包括具有70db阻带衰减和线性相位响应的车载数字重建滤波器,以4(48khz或96khz模式)或2(192khz模式)的过采样率工作。每个通道都有自己的独立可编程衰减器,可在255步内以0.375分贝的增量进行调节。数字输入通过四个串行数据输入管脚(每个立体声对一个)、一个公共帧时钟(DLRCLK)和一个位时钟(DBCLK)提供。或者,TDM模式之一可用于在单个TDM数据线上访问多达16个信道。

每个输出管脚的标称共模直流电平为1.5 V,对于0 dBFS数字输入信号摆动±1.27 V。建议使用单运算放大器、三阶外部低通滤波器来消除输出引脚上的高频噪声。使用低转换率或低带宽的运放会导致高频噪声和音调向下折入音频频带;因此,在选择这些组件时要小心。

共模参考引脚CM处的电压可用于偏置缓冲输出信号的外部运算放大器(见电源和电压参考章节)。

时钟信号

可以选择片上锁相环(PLL)以参考来自LRCLK管脚的输入采样率或来自MCLKI/XI管脚的48 kHz模式的256、384、512或768倍采样率。通电时的默认值为256×f(来自MCLKI/XI引脚)。在96 kHz模式下,主时钟频率保持在相同的绝对频率;因此,实际倍率除以2。在192 kHz模式下,实际倍率除以4。例如,如果AD193x系列中的设备被编程为256×f模式,则主时钟输入的频率为256×48 kHz=12.288 MHz。如果AD193x随后切换到96 kHz操作(通过写入SPI端口),则主时钟的频率应保持在12.288 MHz,即128×f。在192 kHz模式下,这将变为64×f。

对于所有时钟模式,ADC的内部时钟为256×fS。DAC的内部时钟随模式变化:512×fS(48 kHz模式)、256×fS(96 kHz模式)或128×fS(192 kHz模式)。默认情况下,车载PLL从外部时钟生成该内部主时钟。如果在PLL和时钟控制1寄存器中选择,直接512×f(参考48 kHz模式)主时钟可用于adc或dac。注意,对于设置为192 kHz模式的ADC,不可能使用直接时钟。要求在这种模式下使用片上锁相环。

可在PLL和时钟控制0寄存器中关闭PLL。为了确保在改变PLL模式时可靠锁定,或者如果基准时钟在通电时不稳定,请关闭PLL电源,然后在基准时钟稳定时将其重新通电。

内部主时钟可以在PLL和时钟控制0寄存器中禁用,以减少AD1938空闲时的功耗。时钟应在启用前保持稳定。

除非选择了独立模式(请参阅串行控制端口部分),否则时钟通过复位禁用,并且必须通过写入SPI端口才能正常工作。

为了保持最高性能,将内部主时钟信号的时钟抖动限制在小于300 ps rms的时间间隔误差(TIE)。即使在这些电平下,如果抖动频谱包含较大的频谱峰值,DAC输出中也可能出现额外的噪声或音调。如果不使用内部PLL,最好使用独立的晶体振荡器来产生主时钟。此外,在应用于AD1938之前,时钟信号不经过FPGA、CPLD或其他大型数字芯片(例如DSP)是特别重要的。在大多数情况下,由于与其他不相关的数字输出信号共用电源和接地连接,这会导致时钟抖动。当使用PLL时,参考时钟中的抖动根据环路滤波器衰减到一定频率以上。

复位和断电

RST引脚的功能将所有控制寄存器设置为其默认设置。为避免pops,复位不会关闭模拟输出。在RST被解除asserte,PLL获得锁条件之后,一个初始化例程在AD1938中运行。这种初始化持续大约256个主时钟周期。

PLL和时钟控制0、DAC控制1和ADC控制1中的掉电位记录了相应部分的掉电。保留所有其他寄存器设置。到确保正确启动,应通过外部电阻器将RST引脚拉低。

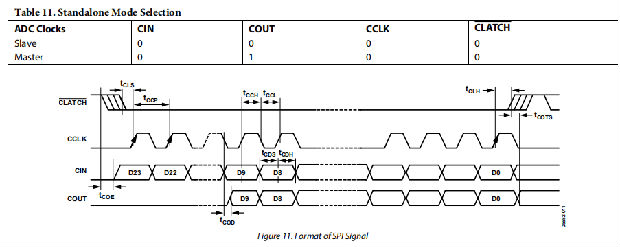

串行控制端口

AD1938有一个SPI控制端口,允许对ADC、DAC和时钟系统的内部控制寄存器进行编程和读取。也有一个独立模式可在没有配置串行控制的情况下运行表11。独立模式选择使用串行控制引脚复位。所有寄存器均设置为默认值,但内部主时钟启用设置为1,ADC BCLK和LRCLK主/从由COUT引脚设置。详见表11。独立模式仅支持具有IS数据格式和256 f主时钟速率的立体声模式。建议使用弱上拉电阻器有微控制器的应用中的碰撞。这个上拉电阻确保AD1938能够识别微控制器的存在。

AD1938的SPI控制端口是一个4线串行控制端口。该格式与Motorola SPI格式相似,只是输入数据字的宽度为24位。串行位时钟和锁存器可以与adc和dac的采样率完全异步。图11显示了SPI信号的格式。

第一个字节是具有读/写位的全局地址。对于AD1938,地址为0x04,由于R/W位左移一位。第二个字节是AD1938寄存器地址,第三个字节是数据。

电源和电压基准

AD1938设计用于3.3V电源。为模拟和数字部分提供单独的电源引脚。这些引脚应绕过100纳法陶瓷芯片电容器,尽可能接近引脚,以尽量减少噪声拾取。在与编解码器相同的印刷电路板上还应提供至少22μF的大块铝电解电容器。对于关键应用,通过为模拟部分和数字部分提供单独的电源,可以提高性能。如果这是不可能的,建议通过与每个电源串联的铁氧体磁珠隔离模拟和数字电源。模拟电源必须尽可能干净。

所有数字输入与TTL和CMOS电平兼容。所有输出均由3.3V DVD电源驱动,并与TTL和3.3V CMOS电平兼容。

ADC和DAC内部电压基准(VREF)在滤波器上输出,应尽可能靠近芯片旁路,并采用10μF和100 nF的并联组合。任何外部电流应限制在50μA以下。

可在PLL和时钟控制1寄存器中禁用内部参考,并可从外部源驱动滤波器。此配置可用于根据功率放大器的电源电压将DAC输出缩放到功率放大器的限幅级别。ADC输入增益随反比而变化。从ADC输入到DAC输出的总增益保持不变。

CM引脚是内部共模参考。应尽可能靠近芯片绕过,并采用47μF和100 nF的并联组合。该电压可用于将外部运放偏置至输入和输出信号引脚的共模电压。输出电流应限制在小于0.5毫安源和2毫安汇。

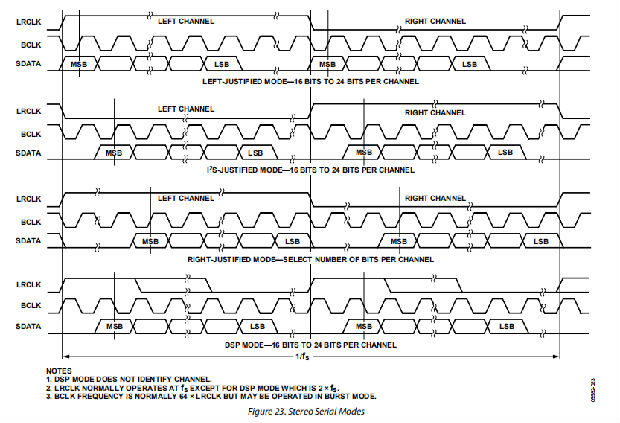

串行数据端口-数据格式

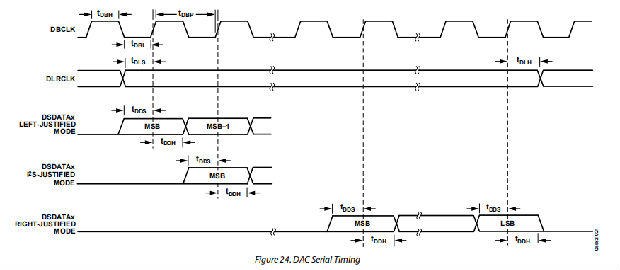

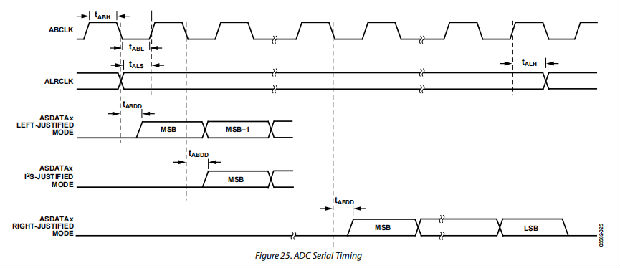

八个DAC通道在串行数据端口中使用一个公共串行位时钟(DBCLK)和一个公共左右帧时钟(DLRCLK)。四个ADC通道在串行数据端口中使用一个公共串行位时钟(ABCLK)和左右帧时钟(ALRCLK)。时钟信号都与采样率同步。正常的立体声串行模式如图23所示。

ADC和DAC串行数据模式默认为。端口也可以编程为左对齐、右对齐和TDM模式。字宽默认为24位,可编程为16位或20位。DAC串行格式可根据DAC控制0寄存器进行编程。DBCLK和DLRCLK的极性可根据DAC控制1寄存器进行编程。ADC串行格式和串行时钟极性可根据ADC控制1寄存器进行编程。根据DAC控制1寄存器和ADC控制2寄存器,DAC和ADC串行端口都可编程为总线主控。默认情况下,ADC和DAC串行端口都处于从属模式。

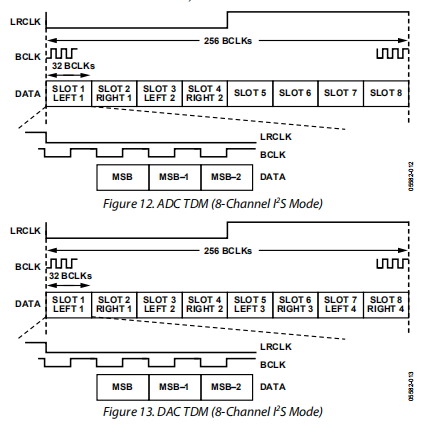

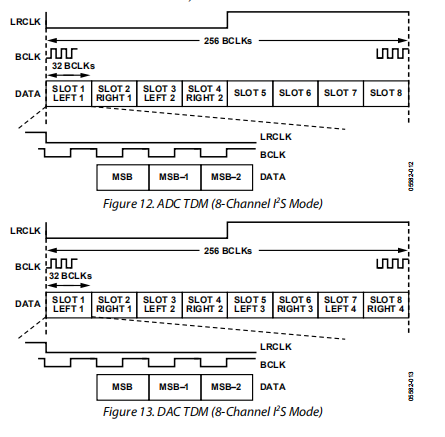

时分复用(TDM)模式

AD1938串行端口也有几种不同的TDM串行数据模式。第一个也是最常用的配置如图12和图13所示。在图12中,ADC串行端口输出一个数据流,该数据流由四个片上ADC和四个未使用的插槽组成。在图13中,八个片上DAC数据槽被打包成一个TDM流。在这种模式下,DBCLK和ABCLK都是256f。

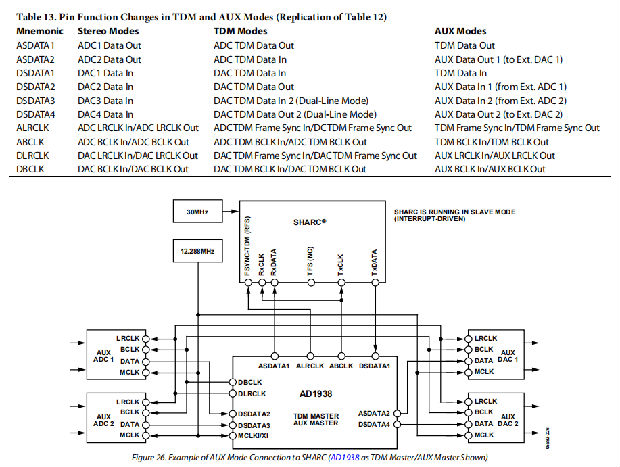

串行端口的I/O引脚根据所选的串行模式定义。有关TDM和辅助模式中每个引脚的功能的详细描述,请参见表12。

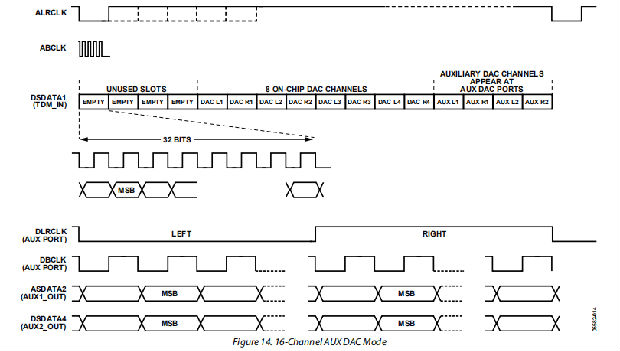

AD1938允许具有超过八个DAC信道的系统通过辅助串行数据端口的使用而容易配置。DAC TDM-AUX模式如图14所示。在这种模式下,辅助信道是TDM数据流的最后四个时隙。这些插槽被提取并输出到AUX串行端口。应注意的是,由于DBCLK频率高,此模式仅在48 kHz/44.1 kHz/32 kHz采样率下可用。

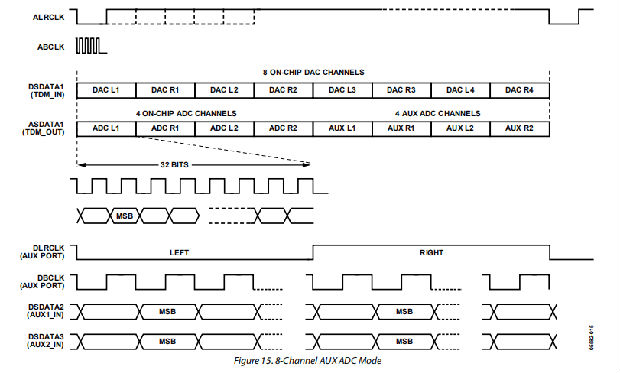

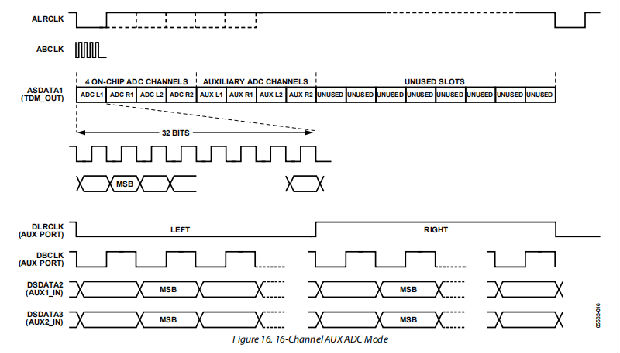

AD1938还允许具有四个以上ADC通道的系统配置,如图15和图16所示,分别使用8个ADC和16个ADC。同样,由于高ABCLK频率,此模式仅在48 kHz/44.1 kHz/32 kHz采样率下可用。

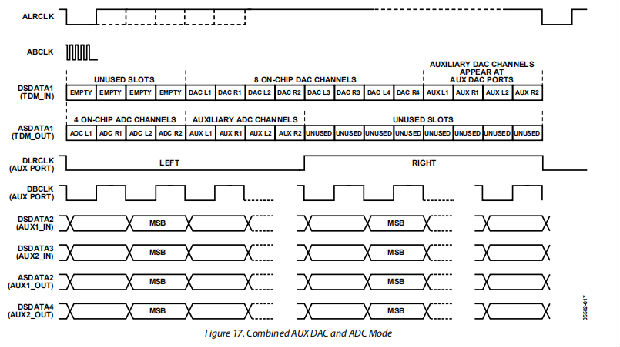

将AUX ADC和DAC模式结合在一起,可以得到8个ADC和12个DAC的系统配置。然后,该系统由两个外部立体声ADC、两个外部立体声DAC和一个AD1938组成。此模式如图17所示(AUX ADC和DAC组合模式)。

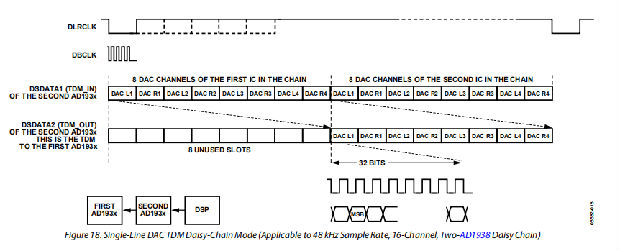

菊花链模式

AD1938允许菊花链配置将系统扩展到8个ADC和16个DAC(见图18)。在此模式下,DBCLK频率为512f。DAC TDM数据流的前8个时隙属于链中的第一个AD1938,最后8个时隙属于第二个AD1938。第二个AD1938是连接到DSP TDM端口的设备。

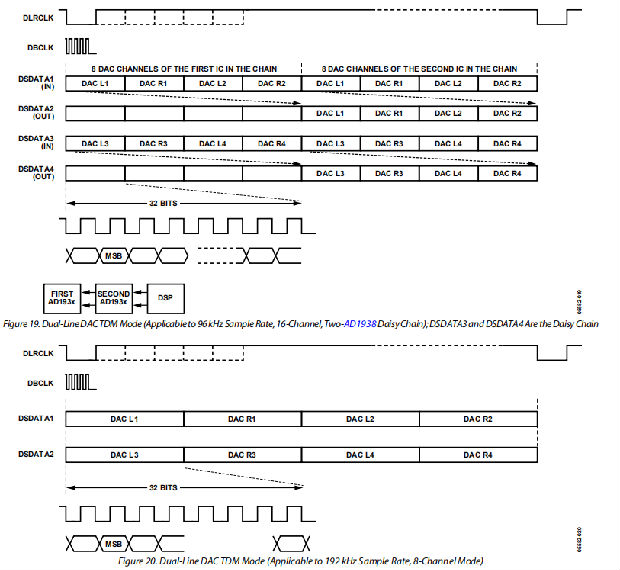

为了在96 kHz采样率下容纳16个信道,可以将AD1938配置为双线TDM模式,如图19所示。此模式允许比单线TDM模式通常需要的DBCLK慢。

同样,每个TDM输入的前四个信道属于链中的第一AD1938,最后四个信道属于第二AD1938。

双线TDM模式也可用于以192 kHz采样率向AD1938发送数据,如图20所示。

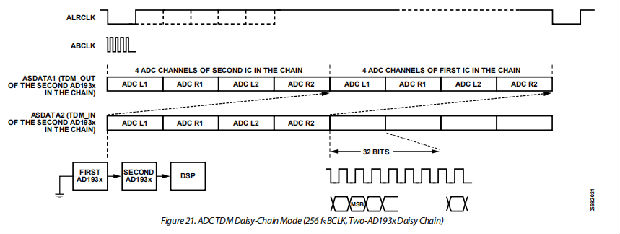

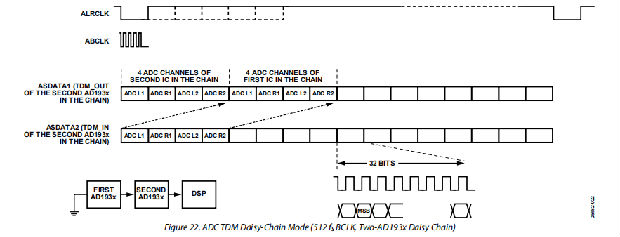

有两种配置可使ADC端口在菊花链模式下工作。第一个是图21所示的256F的ABCLK。第二种配置如图22所示。注意,在512f ABCLK模式下,ADC通道占用前8个插槽;后8个插槽为空。第一个AD1938的TDM单元必须在所有操作模式下接地。

串行端口的I/O引脚根据所选的串行模式定义。各引脚功能的详细说明见表13。请参见图26,了解具有两个外部立体声DAC和两个外部立体声ADC的典型AD1938配置。

图23到图25显示了串行模式格式。为了最大的灵活性,LRCK和BLK的极性是可编程的。在这些图中,所有的时钟都显示为正常极性。默认模式为。

控制寄存器

定义

AD1938的全局地址是0x04,由于R/W位左移一位。除设置为满卷的DAC卷寄存器外,所有寄存器都重置为0。

注意,每个控制寄存器参数中的第一个设置是默认设置。

附加模式

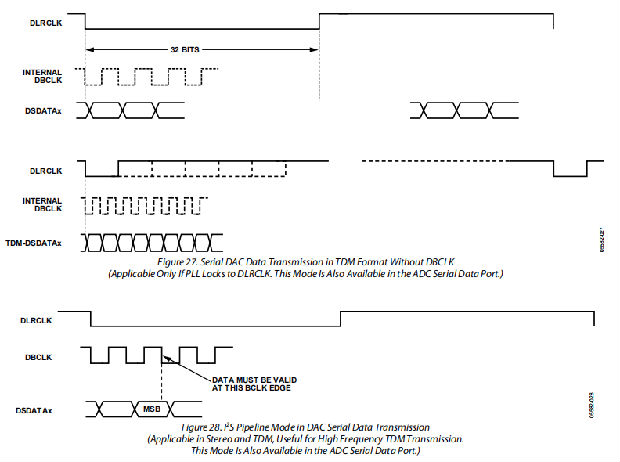

AD1938为板级设计增强提供了几种附加模式。为了减少板级设计中的电磁干扰,串行数据可以在没有显式BCLK的情况下传输。关于不需要高速DBCLK的DAC TDM数据传输模式的示例,请参见图27。当以DLRCLK为PLL参考频率的PLL生成AD1938主时钟时,该配置适用。

为了在高速TDM数据传输的情况下放宽AD1938的设置时间要求,AD1938可以利用DBCLK的下降沿来锁定数据。这有效地将整个BCLK周期专用于设置时间。此模式在源在串行数据驱动程序中具有较大延迟时间的情况下非常有用。图28显示了这种数据传输的管道模式。

在ADC串行数据端口上,无盲模式和流水线模式都可用。

应用电路

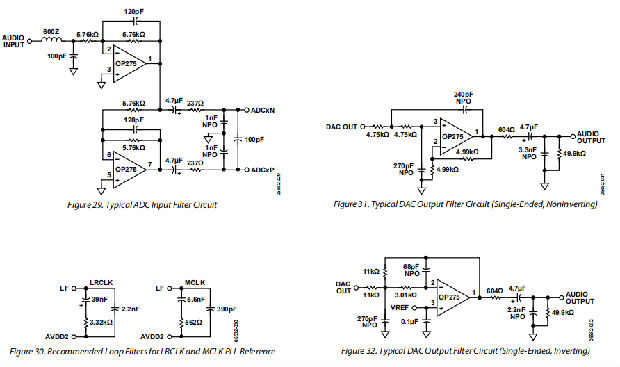

典型应用电路如图29至图32所示。图29显示了典型的ADC输入滤波器电路。作为PLL参考的LR时钟和主时钟的推荐环路滤波器如图30所示。DAC输出的输出滤波器如图31和图32所示。

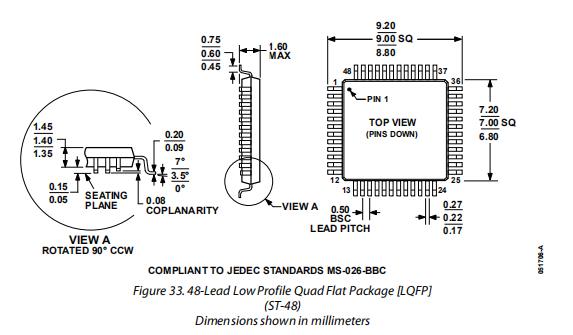

外形尺寸

汽车产品

AD1938WBSTZ和AD1938WBSTZ-RL型号提供受控制造,以支持汽车应用的质量和可靠性要求。请注意,这些车型的规格可能与商用车型不同;因此,设计师应仔细审查本数据表的规格部分。只有所示的汽车级产品可用于汽车应用。请与您当地的模拟设备客户代表联系以获取特定的产品订购信息,并获取这些型号的特定汽车可靠性报告。