FS6131-01点击型号即可查看芯片规格书

4095点击型号即可查看芯片规格书

1.0主要功能通过I2实现完全可编程控制C8482;总线可选CMOS或PECL兼容输出外部反馈回路功能允许发电机锁定用于抖动衰减的可调谐VCXO环路

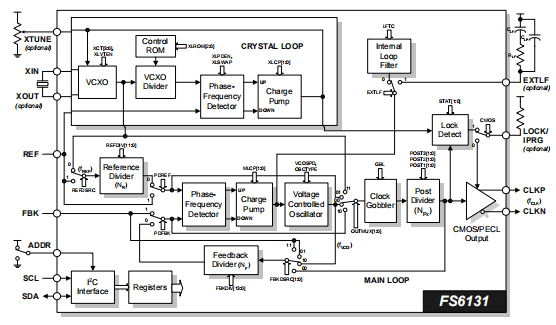

2.0一般说明FS6131-01是一个单片CMOS时钟发生器/再生器集成电路,其设计目的是在各种电子系统。通过I2C总线接口,FS6131-01可适应多种时钟产生要求。调整车载压控晶体振荡器(VCXO)的能力,参考和反馈分压器的长度,以及粒度和后分频器的灵活性使FS6131-01成为最灵活的独立锁相环(PLL)时钟。发电机可用。

3.0应用频率合成线路锁定和genlock应用时钟倍增电信抖动衰减

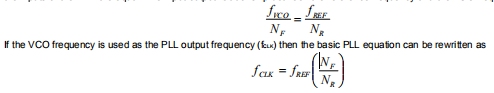

4.0功能块描述4.1主回路PLL主环路锁相环(ML-PLL)是一种标准的锁相环和频率锁相环结构。如错误所示!未找到参考源。ML-PLL由参考分压器、相频检测器(PFD)、电荷泵、内部环路滤波器、压控振荡器(VCO)、反馈分频器和后分频器。在工作期间,由车载晶体振荡器或外部频率源产生的参考频率(fREF)是首先由参考分压器减小。频率除以的整数值称为模数,表示为参考分压器。然后将分割的参考输入PFD。PFD通过电荷泵和环路滤波器控制VCO(fVCO)的频率。VCO提供高速、低噪音,用于ML-PLL的连续可变频率时钟源。VCO的输出通过反馈反馈反馈给PFD除法器(模数用NF表示)关闭回路。PFD将驱动VCO频率上升或下降,直到分割的参考频率和分割的VCO频率出现在PFD的输入是相等的。参考频率和VCO频率之间的输入/输出关系为

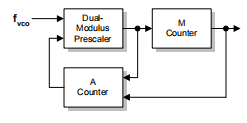

4.1.1条。参考分压器参考分压器是为低相位抖动而设计的。分频器接受任一晶体回路的输出(VCXO输出)或一个外部参考频率,并向PFD提供一个向下划分的频率。参考除法器是一个12位除法器,并且可编程设定从1到4095的任何模数。有关其他编程信息,请参见表3和表8。4.1.2条。反馈分配器反馈分频器基于双模预定标器技术。该技术允许与完全可编程反馈分频器,同时仍允许可编程部分以低速运行。高速预分频器(也称为预分频器),由于VCO的速度很高,所以放置在VCO和可编程反馈分频器之间可以操作。双模技术确保VCO在任何速度下都能可靠运行,并降低了分压器的功耗。例如,在反馈分配器中可以使用8的固定除法。不幸的是,除以8会限制反馈除法器路径的模数为8的倍数。这种限制将限制PLL在不使参考和反馈分频器值都相对较大的情况下实现期望的输入-输出频率比的能力。大分隔线由于相位抖动增加,通常不需要模。

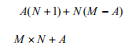

要了解操作,请参阅错误!找不到引用源。。M计数器(模为M)与双模预定标器。如果预分频器模数固定在N,则反馈分配器链的总模数将为MXN。然而,A计数器使预定标器模数在预定标器的第一个A输出中改变为N+1。A-柜台使双模预分频器恢复为N模,直到M计数器达到其终端状态并重置整个分隔符。总模量可以表示为

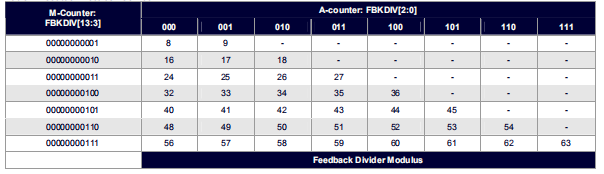

4.1.3条。反馈除法器编程M≥A的要求意味着反馈除法器只能编程为小于除法器模数56的某些值。除法器值的选择如表2所示。如果期望的反馈除法器小于56,请在表中查找除法器值。按列查找A计数器程序价值。沿着左边的行查找M计数器值。在56的模数以上,反馈分配器可以编程为16383以下的任何值。其他见表3和表8编程信息。

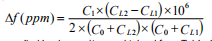

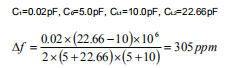

改变XTUNE引脚上的电压。有效负载电容的总变化(从一个极端到另一个极端)为1.5pF名义上,效果是错误的!找不到引用源。。振荡器以平行谐振模式操作晶体谐振器。晶体翘曲或晶体振荡频率的“拉”是通过改变有效载荷来实现的振荡器电路提供给晶体的电容。改变负载电容改变振荡器的实际量频率将取决于晶体的特性以及振荡器电路本身。晶体的运动电容(通常被晶体制造商称为C1),晶体的静态电容(C0)振荡器的负载电容决定了振荡器电路中晶体的翘曲能力。一个简单的公式确定晶体的总翘曲能力为

其中,CL1和CL2是从表11中获得的施加负载电容的两个极端值。示例:具有以下参数的晶体用于FS6131。总的粗调范围为:

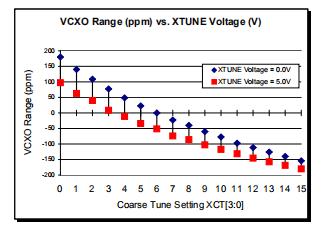

VCXO可以通过通过XCT[3:0]控制位对晶体负载电容的可编程调整来进行粗调见表11用于控制代码和相关的负载电容。调谐电容引起的实际频率扭曲量将取决于所使用的晶体。VCXO调谐电容包括一个外部6pF负载电容(从XIN引脚到接地为12pF,从XOUT引脚到接地为12pF)。这个VCXO的微调功能可以通过将XLVTEN位设置为1来启用,也可以通过将其设置为0来禁用。错误!找不到引用源。显示了粗微调机构的典型效果。总的粗调范围是约350ppm。VCXO频率的百万分之几(ppm)的差异显示为XTUNE引脚上的微调电压从0V到5V不等。请注意,随着晶体负载电容的增加,VCXO的频率会随着粗步,微调范围减小。微调范围总是与一些粗略的微调范围重叠,从而消除VCXO响应中可能存在漏洞。不同的晶体翘曲特性可以改变Y轴上的结垢,但不能改变。曲线的总体特征。

4.5水晶圈该晶体环设计用于衰减高抖动、低Q、低频基准上的抖动。水晶圈也可以如果低频参考是间歇性的,则保持主回路的恒定频率输出。晶体环路由一个电压可控晶体振荡器(VCXO)、一个分频器、一个PFD和一个调谐VCXO的电荷泵组成频率参考。频率基准被锁相到外部高Q无抖动晶体的分频,从而将VCXO锁定到参考频率。即使频率基准,VCXO也可以继续从晶体中逸出变得断断续续。4.5.1条。锁定到外部频率源当晶体回路与外部频率源同步时,FS6131可以监视晶体回路并检测该回路是否从外部源解锁。如果外部电源断开,crystal loop将尝试驱动至零频率,并设置一个锁状态错误标志。晶体环路还可以检测VCXO是否已退出微调范围,需要更改为粗调。锁状态还锁定回路解锁时超出范围(高或低)的方向。4.5.1.1水晶环锁状态标志要启用此模式,请将STAT[1]和STAT[0]位清除为零。如果CMOS位设置为1,则如果水晶环解锁。通过读取STAT[1]位,该标志在软件控制下始终可用,即在此模式下用状态标志(低=解锁)覆盖(见表)。4.5.1.2超出范围高/低可以通过清除STAT[1]为零并将STAT[0]位设置为1来确定循环超出范围的方向。如果CMOS位设置为1,如果晶体回路超出范围上限,锁/IPRG引脚将变高。如果引脚进入逻辑低位,则循环超出范围低。在软件控制下,也可以通过读取STAT[1]位来获得超出范围的信息,该位被标志覆盖(高=超出范围高,低=超出范围低)在此模式下。只有在crystal循环失去锁定时才设置或清除该位(见表)。

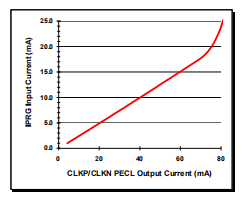

4.5.1.3晶体回路禁用通过将XLPDEN位设置为逻辑高(1),crystal循环被禁用。该位禁用环路中的电荷泵电路。设置XLPDEN位低(0)允许水晶环作为控制环运行。4.6将FS6131连接到外部参考频率如果不使用晶体振荡器,将XIN接地并通过设置XLROM[2:0]=1关闭晶体振荡器。REF和FBK引脚没有上拉或下拉电流,但是有少量的滞后以减少额外的边缘。信号可以通过外部直流偏置电路交流耦合到这些输入端,以产生2.5V的直流偏置参考或反馈信号应为方形,以获得最佳效果,信号应为轨对轨。未使用的输入应接地以避免不必要的信号注入。4.7差动输出级差分输出级同时支持CMOS和伪ECL(PECL)信号。所需的输出接口通过程序寄存器(见表)。如果使用PECL接口,则通常使用Thévenin终端来终止传输线。输出级只能下沉PECL模式下的电流,以及由LOCK/IPRG引脚上的编程电阻器设置的汇电流量。IPRG比率输出驱动电流的电流如图所示。源电流由作为Thévenin一部分的上拉电阻器提供终止。