特点

具有同步整流功能的DAC/电压监视器和PWM组合

5位数模转换器

1%DAC/参考组合精度

与5V和12V系统以及仅12V系统兼容

低偏移电流检测放大器

可编程振荡器频率,适用于700kHz

折叠限流

过压和欠压故障窗口

2Ω图腾极输出,具有可编程死区时间,以消除交叉传导

芯片禁用功能

带5位DAC的平均电流模式同步控制器

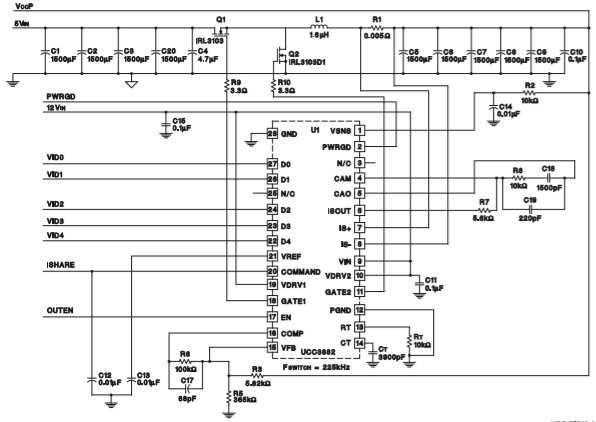

方块图

UDG-97047-1型

说明UCC3882将高精度参考电压监测电路与平均电流模式的PWM同步整流控制器电路结合起来,为具有最少外部组件的高端微处理器供电。UCC3882以1%的直流系统精度,将5V或12V转换为50mV步进范围为1.8VDC至2.05VDC、100mV步进范围为2.1VDC至3.5VDC的可调输出。

DAC输出电压与Intel的5位VID代码(表1)直接兼容,该代码以50mV为步进覆盖1.3V到2.05V,以100mV为步进覆盖2.1V到3.5V。DAC/参考组合的精度优于1%。欠压锁定电路确保在通电和断电期间输出的逻辑状态正确。过压和欠压比较器监测系统输出电压,并指示何时高于或低于其设计值9%以上。当系统输出电压超过其设计值17.5%以上时,第二个过电压比较器以数字方式强制关闭GATEHI并打开GATELO。

绝对最大额定值

VDRVHI,GATEHI(注1)。. . . . . . . . . . . . . . . . –0.3伏至20伏

维德韦洛,盖特洛。. . . . . . . . . . . . . . . . . . . . . . –0.3V至15V

所有其他与GND有关的管脚。. . . . . . . . . . . . –0.3伏至5.3伏

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +15伏

储存温度。. . . . . . . . . . . . . . . . . . –65°C至+150°C

结温。. . . . . . . . . . . . . . . . . . –55°C至+150°C

铅温度(焊接,10秒)。. . . . . . . . . . . . +300摄氏度

电流存储到,负输出到指定的终端。关于热变形和包装注意事项的数据手册包装部分。

注1:20V无负载。Derateto18.5V串联使用的电容负载大于1000pF,小于20Ω。

说明(续)

对于所有部件,将EN引脚接地将禁用GATEHI和GATELO输出,并关闭电源。仅对于2882和3882,对低于1.8V的DAC输出电压进行编程,或对所有VID引脚进行高编程,也会禁用GATEHI和GATELO输出。对于“–1”选项部分,GATEHI和GATELO输出正在切换,并且电源输出电压在所有VID代码的编程DAC输出电压下进行调节。

电压和电流放大器具有2.5MHz的增益带宽积,以满足高性能系统的要求。内部电流检测放大器允许使用一个低值电流检测电阻,最大限度地降低功率损耗。振荡器频率是外部的-

管脚说明

凸轮:这个引脚是电流放大器的反向输入。来自ISOUT引脚的平均负载电流反馈通过电阻器施加到该引脚。电流回路补偿网络也连接到此管脚(见下面的CAO)。

曹:这个引脚是电流放大器的输出。电流环补偿网络连接在该引脚和凸轮引脚之间。该引脚上的电压是PWM比较器的输入,并调节系统的输出电压。在这个输出电压范围从0.5V以下(迫使0%占空比)到2.5V以上迫使最大占空比。3V钳位电路可防止氧化钙电压过度升高,超过振荡器峰值电压,从而获得良好的瞬态响应。

公司:这个引脚是电压误差放大器的输出电压。系统电压补偿网络应用于COMP和VFB之间。当输出短路时,使用1.37V钳位命令强制电源进入限流模式。有关电流限制的编程,请参阅应用程序部分。

命令:该引脚是5位数模转换器(DAC)的输出,是电压误差放大器的非逆变输入。此引脚上的电压设置开关调节器输出电压。根据表1,指令电压由DAC输入引脚D0-D4设置。命令源阻抗通常为1.2kΩ,因此,如果要保持精度,则必须仅驱动高阻抗输入。带0.01μF、低ESR、低ESL电容器的旁路命令,以获得最佳的电路抗噪性。

计算机断层扫描:该引脚与RT一起用于编程内部PWM振荡器频率。使用高质量的电容器以获得最佳的振荡器精度。有关振荡器的编程,请参阅应用程序部分。

D0-D4:这些是DAC的数字输入控制代码(见表1)。DAC由D4设置的两个范围组成,D0表示最低有效位(LSB)和D3表示最高有效位(MSB)。一位通过接地设置为低;一位通过浮动或连接到5V电源设置为高。每个控制销通过内部上拉被拉高到大约5V。

英语:此输入用于禁用GATEHI和

GATELO输出,导致禁用电源。将EN拉到GND会导致GATEHI和GATELO输出保持在低位,而浮动管脚或将其拉到5V可确保正常工作。EN内部被拉高至5V。

盖蒂:该输出提供一个低阻抗图腾极驱动器来驱动高侧外部MOSFET。建议在该引脚和外部MOSFET的栅极之间设置一个串联电阻,以防止栅极驱动振铃和过冲。应使用良好的布局技术,以防止GATEHI在PGND以下的铃声超过0.3V。VDRVHI引脚为GATEHI引脚提供电源。在UVLO和过电压条件下,GATEHI被禁用。仅对于2882/3882,当指令电压编程设定在1.3到1.75V之间时,或当D0-D4引脚均为逻辑高电平时,GATEHI也被禁用,表示不存在处理器。

引脚说明(续)

盖特洛:该输出提供一个低阻抗图腾极驱动器来驱动低边同步外部MOSFET。建议在该引脚和外部MOSFET的栅极之间设置一个串联电阻,以防止栅极驱动振铃和过冲。应使用良好的布局技术,以防止GATELO在PGND以下振铃超过0.3V。VDRVLO引脚为GATELO提供电源。在UVLO条件下,GATELO被禁用。仅对于2882/3882,当指令电压编程设定在1.3到1.75V之间时,或当D0-D4引脚均为逻辑高电平时,GATELO也被禁用,表示不存在处理器。

地面:设备的接地参考。除栅极电压外,所有电压都是相对于GND测量的。VIN、VREF、VSNS和COMMAND上的旁路电容器应直接连接到接地附近的接地平面。

是-:该引脚是电流检测放大器的反向输入,并连接到平均电流检测电阻器的低端。

IS+:该引脚是电流检测放大器的非反相输入,并连接到平均电流检测电阻器的高压侧。

ISOUT公司:这个引脚是电流检测放大器的输出。该引脚上的电压等于传感电阻上的电压乘以16,再加上指令电压。此电压用于平均值

电流模式控制和限流。

PGND:第页该引脚为输出门驱动器提供专用接地。GND和PGND引脚应使用短PC板轨迹或平面进行外部连接。使用至少0.1μF的低ESR电容器将VDRVHI和VDRVLO与PGND分离。

PWRGD:该引脚是一个开漏输出,当VSN高于或低于其标称值9%时,驱动低电平复位微处理器。开路漏极开关的接通电阻将不高于470Ω。该输出应被拉高到逻辑电平电压,并应编程为接收1毫安或以下。

室温:此引脚与CT一起用于编程内部的脉冲宽度调制振荡器频率。它还用于编程外部MOSFET通断周期之间的延迟时间,从而消除这些MOSFET中的交叉传导。有关振荡器编程和控制交叉传导的信息,请参阅应用部分。

VDRVHI公司:该引脚为高端输出驱动器GATEHI供电。将VDRVHI连接到18V或更低电压源(用于将12VDC转换为更低电压的电源),并连接到12V电压源(用于将5VDC转换为更低电压的电源系统)。应使用低ESR电容器将该引脚直接旁路至PGND。

VDRV低:该引脚为低端输出驱动器GATELO供电。VDRVLO通常连接到12V电源,但也可以连接到5V电源以驱动逻辑电平mosfet。应使用低ESR电容器将该引脚直接旁路至PGND。

车辆识别号:这个引脚为芯片供电。将车辆识别号(VIN)连接到一个稳定的电压源,该电压源至少高于接地电压10.8伏。GATEHI、GATELO和PWRGD输出将保持在低位,直到VCC超过上限欠压锁定阈值。该引脚应直接绕过接地。

心室颤动:该引脚是误差放大器的反向输入。该输入通过反馈网络连接到COMP,并通过电阻器或分压器网络连接到电源输出。

参考电压:该引脚提供准确的5V参考电压,内部短路电流受限。VREF为D/A转换器供电,同时也为UVLO比较器提供阈值电压。为了获得最佳的参考稳定性,使用至少0.01μF的低ESR、低ESL电容器直接将VREF旁路至GND。

虚拟存储网络:该引脚通过低通R-C滤波器连接到系统输出电压。当VSN上的电压高于或低于指令电压9%时,PWRGD输出被驱动为低输出,以重置微处理器。当VSN上的电压高于命令电压17.5%时,OVP比较器将禁用GATEHI输出并启用GATELO输出,从而强制电源上的占空比为0%。该引脚也被折叠限流电路用来指示输出电压何时短路。VSN应与集成电路非常紧密地分离,并带有一个接地电容器。OV和UV比较器的滞后通常为20mV,需要良好的布局和滤波技术,以确保噪声和地面反弹不会无意中使OV和UV比较器跳闸。建议将设置为大约FS/10的R—C滤波器用于从系统输出中滤除噪声,其中Fs是振荡器频率。

DAC信息

5位数模转换器(DAC)根据表1进行编程。只要UCC3882车辆识别号引脚高于欠压锁定电压,指令电压始终处于激活状态。仅对于2882/3882,输出门驱动GATEHI和

应用程序信息

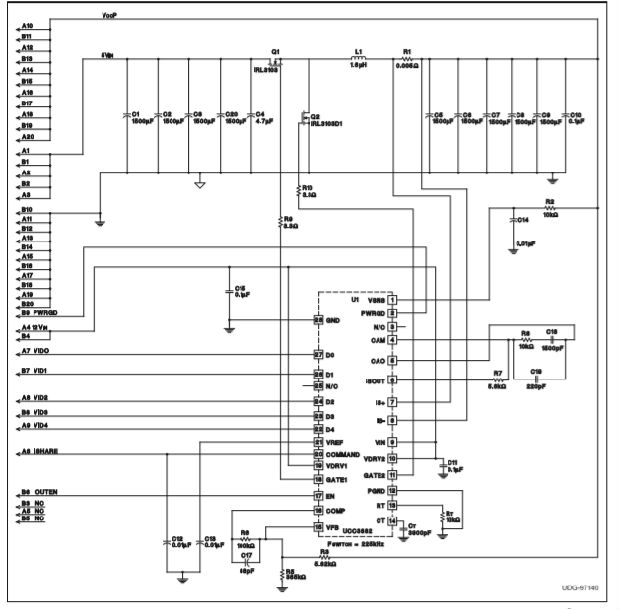

该集成电路用于高性能电源,为奔腾II或类似处理器供电。图1显示了一个典型的电源应用电路,它将+5V转换为奔腾II处理器所需的较低电压。®®

同步切换延迟时间

Buck和同步Buck调节器之间的基本区别是

而不是肖特基二极管作为低边或自由旋转开关。

为了保持同步降压稳压器的安全高效运行,mosfet(Q1和Q2)不应同时开启。同时打开两个mosfet会导致交叉传导,这会导致一个或两个mosfet的功耗过高。UCC3882在一个MOSFET的关闭和另一个MOSFET的打开之间有一个内置的延迟。此延迟是GATEHI和GATELO驱动输出之间的受控延迟,可通过选择电阻RT进行编程。控制GATEHI和GATELO驱动输出之间的延迟只是解决方案的一部分。电源设计人员还必须了解涉及MOSFET开启、关闭、上升和下降时间的固有延迟,以确保没有交叉传导。

建议RT使用10kΩ到15kΩ之间的值,这将使延迟最小化,并可导致最高效率的操作。较高的RT值将导致MOSFET栅极跃迁之间的较大延迟。RT应在10K最小值和50K最大值之间。

振荡器编程

对振荡器编程的第一步是如上所述选择RT的值。第二步是根据图3所示的曲线,通过选择适当的电容值来编程频率。

为了方便起见,使用标准电阻和电容值的100kHz至700kHz的标称频率值。

栅极驱动信号之间的延迟时间过长,或延迟时间太小,将导致电源设计效率低下。振荡器编程的第三步是观察实际电路波形,以确保延迟是最佳的。设计者应相应地改变RT和CT,以调整延迟时间并编程适当的振荡器频率。

与低边MOSFET并联使用外部肖特基二极管

使用同步降压稳压器的目的是用低压降MOSFET代替肖特基二极管作为低压侧开关。然而,仍然需要外部肖特基二极管,以减少由于低压侧MOSFET体二极管的反向恢复而造成的损耗。图4说明了由于典型的MOSFET体二极管的非理想性质对功率损耗的影响。IRM为Q2体二极管的峰值恢复电流,ILOUT为输出电感的电流。采用并联肖特基二极管可以降低这些损耗,提高电路效率。二极管的尺寸应随负载电流、输入电压和工作频率的变化而增大。二极管应尽可能接近较低的MOSFET,Q2,以减少杂散电感。

应用程序信息

选择RSENSE设置电流限制

短路电流限值与开关稳压器的输出电感值和工作频率的函数关系不大,因为纹波电流的高值会降低平均短路电流限值。给定UCC3882公共值时Isc的变化。UCC38 822名义上配置,使0.00 5MΩ电阻将电流限制设置为约17A。

UCC3882包含短路电流折叠,当电源输出短路时,输出电压下降。当输出电压达到其标称电压(命令/2)的1/2时,输出电流减小。此特性减少了mosfet和电容器中的电流量,并确保了高可靠性。

选择VDRVLO、VDRVHI和VIN

UCC3882要求在车辆识别号处提供标称12伏输入。VDRVLO和VDRVHI可以设置为低于18.5V的任何电压,并且可以单独设置。从+5V获得电源的电源应在VDRVHI管脚处使用+12V,但根据同步低边MOSFET的驱动要求,可以使用+5V或+12V。从+12V获得功率的电源应在VDRVHI处使用+18V,以便为高侧MOSFET提供足够的电压(6V)栅极驱动。车辆识别号必须小于+15V。

输入电容器

输入电容器的选择主要基于其开关频率均方根电流处理能力和电压额定值。即使电路没有输入电感,输入电容器也必须在开关频率下处理几乎所有的均方根电流。输入电容器中的开关电流如图7所示。

可使用铝或钽电容器。电解电容器中均方根电流的大小对电容器的可靠性和寿命有很大的影响。影响输入电容器寿命的其它因素是内部热上升、外部气流、电路在最大电流下工作的时间量和操作电压。图8中的曲线显示了典型电压为5V或12V的VRM电路中由总输入电容处理的均方根电流。

申请资料(续)

英特尔奔腾II处理器的UCC3882 5位同步整流器PWM控制器