1149点击型号即可查看芯片规格书

特征

用于配置锡林克斯燃气

低功耗先进CMOS NOR闪存工艺

持续20000个程序/擦除周期

在整个工业温度范围内运行(-40°C至+85°C)

IEEE标准1149.1/1532边界扫描(JTAG)对编程、原型和测试的支持

标准fpga的jtag命令启动配置

可级联存储较长或多个比特流

专用边界扫描(JTAG)I/O电源(VCCJ)

I/O引脚与以下电压等级兼容1.5伏至3.3伏

使用Xilinx Alliance ISE和基础ISE系列软件包

XCF01S/XCF02S/XCF04S

-3.3V电源电压

-串行现场可编程门阵列配置接口(高达33兆赫)

-提供小型VO20和VOG20

包装。

XCF08P/XCF16P/XCF32P

-1.8V电源电压

-串行或并行FPGA配置接口(最高33兆赫)

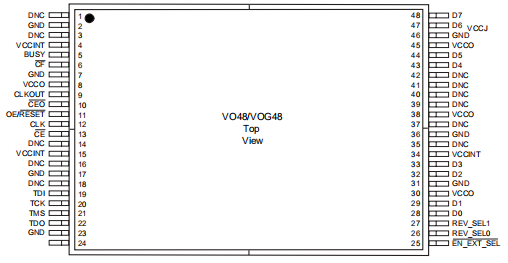

-提供小型VO48、VOG48、FS48,和fsg48包

-与Xilinx兼容的内置数据解压器先进的压缩技术

说明

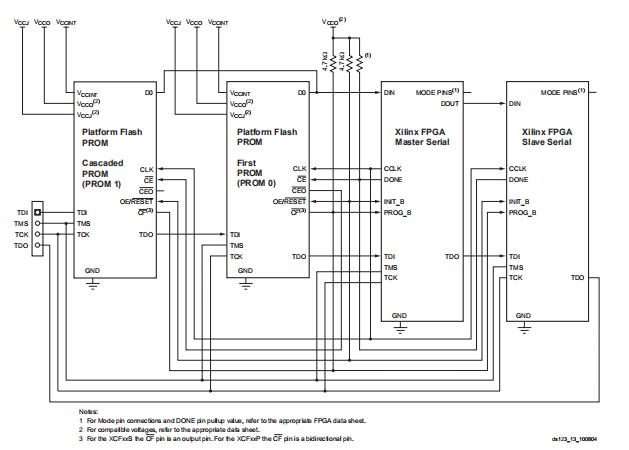

xilinx介绍了平台flash系列系统内可编程配置proms。有1到32种兆位(mbit)密度,这些prom提供易于使用、成本效益高且可重新编程的方法用于存储大型xilinx fpga配置位流。这个平台Flash PROM系列包括3.3V和xcfxs prom和1.8v xcfxp prom。xcfxs版本包括4-Mbit、2-Mbit和1-Mbit PROMs支持主串行和从串行的fpga配置模式。XCFxxP版本包括32mbit,支持主串行的16mbit和8mbit prom,从串行、主选择映射和从选择映射fpga配置模式。对平台flash prom系列成员和支持的功能如表1所示。

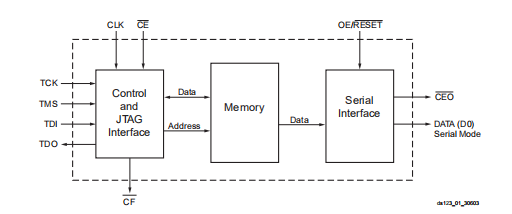

xcfxs平台flash prom框图

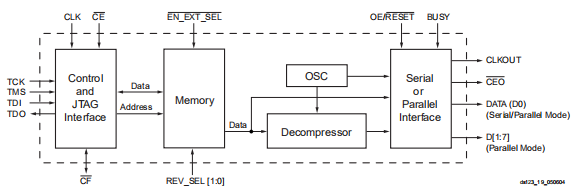

xcfxp平台flash prom框图

当fpga处于主串行模式时,它会生成驱动PROM的配置时钟cf高,aCE和OE启用后的短访问时间,数据为在连接到的PROM数据(D0)引脚上可用FPGA的DIN管脚新数据可短时间访问每一个上升时钟边缘后的时间。fpga生成适当数量的时钟脉冲来完成配置。

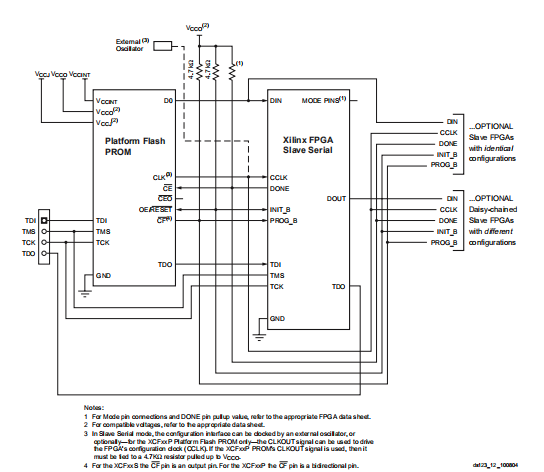

当FPGA处于从串行模式时,PROM和fpga都由外部时钟源进行时钟,或者可选地,仅对于xcfxxp prom,prom可以是用于驱动fpga的配置时钟。平台flash prom的xcfxxp版本还支持主选择映射和从选择映射(或从并行)fpga配置模式。当FPGA在主选择映射模式,FPGA生成驱动PROM的配置时钟当FPGA处于从机状态时选择映射模式,外部振荡器将生成驱动prom和可选择使用fpga或xcfxxp prom驱动fpga的配置时钟。忙得不可开交cf高,在ce和oe被启用后,数据在PROMs数据(D0-D7)管脚新数据可用每个上升时钟边缘后的短访问时间。数据是在下面的上升沿CCLK公司。一个自由运转的振荡器可以用在从机上并行/从SelecMAP模式。

平台Flash PROM的XCFxxP版本提供其他高级功能。内置数据解压器支持使用压缩的prom文件,并且设计修订允许将多个设计修订存储在单个舞会或跨多个舞会存放。用于设计修正,外部引脚或内部控制位用于选择激活的设计版本。

多平台Flash PROM设备可以级联到当瞄准更大的fpga设备或瞄准多个fpgas雏菊时,支持所需的更大配置文件锁在一起使用高级功能时xcfxxp平台flash prom,如设计修改、跨级联prom的编程文件只能为包含只有xcfxp proms。如果高级xcfxp功能是未启用,则级联链可以包括xcfxxp和xcfxs proms。

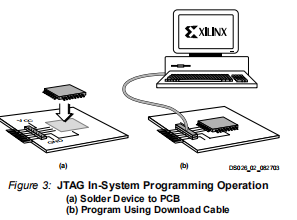

程序设计

系统内编程系统内可编程proms单独地,或两个或更多可以菊花链在一起并通过标准4针JTAG在系统中编程协议如图3所示。系统内编程提供快速有效的设计迭代,并消除不必要的包装处理或设备插接。这个编程数据序列传送到设备使用xilinx impact软件和xilinx下载有线电视,第三方JTAG开发系统JTAG兼容板测试仪,或一个简单的微处理器模拟JTAG指令序列的接口这个冲击软件还输出串行矢量格式(SVF)与任何接受svf格式的工具一起使用的文件,包括自动测试设备。在系统编程过程中,首席执行官的产出被推高。所有其他输出都保存在高阻抗状态或在在系统编程中系统内编程完全在建议的工作电压和

温度范围。

运行经验/重置系统中的1/2/4mbitxcfxs平台Flash PROMs编程算法导致内部设备复位,导致运行经验/复位脉冲低。

外部编程xilinx可重编程proms也可以通过xilinx多处理器桌面工具或第三方设备程序员。这提供了使用的附加灵活性。

具有系统内可编程的预编程设备用于未来增强和设计更改的选项。

可靠性和耐久性Xilinx系统内可编程产品保证系统内程序/擦除的持久性级别为20000周期和至少20年的数据保留期。每个设备满足所有功能、性能和数据保留要求在此耐久极限内的规格。

设计安全性Xilinx系统可编程平台Flash PROM设备集成了高级数据安全功能防止未经授权的fpga编程数据通过JTAG阅读。xcfxp proms也可以是pro编程以防止通过jtag意外写入。

读保护

用户可以设置read protect安全位,以防止内部编程模式被读取或通过JTAG复制。读保护不阻止写操作。对于xcfxs prom,将为整个设备设置读保护安全位,重置读保护安全位需要擦除整个设备。对于xcfxxp prom可设置读保护安全位单独的设计修订,并重置读保护bit需要删除特定的设计修订。

IEEE1149.1边界扫描(JTAG)平台Flash PROM系列是IEEE标准1532系统内编程兼容,完全兼容使用ieee标准1149.1边界扫描,也称为JTAG,是IEEE标准1532边界扫描的一个子集。

提供测试访问端口(TAP)和寄存器,以支持所有必需的边界扫描指令,以及许多由ieee标准指定的可选指令。1149.1年。此外,JTAG接口用于实现系统内编程(ISP),便于在平台闪存上进行配置、擦除和验证操作可编程只读存储器设备表6列出了必需的和可选的平台flash支持的边界扫描指令舞会。参考ieee标准1149.1规范边界扫描体系结构和必需和可选说明。

指令寄存器平台flash prom的指令寄存器(ir)在指令期间连接TDI和TDO扫描顺序。为指令扫描做准备顺序,指令寄存器并行加载固定指令捕获模式。这种模式被改变了转到TDO(首先是LSB),同时将指令移到来自TDI的指令寄存器。xcfxs指令寄存器(8位宽)xcfxs PROM的指令寄存器(IR)是8位宽,在指令扫描序列。的详细组成这个指令捕获模式移出xcfxs设备包括红外光谱[7:0]。IR[7:5]是保留位,设置为逻辑“0”。isc status字段ir[4]包含逻辑“1”,如果设备当前处于系统配置(ISC)模式;否则,它包含逻辑“0”。安全域,ir[3],包含逻辑“1”,如果设备已编程安全选项已打开;否则,它包含逻辑“0”IR[2]未使用,并且设置为“0”剩下的部分按照IEEE标准1149.1的定义,IR[1:0]设置为“01”。xcfxp指令寄存器(16位宽)xcfxxp prom的指令寄存器(ir)宽16位,在指令扫描序列中连接在tdi和tdo之间。

指令捕获模式从xcfxp移出设备包括红外线[15:0]。ir[15:9]是保留位,并且设置为逻辑“0”。ISC错误字段IR[8:7]包含“10”当ISC操作成功时;否则在系统内配置(ISC)操作失败。这个erase/program(er/prog)错误字段,ir[6:5],包含当擦除或程序操作成功时为“10”;oth当擦除或程序操作失败时,输入“01”这个erase/program(er/prog)status字段ir[4]包含当设备忙于执行擦除或编程操作;否则,它包含逻辑“0”。如果设备是当前处于系统配置(ISC)模式;否则,它包含逻辑“0”。done字段ir[2]包含逻辑“1”如果抽样设计修订成功编程;否则,逻辑“0”表示不完整编程。其余位ir[1:0]设置为'01'由IEEE标准1149.1定义边界扫描寄存器用于控制和观察在EXTEST、SAMPLE/PRELOAD和CLAMP指令期间设备管脚的状态每个输出引脚平台上的flash prom有两个寄存器级参与边界扫描寄存器,而每个输入pin只有一个寄存器级。双向引脚具有共有三个登记阶段边界扫描寄存器。对于每个输出管脚,寄存器最接近TDI的阶段控制并观察输出状态,最接近时差控制和观测的第二阶段输出引脚的高Z启用状态对于每个输入引脚,一个寄存器级控制并观察输入状态别针的。双向管脚结合了三个位,首先是输入级位,然后是输出级位和最后输出使能阶段位。输出启用阶段bit最接近tdo。

See the XCFXS//XCFXP PIN names and descriptionsTables in the Pinouts and Pin descriptions section for the所有连接设备的边界扫描比特命令,或See the appropriate BSDL file for the complete boundary-scan bit order description under the attribute“BSDL文件中的边界` U register'部分”。比特分配到边界扫描单元0“是边界扫描寄存器中的LSB,并且是寄存器位封闭到TDO。识别寄存器IDCode RegisterIDCODE是一个固定的,销售商指定的价值被使用。

电气识别制造商与类型设备作为地址IDCode register is 32 bits广阔IDCODE register can be shifted out for examination by using the IDCODE instruction.IDCODE可通过JTAG提供任何其他系统组件。Table 7 Lists该IDCOD Register Values for the Platform Flash Proms.The IDCODE register has the following binary format:哪里

模板版本号码Prom Family Code特殊平台闪光灯产品标识c=The Xilinx Manufacturer'“IDCODE register's always read as logic”As defined by IEEE STD.1149.1.

用户寄存器使用者指令为32位用户提供存取可编程scratch pad typeically used to supply information about the device''s programmed contents.使用用户指令,一个用户可编程的识别码可以被移除以供检查。这个代码是在编程过程中装入用户寄存器闪电平台如果设备是布朗克或不是布朗克在编程过程中装载,用户寄存器包ffffffffh。

客户代码寄存器对于XCFXP平台闪光灯,添加到用户代码,一个32-byte的用户代码可以是为每一个设计复习设置的PROM。

用户代码是在编程过程中设置的,并且通常用于提供关于设计修订的信息。

Contents.需要一个私人JTAG指令阅读客户代码如果晋升是空白的,或是顾客选择性设计修订的代码在装载期间未装载。编程,或如果特殊设计修订顾客代码将包含所有人。

平台闪光灯

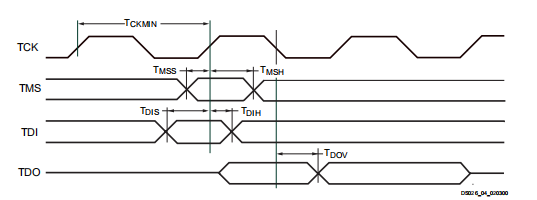

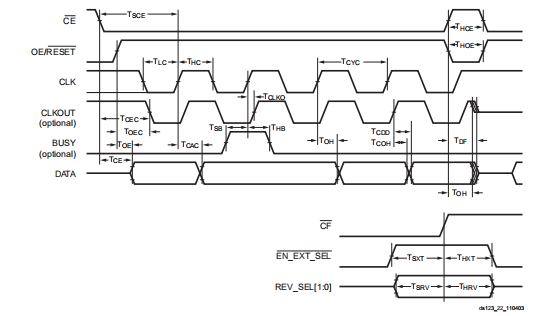

特性系统中的闪光灯平台编程和IEEE 1149.1边界扫描(JTAG)测试通过单个4-Wire测试接入端口(“TAP”)。简化系统设计与配置标准自动测试设备实现两种功能。下面描述了平台闪光灯前锥的AC特性。

锥度定时

这些定时特性对双方都是一样的。

边界扫描与ISP操作。

xcfxp的附加功能内部振荡器8/16/32 mbit xcfxp平台flash proms包括一种可选的内部振荡器,可用于驱动配置接口上的时钟和数据管脚。

内部振荡器可以在设备编程期间启用,并且可以设置为默认频率或以较低的频率(级联时工作条件下的交流特性)。

克尔考特8/16/32 mbit xcfxp平台flash proms包括启用CLKOUT信号的可编程选项它允许prom提供一个同步源时钟与配置接口上的数据对齐这个clkout信号来自两个时钟源之一:CLK输入引脚或内部振荡器。输入时钟在PROM编程过程中选择源顺序。输出数据位于克尔考特。

clkout信号在编程期间启用,并且当CE低且OE/RESET高时激活。禁用时,CLKOUT引脚将进入高阻抗状态并应在外部拉高以提供已知的国家。

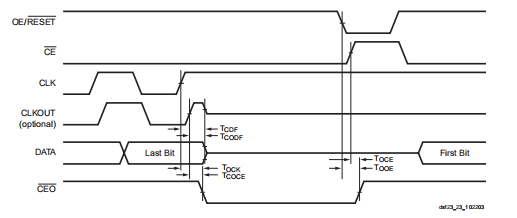

当使用clkout级联平台flash proms时启用,完成数据传输后,第一个prom禁用clkout并释放ceo pin以启用舞会连锁店的下一场舞会。下一场舞会就要开始了一旦prom启动,驱动clkout信号数据可供传输。

在没有压缩的高速并行配置中,FPGA驱动配置上的忙信号接口。当busy被断言为高时,proms内部地址计数器停止递增,并且当前数据值保存在数据输出上在忙碌的时候,舞会将继续向现场可编程门阵列,记录现场可编程门阵列的配置逻辑。当fpga解除asserts busy,表示它已经准备好接收附加配置数据,PROM将开始驱动配置界面上的新数据。

减压

8/16/32 mbit xcfxp平台flash proms包括与Xilinx advanced兼容的内置数据解压器压缩技术。压缩平台闪存prom文件是从目标fpga位流创建的使用Impact软件。只有从机串行和从机支持SelectMap(并行)配置模式使用用压缩比特流编程的XCFxxP PROM时的FPGA配置压缩率取决于几个因素,包括目标设备族和目标设计内容。

解压选项在PROM期间启用编程顺序。舞会减压在驱动时钟和数据到现场可编程门阵列的配置接口。如果减压是启用,则必须使用平台闪存时钟输出引脚(CLKOUT)作为配置的时钟信号接口,驱动目标FPGA的配置时钟输入引脚(CCLK)。PROM的CLK输入引脚或必须选择内部振荡器作为CLKOUT的源。任何连接到prom的目标fpga必须作为配置链中的从机运行,并且配置模式设置为从机串行模式或从机选择映射(并行)模式。

启用解压缩时,clkout信号变为最大控制时钟输出频率。当解压缩的数据未准备好时,clkout pin将进入high-z状态,必须将其拉高从外部提供已知状态。

启用解压缩时,将自动禁用忙输入。

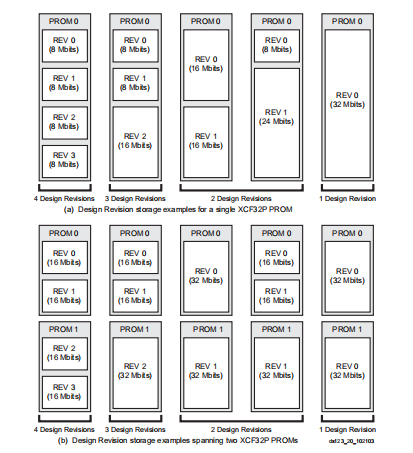

设计修改允许用户创建多达四个在单个PROM上或存储在多个级联prom8/16/32 mbit xcfxxp平台flash proms支持设计修改在串行和并行模式下。设计修改可以与压缩的prom文件一起使用,并且CLKOUT功能已启用prom编程文件与修订信息文件(.cfi)一起创建使用Impact软件。.cfi文件需要在Impact中启用设计修订编程。单个设计修订版由1到n 8-mbit组成内存块。如果单个设计修订包含的超过8mbits的数据,则剩余的空间被填充和所有人一起较大的设计修订可以跨越几个8-Mbit内存块,以及最后一个8-mbit内存块全部填充。

•一个32mbit prom包含四个8mbit内存块,因此最多可以存储四个独立的设计修订:一个32mbit设计修订,两个16mbit设计修订版,三个8mbit设计修订版,四个8-mbit设计修订版,依此类推。

•因为8-mbit的最小尺寸要求每次修订,一个16mbit的prom只能存储最多两个独立的设计修订版:一个16mbit设计修订,一个8-mbit设计修订,或两个8-mbit设计修订版。

•单个8-mbit prom只能存储一个8-mbit设计修订。

较大的设计修改可以分成几个级联舞会。例如,两个32mbit prom最多可存储四个独立的设计版本:一个64mbit的设计版本,两个32mbit设计修订,三个16mbit设计修订,四个16mbit设计修订,等等当级联一个16mbit PROM和一个8mbit PROM时,有24mbit的可用空间,因此最多可以存储三个独立的设计修订:一个24mbit设计修订版,两个8-Mbit设计修订版,或三个8-Mbit设计修订。

有关如何存储多个修订的一些基本示例,请参见图7在impact中的文件生成过程中,设计修订分区将自动处理。在prom文件创建过程中,每个设计版本分配了修订号:在用一组设计修订,特定的设计修订可以是使用外部rev_sel[1:0]引脚或使用内部可编程设计修订控制位。这个en_ext_sel pin确定外部pin还是内部pinBITS用于选择设计修订。什么时候?en_ext_sel低,控制设计修订选通过外部版本选择管脚,rev_sel[1:0]。什么时候?en_ext_sel高,设计版本选择由内部可编程版本选择控制位。通电期间,设计修改选择输入(管脚或控制位)在内部取样。通电后,当CE被断言(低)启用PROM输入时设计修改选择输入在cf脉冲的上升沿。从选定的然后在现场可编程门阵列(FPGA)配置接口上给出设计修改。

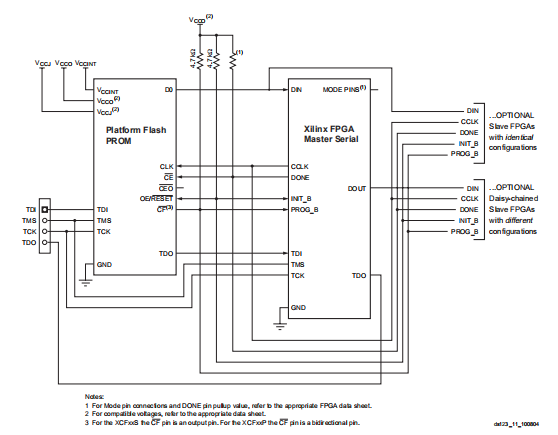

prom到fpga的配置模式和连接摘要FPGA的I/O、逻辑功能和内部互连由FPGA的比特流比特流被加载到可编程门阵列在通电时自动启动,或在命令下启动,取决于FPGA的模式管脚的状态锡林克斯平台flash prom设计为直接下载到现场可编程门阵列配置接口。现场可编程门阵列配置xcfxs平台flash支持的模式prom包括:主串行和从串行。xcfxxp平台flash proms支持的fpga配置模式包括:主串行,从串行,主选择映射和从选择映射。下面是一个短的支持的FPGA配置模式概述见用于设备配置的各自的fpga数据表详细信息,包括支持哪些配置模式通过目标的fpga设备。

主串行模式在主串行模式下,fpga自动加载来自外部存储器的位串行配置位流,由fpga生成的配置时钟(cclk)同步。在通电或重新配置时,使用fpga的模式选择管脚来选择主控芯片串行配置模式。主串行模式提供简单的配置界面。只有一条串行数据线时钟线和两条控制线(INIT和DONE)是需要配置一个fpga。舞会上的数据是在单个数据行(din)上按顺序读取,访问通过PROM的内部地址计数器,该计数器在CCLK的每个有效上升沿上递增。串行位流数据必须设置在FPGA的DIN输入引脚a上在fpga内部每个上升沿之前的短时间内生成CCLK信号。

通常,可以为fpga内部生成的cclk总是启动以缓慢的默认频率。fpga的比特流包含可将CCLK切换到更高频率的配置位,用于主串行配置的其余部分顺序。所需的cclk频率在比特流生成。

将fpga设备连接到配置prom主串行配置模式

PROM的数据输出驱动领先的fpga设备。

主fpga cclk输出驱动clk输入舞会的

prom的ceo输出驱动下一场舞会是菊花串(如果有的话)。

所有prom的OE/RESET引脚都连接到所有fpga设备的init_b管脚。这种联系确保PROM地址计数器在任何(重新)配置的开始。

PROM CE输入可由DONE引脚驱动。

可驱动第一个(或唯一一个)PROM的CE输入通过所有目标fpga设备的输出,前提是DONE没有永久接地总工程师也可以被永久性地固定在低位,但这样可以保持数据输出激活并导致不必要的ICC有功电源电流(直流特性超过操作条件)。

prom cf引脚通常连接到fpga程序输入。仅限XCFxP,cf引脚是双向引脚。如果xcfxxp cf pin是未连接到现场可编程门阵列的程序(或程序)输入时,应将针系在高处。

从串行模式在从串行模式下,fpga以位串行形式从外部存储器加载由外部提供的时钟同步的配置位流。通电后或重新配置时,使用了FPGA的模式选择管脚选择从机串行配置模式。从串行模式提供了一个简单的配置界面。只有一个串行数据线、时钟线和两条控制线(INIT和完成)是配置一个fpga所必需的。数据来自可编程只读存储器(PROM)在单个数据线上顺序读出,通过PROM的内部地址计数器访问在cclk的每个有效上升沿上递增。连续剧位流数据必须设置在fpga的din输入引脚a上在外部提供的每个上升沿之前的短时间CCLK公司。

将FPGA设备连接到配置PROM从串行配置模式:

•PROM的数据输出驱动领先的fpga设备。

•prom clkout(仅适用于xcfxp)或外部时钟源驱动fpga的cclk输入。

prom的ceo输出驱动下一场舞会是菊花链(如果有的话)。

所有prom的OE/RESET引脚都连接到所有fpga设备的init_b(或init)管脚。这个连接确保PROM地址计数器在任何(重新)配置开始之前重置。

PROM CE输入可由DONE引脚驱动。

可驱动第一个(或唯一一个)PROM的CE输入通过所有目标fpga设备的输出,前提是DONE没有永久接地总工程师也可以被永久性地固定在低位,但这样可以保持数据输出激活并导致不必要的ICC有功电源电流(直流特性超过操作条件)。

prom cf引脚通常连接到fpga程序输入仅限XCFxP,

cf引脚是双向引脚。如果xcfxxp cf pin是未连接到现场可编程门阵列的程序(或程序)输入时,应将针系在高处。

串联菊花链多个fpga可以通过菊花链从单个源进行串行配置在特定的现场可编程门阵列配置后,下一个设备的数据将在内部路由到现场可编程门阵列的双引脚。通常是dout上的数据CCLK下降沿上的销变化,尽管对于一些设置在cclk上升沿上的dout pin变化。

有关特定fpga设备的详细信息,请参阅相应的设备数据表。为了计时菊花链配置,在可以将chain设置为master serial,生成cclk,其余设备设置为从机串行。或者所有的fpga设备都可以设置为从串行和外部产生的时钟可以用来驱动fpga的配置接口。

FPGA主选择映射(并行)模式(1)在master selectmap模式下,字节范围的数据被写入fpga,通常有一个busy标志来控制数据,由fpga生成的配置时钟(cclk)同步。在通电或重新配置时,使用fpga的模式选择管脚来选择主控芯片选择映射配置模式。配置接口通常需要一条并行数据总线、一条时钟线和两条控制线(INIT和DONE)另外,FPGA的芯片必须正确控制选择、写入和忙碌管脚启用SelectMAP配置配置数据

在fpga的每个上升沿之前的短时间内内部生成的CCLK信号如果断言忙(高)通过现场可编程门阵列,必须保存配置数据直到忙得不可开交。外部数据源或外部必须使用下拉电阻器来启用FPGA的有源低芯片选择(CS或CS U B)和写入(写入或rdwr_b)启用fpga的selectmap配置过程的信号。主SelectMAP配置界面由fpga的内部振荡器。通常,可以为内部生成的CCLK选择宽范围的频率它总是以一个缓慢的默认频率开始现场可编程门阵列位流包含可切换的配置位对于主设备的其余部分,CCLK频率更高选择映射配置序列。在比特流生成期间选择所需的cclk频率。配置之后,selectMap端口的管脚可以是用作附加用户I/O。或者,端口可以是使用persist选项保留。

将FPGA设备连接到配置PROM主选择映射(并行)配置模式

PROM的数据输出驱动[d0..d7]主fpga设备的输入。

主fpga cclk输出驱动clk输入舞会的prom的ceo输出驱动下一场舞会是菊花链(如果有的话)。

所有prom的OE/RESET引脚都连接到所有fpga设备的init_b管脚。这种联系确保PROM地址计数器在任何(重新)配置的开始。

PROM CE输入可由DONE引脚驱动。

可驱动第一个(或唯一一个)PROM的CE输入通过所有目标fpga设备的输出,前提是DONE没有永久接地总工程师也可以被永久性地固定在低位,但这样可以保持数据输出激活并导致不必要的ICC有功电源电流(直流特性超过操作条件)。

对于高频并行配置,所有prom的管脚都连接到fpga的busy输出此连接确保下一个数据prom的转换被延迟,直到fpga为下一个配置数据字节做好准备。

prom cf引脚通常连接到fpga程序输入。仅限XCFxP,cf引脚是双向引脚。如果xcfxxp cf pin是未连接到现场可编程门阵列的程序(或程序)输入时,应将针系在高处。FPGA从机SelectMAP(并行)模式(1)在slave selectmap模式下,字节范围的数据被写入fpga,通常有一个busy标志来控制数据,由外部提供的配置同步时钟(CCLK)。在通电或重新配置时,使用fpga的模式选择管脚来选择从机选择映射配置模式。配置接口通常需要一条并行数据总线、一条时钟线和两条控制线(INIT和DONE)另外,FPGA的芯片必须正确控制选择、写入和忙碌管脚启用SelectMAP配置配置数据是从引脚[d0..d7]上的PROM逐字节读取,通过PROM的内部地址计数器访问在cclk的每个有效上升沿上递增。位流数据必须在fpga的[d0..d7]输入端设置在提供的CCLK公司。如果fpga断言busy(高),则必须保持配置数据,直到busy变低。外部的必须使用数据源或外部下拉电阻器启用现场可编程门阵列的活动低芯片选择(CS或CS-B)并写入(write或rdwr_b)信号以启用fpga的selectmap配置过程。

配置之后,selectMap端口的管脚可以是用作附加用户I/O。或者,端口可以是使用persist选项保留。

将FPGA设备连接到配置PROM从选择映射(并行)配置模式:

•PROM的数据输出驱动[D0..D7]主FPGA设备的输入。

•prom clkout(仅适用于xcfxp)或外部时钟源驱动fpga的cclk输入

•prom的ceo输出驱动下一场舞会是菊花链(如果有的话)。

•所有prom的OE/RESET引脚都连接到所有fpga设备的init_b管脚。这种联系确保PROM地址计数器在任何(重新)配置的开始。

•PROM CE输入可由DONE引脚驱动。可驱动第一个(或唯一一个)PROM的CE输入通过所有目标fpga设备的输出,前提是DONE没有永久接地总工程师也可以被永久性地固定在低位,但这样可以保持数据输出激活并导致不必要的ICC有功电源电流(直流特性超过操作条件)。

对于高频并行配置所有prom的管脚都连接到fpga的busy输出。这种连接保证了下一个

程序输入。仅限XCFxP,cf引脚是双向引脚。如果xcfxxp cf pin是未连接到现场可编程门阵列的程序(或程序)输入时,应将针系在高处。

fpga选择映射(并行)设备链(1)可以使用选择映射模式,并使其同时启动。要以这种方式配置多个设备,请将cclk、done、init、data([d0..d7])、write(write或rdwr_b)和所有设备的繁忙管脚并联。如果全部设备将配置为相同的位流,不使用回读,并选择CCLK频率不需要使用忙信号,CS\U B引脚可以连接到公用线,因此所有设备同时配置。

通过附加的控制逻辑,各个设备可以通过断言每个设备的CS_B pin分别加载依次启用相应的配置数据。

prom还可以存储每个可编程门阵列用于在单独的设计修订版中进行SelectMAP配置当使用设计修改时,附加控制逻辑可用于通过断言EN_EXT_SEL pin,并使用rev_sel[1:0]管脚选择所需的位流,而断言位流所针对的fpga的cs_b管脚。

为并行配置链计时,第一个链中的fpga可以设置为master selectmap,生成cclk,其余设备设置为slaveSelectMAP,或者所有的FPGA设备都可以设置为Slave可以使用selectmap和外部生成的时钟驱动配置接口同样,各自有关特定的fpga设备的详细信息,包括目标fpga设备支持的配置模式,应参考设备数据表。级联配置proms在串行菊花链中配置多个FPGA时,在selectmap并行链中配置多个fpga,或者配置需要更大配置位流的单个fpga,级联prom提供额外的内存。多平台flash prom可以通过使用ceo输出驱动下游设备的ce输入。所有的时钟信号和数据输出链中的平台flash prom是相互连接的。读取第一个PROM的最后一个数据后,第一个prom声称其ceo的产出很低,并将其产出驱动到高阻抗状态。第二场舞会其CE输入低电平,并立即启用其输出。

配置完成后,如果PROM OE/reset pin变为低或CE高。

使用XCFxxP平台Flash PROM的高级功能时,包括时钟输出(CLKOUT)选项,解压选项,或设计修改,跨级联prom设备的编程文件仅为仅包含xcfxp协议。如果不使用高级功能,然后级联prom链可以包含xcfxp和XCFXS项目。

启动fpga配置通过平台Flash PROM启动FPGA配置的选项包括:一开机时自动配置应用外部程序脉冲应用jtag config指令遵循FPGA的通电顺序或断言在PROG_B(或PROGRAM)管脚中,清除FPGA的配置存储器,选择配置模式,fpga已经准备好接受新的配置位流。可编程门阵列的程序B引脚可由外部源,或者平台flash proms合并一个可以绑定到fpga的cf pin程序B引脚。通过执行config指令JTAG对CF输出低脉冲一次,持续300-500纳秒,重置现场可编程门阵列并启动配置。影响软件可以发出jtag config命令来启动通过设置“加载fpga”选项进行fpga配置。

在设计中使用xcfxp平台Flash PROM时修正启用后,CF引脚应始终连接到现场可编程门阵列上的PROG B(或程序)引脚确保对当前设计修订选择进行抽样当fpga复位时。xcfxxp prom对从外部选择当前设计修订REV_SEL引脚或内部可编程版本选择cf上升沿上的位。当执行jtag config命令时,xcfxp将对新的启动fpga配置前的设计修改顺序。使用xcfxp平台flash prom时如果cf pin未连接到FPGA PROG_B(或PROGRAM)管脚,然后是xcfxpCF销应绑高。

配置prom到fpga设备接口连接图

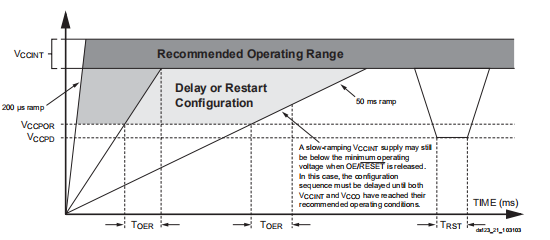

重置和上电重置激活通电时,设备需要VCCINT电源单调上升到额定工作电压指定的VCCINT上升时间如果电源不能满足此要求,则设备可能无法执行开机复位正常。在通电过程中,OE/复位被PROM保持在低位一旦要求电源已到达各自的端口(打开电源重置)阈值,运行经验/重置释放延迟(TOER最小)允许电源有更多的裕度在启动配置前保持稳定。OE/复位引脚连接到外部4.7KΩ上拉电阻器,并且到目标fpga的初始pin。对于使用缓慢上升电源的系统,额外的电源监控电路可用于延迟目标配置,直到系统电源通过保持OE/复位引脚低当运行经验/重置被释放时fpga的init pin被拉得很高,允许fpga的配置序列开始。如果功率降到掉电阈值(VCCPD),PROM复位OE/RESET再次保持在低位,直到达到POR阈值OE/复位极性不可编程。

对于全功率平台flash prom,会发生重置每当oe/reset被断言(低)或ce被解除(高)时。地址计数器复位,CEO被驱动高,其余输出处于高阻抗状态。

笔记:一xcfxs PROM只需要VCCINT高于在释放OE/RESET之前的POR阈值。

2.xcfxxp prom要求vccint都高于其por阈值和vcco达到释放前的推荐工作电压水平运行经验/重置。

输入/输出输入电压容限和功率排序每个可重新编程平台flash prom上的i/os完全3.3V耐受。这使得3V CMOS信号可以直接连接到输入端而不会损坏。核心力量电源(VCCINT)、JTAG引脚电源(VCCJ)、输出电源(VCCO)和外部3V CMOS I/O信号可按任何顺序应用。

此外,仅对于XCFXS PROM,当VCCO以2.5V或3.3V供电,而VCCINT以3.3V供电时,I/O可耐受5V电压这使得5V CMOS信号可以直接连接到电源xCFxS PROM的输入端没有损坏。当提供5伏输入信号可能导致xcfxs设备。

待机模式每当ce被解除资产(高)在待机状态下,地址计数器重新设置后,CEO会被激励得很高,剩下的输出是处于高阻抗状态,无论运行经验/复位输入。使设备保留在低功耗待机模式,JTAG引脚tms、tdi和TDO不能拉低,TCK必须停止(高或低)。用FPGA完成信号驱动PROM-CE时引脚高,以减少配置后的备用电源,应使用外部上拉电阻器。通常为330Ω使用上拉电阻,但请参考相应的fpga推荐的完成引脚上拉值的数据表。如果done电路连接到led以指示fpga配置已完成,并且还连接到prom ce pin启用低功耗待机模式,然后应使用外部缓冲器驱动LED电路确保PROM的CE引脚上有有效的转换。如果是低功率PROM不需要待机模式,然后CE引脚应该接地。

运行条件下的交流特性

级联时运行条件下的交流特性

XCFxP引线图