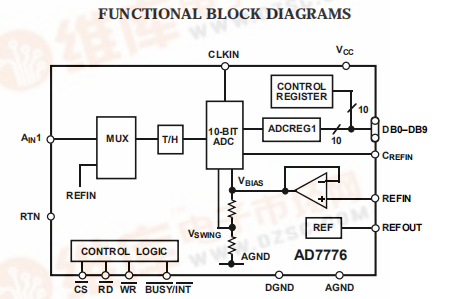

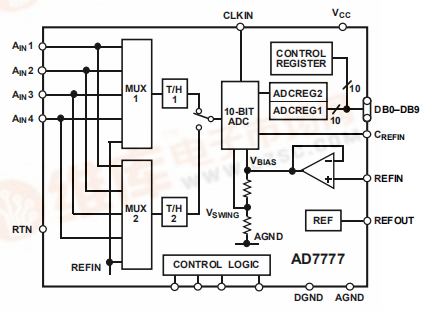

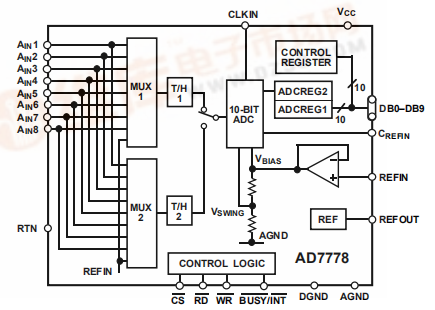

特征:AD7776:单通道;AD7777:4通道;AD7778:8通道;快速10位adc:2.5ms最坏情况;+仅5伏;半刻度转换选项;快速接口端口;断电模式。

应用:硬盘伺服;仪表。

一般说明

AD7776、AD7777和AD7778是一个高速家族,多信道,10位adc,主要用于r/w高密度硬盘驱动器中的磁头定位伺服。它们具有独特的输入信号调节功能,使它们是这种单一供应应用的理想选择。

通过在四通道内的控制寄存器中设置一个位版本AD7777和八通道版本AD7778,输入通道可以独立采样,也可以任意两个选择的通道可以同时采样。对于所有版本,指定的输入信号范围为vbias±vswing格式。然而,如果rtn管脚偏压在2v,比如所有输入的模拟输入信号范围变为0 V至+2 V频道。本节将详细介绍这一点改变模拟输入电压范围。电压Vbias是ADC中点代码与地面的偏移量由用户可用的车载参考提供(重新输出)或通过外部电压基准施加到雷芬。ADC的满标度范围(FSR)等于2垂直机翼,垂直机翼名义上等于refin/2。此外,当置于半刻度转换模式时,refin的值被转换。这允许信道偏移待测量。

控制寄存器加载和ADC寄存器读取、通道选择和转换启动由μP控制。两个互补编码的ADC通过其10位数据端口和标准接口轻松连接到标准16位MPU总线微处理器控制线路。

AD7776/AD7777/AD7778采用线性兼容CMOS(LC2)工艺制造一种先进的混合工艺将精密双极电路和低功耗CMOS结合在一起逻辑。AD7776有24针SOIC封装;以及AD7777可用于28针DIP和28针SOIC封装;AD7778可用于44针PQFP封装。

电路说明

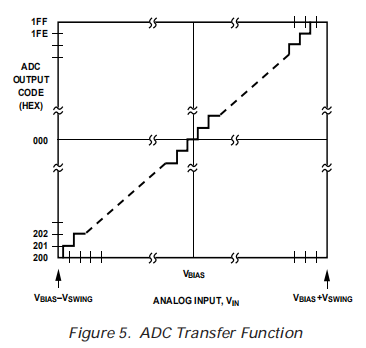

ADC传输函数

对于所有版本,都需要vbias±vswing形式的输入信号。此VBIAS信号电平作为伪接地工作,所有输入信号都必须参考。vbias电平由施加到refin引脚的电压决定。这可以由外部电压源驱动,或者,也可以使用在重新输出时可用的车载2 V参考电压。输入信号摆动的幅度等于vbias/2(或refin/2),并在内部设置。当refin为2v时,模拟输入信号电平从1v变化到3v,即2±1v。图5显示了adc的传输函数及其与vbias和vswing的关系。ADC的半标度二进位码,000十六进制(00 0000 0000二进制),在等于VBIAS的输入电压下出现。adc的输入满标度范围等于2vswing,因此正满标度转换(1fe到1ff)发生在等于vbias+vswing–1.5 lsbs的电压下,负满标度代码转换(200到201)发生在vbias–vswing+0.5 lsbs的电压下。

控制寄存器

控制寄存器宽10位,只能写入。通电时,控制寄存器中的所有位置都会自动加载0。对于单通道AD7776,控制寄存器的CR0到CR6位置是“不在乎”的。对于四通道AD7777,CR2和CR5位置是“不在乎”的。

CR0- CR2:频道地址位置。确定将为单通道操作选择和转换哪个通道。对于同时采样操作,CR0–CR2保存要采样的两个通道之一的地址。

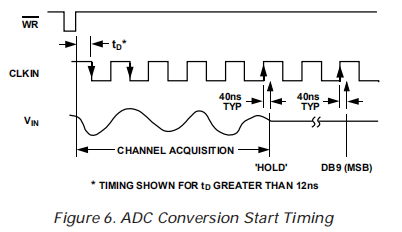

ADC转换开始计时

图6显示了启动con的工作波形-版本周期。在wr的上升沿上,转换周期从所选adc信道ain1–8的捕获和跟踪开始。在四个完整的clkin循环后clkin的第一上升沿之后,模拟输入电压保持40ns(通常)。如果图6中的td大于12ns,则如图所示的clkin下降沿将被视为第一个下降时钟沿。如果td小于12ns,则要识别的第一个下降时钟边缘在一个周期之后才会出现。

在模拟输入上“保持”之后,在做出msb决定之前,允许两个完整的clkin循环用于解决问题。实际判定点出现在clkin上升沿后约40ns处,如图6所示。第二个msb决策还允许两个clkin循环。在clkin的每个上升沿之后大约40 ns做出后续比特决定,直到转换完成。在转换结束时,如果一次转换已被请求(cr6=0),busy/int行改变状态(按cr9编程),sar内容被传输到第一个寄存器adcreg1。然后重设合成孔径雷达,准备进行新的转换。如果已请求同步采样(cr6=1),则busy/int输出,adc自动启动第二个转换。在转换结束时,busy/int行改变状态(如cr9所编程),sar内容被传输到第二个寄存器adcreg2。

跟踪和保持

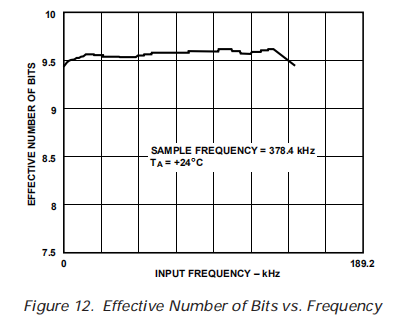

AD7776/AD7777/AD7778的模拟输入端上的跟踪保持(T/H)放大器允许ADC精确地将2V峰值振幅的输入正弦波转换为189 kHz的频率,即ADC以378 kHz的最大吞吐率工作时的奈奎斯特频率。此最大转换速率包括转换时间和转换之间的时间。因为trackand hold的输入带宽远远大于189khz,所以输入信号应该限制频带以避免将不需要的信号折叠到感兴趣的频带中。

停电

AD7776/AD7777/AD7778只需将逻辑高位写入控制寄存器的位置CR8,即可置于断电模式。将“1”写入位置CR8后,以下更改立即生效:

(1)、任何正在进行的转换都将终止。

(2)、如果正在进行转换,wr imedi的前缘-将busy/int输出设为高。

(3)、关闭所有线性电路。

(4)、重新输出输出停止驱动,并弱(5 kΩ)拉至模拟接地。

当AD7776/AD7777/AD7778断电时,控制输入CS、WR和RD保持其用途。如果在将AD7776/AD7777/AD7778置于断电模式时没有进行转换,则ADC寄存器的内容,ADCReg1和ADCReg2在断电期间保留可以正常阅读。在返回正常工作模式时,将自动启动新的转换(或转换,取决于CR6)。完成时,无效的转换结果将加载到ADC寄存器中,从而丢失先前的有效结果。

为了在断电模式下实现尽可能低的功耗,必须特别注意数字和模拟输入和输出的状态:

(1)、由于每个模拟输入通道都有一个电阻分压器接地,其输入电阻在正常模式和断电模式之间不会变化,因此将模拟输入信号驱动至0 V或尽可能接近0 V将使输入信号调节电路中消耗的功率最小化。

(2)、类似地,REFIN输入看到一个到AGND的电阻分压器,其输入电阻在正常模式和断电模式之间没有变化。如果使用外部基准,则将该基准输入驱动至0 V或尽可能接近0 V,将使输入信号调节电路中消耗的功率最小化。

(3)、由于重新输出引脚通常通过A5 kΩ电阻器拉至agnd,因此该输出可能被外部电路拉至0 V以上的任何电压都将消耗不必要的功率。

(4)、数字输入cs、wr和rd都应保持在vcc或尽可能接近。CLKIN应尽可能靠近0 V或VCC。

(5)、由于busy/int输出被主动驱动到逻辑高电平,因此该引脚上的任何0 V负载都将消耗功率。

当逻辑“0”写入控制寄存器的位置CR8时,AD7776/AD7777/AD7778退出掉电模式。请注意,当设备断电时,控制寄存器中其他位置的内容将被保留,当电源恢复时,这些内容将有效。但是,断电后,可以重新加载控制寄存器的完整内容,而无需任何额外指令。

微处理器接口电路

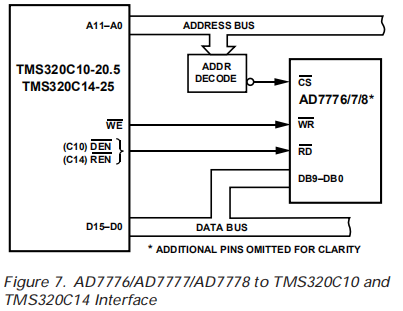

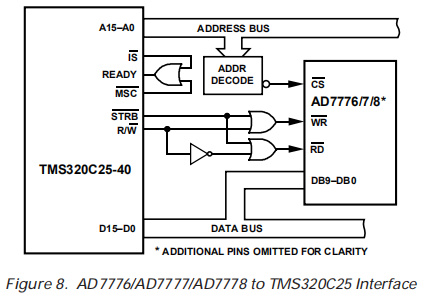

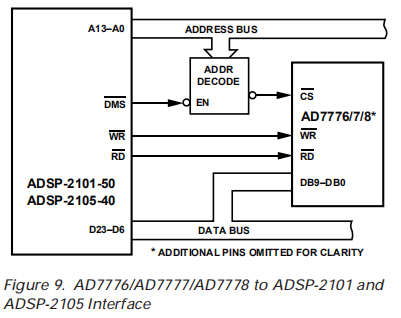

ADCs的AD7776/AD7777/AD7778系列旨在与ADSP-2101、ADSP-2105、TMS320系列和80C196系列微控制器等数字信号处理器(DSP)接口。

图7显示了AD7776/AD7777/AD7778与20.5兆赫的tms320c10和25兆赫的tms320c14的接口。

图8显示了40 MHz下与tms320c25的接口。

请注意:此接口需要一个等待状态。这个ADSP-2101-50和ADSP-2105-40接口如图9。这两台机器都需要一个等待状态。

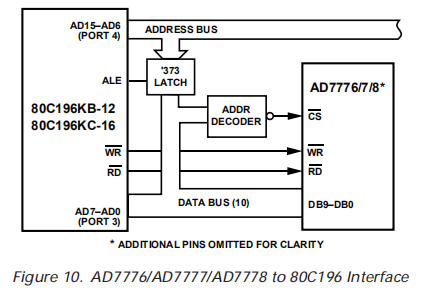

图10显示了与80C196KB@12MHz和80C196KC@16MHz的接口。16MHz机器需要一个等待状态。80C196配置为使用16位多路复用地址/数据总线操作。

请注意:在会话进行期间,对任何设备的读取指令将立即停止该转换并通过数据总线返回不可靠的数据。

设计信息

布局提示

确保印刷电路板的布局尽可能将数字和模拟接地分开。注意不要在模拟信号轨道旁边运行任何数字轨道。用rtn保护(屏幕)模拟输入。

建立一个独立于逻辑系统接地的单点模拟接地,并尽可能靠近AD7776/AD7777/AD7778。AD7776/AD7777/AD7778上的RTN和AGND引脚以及所有其他信号接地都应连接到此单点模拟接地。反过来,该星形接地应仅在一个点(最好是在低阻抗电源本身)连接到数字接地。

低阻抗模拟和数字电源公共回路对于设备的正确运行非常重要,因此要使这些轨道的箔宽度尽可能宽。

为了确保在实际的VCC管脚处有一个低阻抗+5V电源,将有必要使用从管脚本身到DGND的旁路电容器。4.7μf钽电容器与0.1μf陶瓷电容器并联就足够了。

ADC损坏

在转换过程中执行对AD7776/AD7777/AD7778的读取指令将立即停止Con-版本并通过数据总线返回无效数据。

当输出显示转换正在进行时,应密切监视int输出管脚,并防止对ad7776/ad7777/ad7778的所有读取指令。

在转换过程中执行对AD7776/AD7777/AD7778的写入指令会立即停止转换器-sion,wr的下降沿驱动busy/int输出高。模拟输入按正常采样,并启动新的转换序列(取决于CR6)。

模数转换器转换时间

尽管每次转换只需要14个clkin周期,但要获得模拟信号可能需要4.5到5.5个clkin周期

在wr输入变高之后和任何转换开始之前输入。

术语

相对精度

对于AD7776、AD7777和AD7778,相对精度或端点非线性是ADC实际代码转换点相对于在ADC传输函数端点之间绘制的直线的最大偏差(LSB)。

微分非线性

差分非线性是任意两个相邻码的测量变化和理想1lsb变化之间的差值。规定的最大差分非线性为±1 lsb,确保无漏码。

偏移误差

对于理想的10位adc,输入电压等于vbias的输出码应为中刻度。偏移误差是中尺度码的实际中点电压与vbias之间的差值,用lsb表示。

偏置误差匹配

这是测量所有通道的偏置偏移误差相互跟踪的程度。无论信道是独立采样还是同时采样,任何信道的偏置偏移误差匹配与任何其他信道的偏置偏移误差的距离不得超过10 lsb。

正负满标度误差

可以认为ADC的输入通道双极(正、负)输入范围,但指的是vbias(或refin)而不是agnd。adc的正满标度误差是产生正满标度码转换所需的实际输入电压与理想输入电压(vbias+vswing-1.5lsb)之间的差,用lsb表示。负满标度误差同样适用于负满标度代码转换,相对于此转换的理想输入电压(vbias–vswing+0.5 lsb)。注意,adc输入通道的满标度误差是在其各自的偏置偏移误差被调整后测量的。

正负满标度误差匹配

这是衡量所有通道的满标度误差相互跟踪的程度。无论信道是独立采样还是同时采样,任何信道的满标度误差匹配与任何其他信道的相应满标度误差的距离不得超过10 lsb。

短路电流

这被定义为最大电流,如果该引脚对0 V和VCC之间的任何电位短路,则该电流将流入或流出重新输出引脚。在不超过包的功耗的情况下,这种情况最多允许10秒。

信噪比和失真率,s/(n+d)信噪比和失真比s/(n+d)是测量输入信号的均方根值与奈奎斯特频率以下所有其他谱分量的均方根和的比值,包括谐波,但不包括直流电。s/(n+d)的值以分贝为单位。

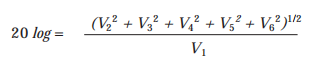

总谐波失真

总谐波失真是前五个谐波分量的均方根和满标度输入信号的均方根值之比,用分贝表示。对于AD7776/AD7777/AD7778,总谐波失真(THD)定义为:

其中,v 1是基波的均方根振幅,v 2、v3、v4、v5和v6是单个谐波的均方根振幅。

互调失真

当输入由两个频率fa和fb的正弦波组成时,任何具有非线性的有源器件将在mfa+nfb的和频和差频处产生阶数(m+n)的畸变产物,其中m,n=0,1,2,3。互调项是指m或n不等于零的互调项。例如,二阶项包括(fa+fb)和(fa-fb),三阶项包括(2fa+fb),(2fa-fb),(fa+2fb)和(fa-2fb)。

通道间隔离

信道间隔离度是测量信道间串扰水平的一种方法。它是通过对任何一个输入通道应用满标度100 kHz正弦波信号并监视其余通道来测量的。给出的数字是所有频道中最糟糕的情况。

数字信号处理应用

在数字信号处理(dsp)的语音识别、回波抵消和自适应滤波等应用领域,adc的动态特性s/(n+d)、thd和imd至关重要。AD7776/AD7777/AD7778是动态指定的,并且具有标准的直流规范。由于跟踪/保持放大器具有宽频带,因此应在模拟输入端放置抗混叠滤波器,以避免高频噪声混叠回到感兴趣的频带。

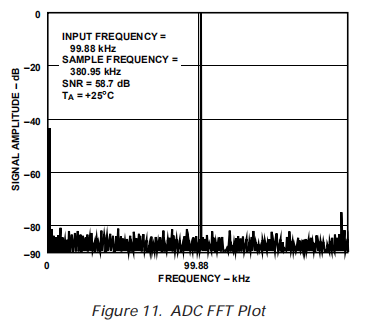

通过对以380.95khz采样率采样的单个模拟输入应用非常低失真的正弦波信号来评估adc的动态性能。然后生成一个快速傅立叶变换(fft)图或直方图,从中可以得到信号的噪声和失真、谐波失真和动态微分非线性数据。类似地,对于互调失真,将由两个不同频率的纯正弦波组成的输入信号施加到ad7776/ad7777/ad7778。

图11显示了输入信号为99.88 kHz的AD7778的单通道2048点FFT图。信噪比为58.71db。可见,大部分谐波都埋在噪声层中。应注意,在计算s/(n+d)时考虑了谐波。

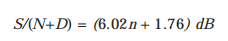

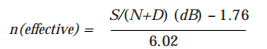

s/(n+d)与分辨率(n)之间的关系用以下公式表示:

这适用于没有微分或积分线性误差的理想零件。这些错误将导致s/(n+d)的退化。通过从上面的方程向后计算,可以得到以有效比特数(n)表示的adc性能的度量:

图12显示了AD7778单通道的有效比特数与频率的关系。有效比特数通常为9.5。

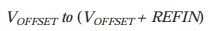

改变模拟输入电压范围通过在agnd上偏置rtn管脚,可以将模拟输入电压范围从vbias±vswing格式更改为更传统的0v到vref范围。新的输入范围可以描述为:

如果0 V≤Voffset≤1 V。要产生此范围,RTN管脚必须偏向(Refin–2 Voffset)。例如,如果RTN与REFOUT连接,然后模拟输入范围变为0 V至2 V。ADC的固定2 V模拟输入电压范围可从1 V至3 V(RTN=0 V)至0 V至2 V(RTN=2 V)不等,即,通过适当的偏置,可覆盖0.3 V至2.3 V的输入信号范围。在这种模式下,相对精度和微分非线性性能基本保持不变,而信噪比和thd性能通常比标准差2-3db。