说明

WM8501是一款具有集成1.7VRMS线路驱动器。它是为音频设计的需要高电压输出的应用增强的负载驱动能力。

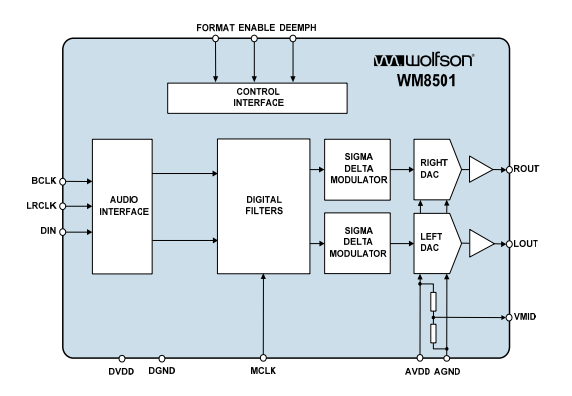

WM8501支持数据输入字长度从16到24位,采样率高达192kHz。WM8501包括串行接口端口、数字内插滤波器,14中的多位Sigma-Delta调制器和立体声DAC-铅SOIC封装。

硬件控制接口用于选择

音频数据接口格式,启用和取消强调。这个WM8501支持I2S,右对齐或DSP接口。在单独的模拟和数字电源上操作WM8501提供了非常低的功耗数字部分,同时支持增强的负载驱动模拟输出。

特征

带1.7Vrms线路驱动器的5V模拟立体声DAC

供给

音频性能

-100dB信噪比(‘A’加权@48kHz)——88db螺纹

DAC采样频率:8kHz–192kHz

插针可选音频数据接口格式-I2

S,16位右对齐或DSP14铅SOIC包

4.5 V-5.5 V模拟、2.7 V-5.5 V数字电源操作

应用

机顶盒

DVD

数字电视

设备描述

概述

WM8501是一种高性能的数模转换器,带有来自5V的集成1.7Vrms线路驱动器。

模拟电源,设计用于数字消费音频应用。

WM8501是一个完整的双声道立体声音频数模转换器,包括数字内插滤波器、带抖动的多位Sigma Delta和开关电容多位立体声DAC输出平滑滤波器。它完全兼容,是一系列行业的理想合作伙伴标准微处理器、控制器和DSP。设备内部功能的控制由硬件控制插脚(插脚编程)提供。

支持使用256fs、384fs、512fs或768fs主时钟的操作,可在时钟速率被自动控制。低于8kHz至96kHz的采样率(fs)为允许,前提是输入了适当的系统时钟。支持的频率也高达192kHz。使用128fs或192fs的主时钟。

音频数据接口支持16位右对齐或16-24位I2S(飞利浦左对齐,一位延迟)接口格式。还支持DSP接口,增强了用户。

可使用分体式模拟和数字2.7-5.5V电源,输出振幅绝对缩放模拟电源电平。低供电电压运行和低电流消耗结合低针数小包装使WM8501吸引许多消费者的应用。一提供断电模式,使功耗最小化。该设备封装在一个14针的小型SOIC中。

DAC电路说明

WM8501 DAC的设计允许播放24位PCM音频或类似的高数据。

分辨率高,噪音低,失真小。可使用高达192kHz的采样率,但要低得多。

如果采样率(LRCLK)与主时钟的比率为(MCLK)维持在要求的费率之一。

WM8501上的两个DAC是使用Sigma-Delta过采样转换实现的。

技术。这些要求对PCM样品进行数字过滤和内插以生成一组比高达192kHz的输入速率高得多的样本。此示例流是然后进行数字调制以产生数字脉冲流,然后将其转换为模拟脉冲流。

开关电容器DAC中的信号。

这种技术的优点是使用噪声整形技术对DAC进行线性化。

允许使用非关键模拟组件来满足24位分辨率。更进一步优点是,DAC输出的高采样率意味着DAC的输出只需要具有相当粗糙的特性,就可以去除这些特性。

DAC输出上的步骤或图像。防止产生不需要的音调抖动与高阶调制器一起用于数字调制器。

在数模转换器中使用的多位开关电容技术降低了时钟抖动的灵敏度,并且与开关电流或单比特技术相比,能显著降低带外噪声。

VMID引脚上的电压用作DAC的参考电压。因此,振幅DAC输出端的信号将随VMID引脚电压的振幅而缩放。安如果需要,外部引用可用于驱动到vmid pin,其值通常为关于中轨的最佳性能。

2个数模转换器的输出由能够驱动的缓冲放大器缓冲出装置。

低阻抗线路负载低至820,耳机负载低至16。缓冲器使用5伏模拟电压时,线路电平负载的放大器输出电压电平设置为1.7伏rms。

提供,避免在许多情况下需要额外的增益级或更高的电源应用。当驱动耳机加载时,输出电压水平限制为1Vrms。这个在WM8501中使用的高级多比特数模转换器产生的带外噪声远小于单比特数模转换器。

传统的sigma-delta-dacs,等等,在大多数需要行级输出的应用中,没有需要后DAC筛选器。通常是一个交流耦合电容器和一个直流整定电阻对地是芯片输出所需的唯一组件。

时钟方案

在典型的数字音频系统中,只有一个中央时钟源产生参考时钟。

所有音频数据处理都同步到。这个时钟通常被称为音频系统的主时钟。外部主时钟可通过MCLK输入直接应用。

没有采样率选择所需配置的针。

注意,在WM8501上,MCLK用于派生DAC路径的时钟。DAC路径由数模转换器采样时钟、数模转换器数字滤波器时钟和数模转换器数字音频接口定时组成。在一个如果参考时钟有许多可能的源,建议使用使用抖动最小的时钟源来优化DAC的性能。

通过停止MCLK,设备可以断电。在这种状态下,功耗为大幅减少。

数字音频接口

音频数据通过数字音频接口应用于内部DAC滤波器。三个接口支持格式:右对齐模式

DSP模式

所有格式都首先发送MSB。数据格式是通过格式pin选择的。格式化时如果低,则选择右对齐数据格式,并且可以使用16位的字长度。当格式PIN高选择S格式,任何值的字长最多可为24位使用。(如果使用的字长小于24位,则应使用零填充未使用的位)。

如果LRCLK为4个BCLK或更短的持续时间,则选择与DSP兼容的格式。模式A和模式B时钟格式受支持,由格式pin的状态选择。

“打包”模式(即每个LRCLK周期仅支持32或48个时钟)操作在两个I2中也都受支持。

(16-24位)和右对齐格式(16位)。如果应用16位字长的“压缩”格式(每个LRCLK半周期16个BCLK),设备自动检测此模式并切换到16位数据长度。

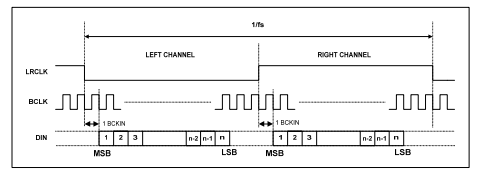

WM8501支持I2中16-24位的字长度

S模式,数字音频接口接收数据的输入。音频数据是时间与LRCLK多路复用,指示是否存在左信道或右信道。也使用了LRCLK作为表示数据字开始或结束的时间参考。

S模式,每个LRCLK周期的最小BCLK数是所选字的2倍

长度。lrclk必须是high(最小字长)bclks,low(最小字长)bclks。

长度bclks。如果满足上述要求,则可接受LRCLK上的任何标记空间比。

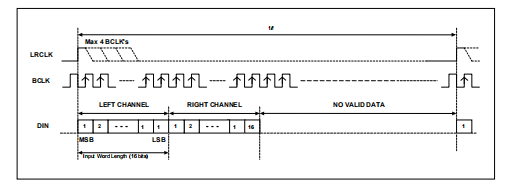

满足。在I2中在S模式下,在BCLK的第二个上升沿上,在LRCLK之后对MSB进行采样。

过渡。左采样时lrclk较低,右采样时lrclk较高。

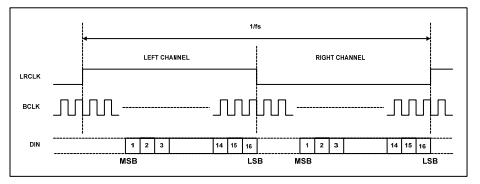

右对齐模式

WM8501支持在右对齐模式下16位的字长度。

在右对齐模式下,数字音频接口接收数据输入。音频数据是时间与LRCLK多路复用,指示是否存在左信道或右信道。也使用了LRCLK作为表示数据字开始或结束的时间参考。

在右对齐模式下,每个LRCLK周期的最小BCLK数是所选时间的2倍字长。lrclk必须至少为字长bclks为高,至少为低字长bclks。如果上述情况发生,则可接受LRCLK上的任何标记空间比。

满足要求。

在右对齐模式下,LSB在LRCLK之前的BCLK上升沿上采样。

过渡。左采样时lrclk高,右采样时lrclk低。

右对齐模式时序图

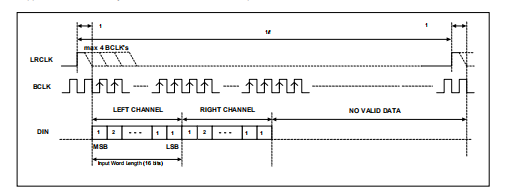

WM8501还支持与DSP兼容的时分复用格式。此格式是指“同步”脉冲后接两个预定数据字(左和右)的类型。

字长。(16位)。“同步”脉冲取代正常时长LRCLK,DSP模式为由较短的LRCLK正常持续时间自动检测。如果lrclk等于或小于4 bclk持续时间,选择与DSP兼容的格式。模式A和模式B时钟格式为支持,由格式pin的状态选择。

音频数据采样率

WM8501的主时钟支持从128fs到768fs的音频采样率,其中fs是音频采样频率(LRCLK),通常为32kHz、44.1kHz、48kHz、96kHz或192kHz。这个主时钟用于操作数字滤波器和噪声整形电路。

WM8501有一个主时钟检测电路,自动确定关系在主时钟频率和采样率之间(在+/-8主时钟范围内)。如果有的话是大于8个时钟的错误,接口关闭DAC并使输出静音。这个主时钟应与LRCLK同步,尽管WM8501允许相位时钟上的差异或抖动。

硬件控制模式

WM8501是硬件可编程的,为用户提供选择输入音频数据的选项。

格式化、去加重和静音。

启用操作

插脚4(启用)控制芯片的操作。如果启用为低,则设备保持在低电源状态。如果此插脚保持在高位,则设备通电。

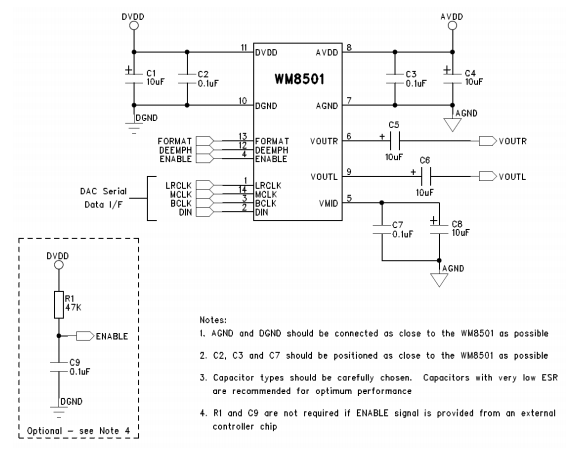

为确保正确操作,使能销上必须有从低到高的转换。在数字电源接通后。这可以通过提供来自外部控制器芯片或通过使能管脚上的简单RC网络。见“应用程序信息”部分的“推荐外部组件”在此结束

请注意,启用引脚不应用作静音引脚或暂时使DAC静音。

(例如,在CD的磁道之间)。使能引脚不能用作静音。

控制,但允许进入低功率模式。通过启用引脚禁用设备具有关闭电压对VMID管脚的影响。重复启用/禁用设备会在输出端发出砰的声音。

应用程序信息推荐的外部组件外部部件图

在使能直接从VDD而不是专用控制线供电的应用程序中,使能引脚上使用了电阻器R3和电容器C9,以在低至启用的高转换。这将确保电源有时间后插脚变高。结算(见数据表“硬件控制模式”部分的“启用操作”)。但是,如果从外部控制器芯片而不是VDD提供启用信号直接,不需要R3和C9。