DS1642点击型号即可查看芯片规格书

512点击型号即可查看芯片规格书

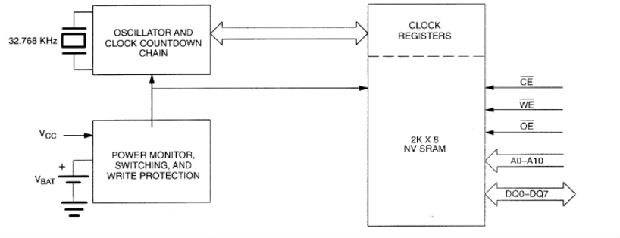

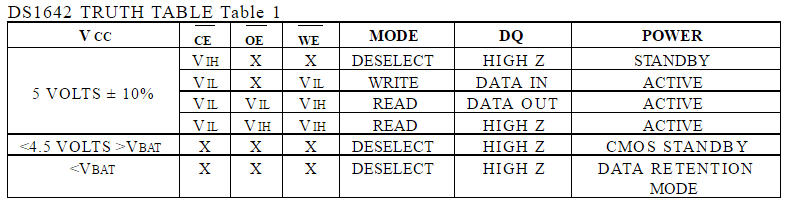

DS1642是2K×8非易失性静态RAM和一个全功能的实时时钟,这两者都是访问在一个单字节宽格式。非易失计时RAM是引脚和功能等同于所有JEDEC标准的2K ×8 SRAM 。该装置也可以很容易被取代的ROM,EPROM和EEPROM的插座,提供读/写非易失性和增加的实时时钟功能。该实时时钟的信息驻留在最高的8个RAM位置。 RTC寄存器包含年,月,日,星期,时,分,秒的数据在24小时BCD格式。更正为天月份和闰年自动进行。 RTC时钟寄存器是双缓冲来避免不正确的数据的访问时可能出现的时钟的更新周期。双缓冲系统也避免时间上的损失倒数计时有增无减通过访问时间寄存器的数据。该DS1642还包含电源失效电路,取消选择设备时的VCC供应中超差的情况。此功能可以防止数据丢失的不可预测的系统操作低V带来的CC为避免错误的访问和更新周期。

时钟操作

读取软时钟而双缓冲寄存器结构减少了读取不正确的数据,内部更新的机会到DS1642时钟寄存器应时钟数据之前被停止读出,以防止数据的读出中过渡。然而,停止内部时钟的寄存器的更新过程中不影响时钟精度。当1被写入到读出的比特,在控制寄存器中的第七最显著位的更新被中止。只要1保持在该位置时,更新被中止。发出停止后,寄存器反映算,也就是一天,日期和时间,这是目前在发出halt命令的那一刻。不过,双缓冲系统的内部时钟寄存器继续更新,以使时钟精确度是不受数据的访问。所有的DS1642寄存器的时钟后同步更新状态复位。更新是在一秒钟内后读取位写入0。

设置时钟

控制寄存器的第8位是写入位。设定的写入位为1时,象读位,停止更新到DS1642寄存器。然后,用户可以在正确的星期,日期和时间数据加载它们24小时BCD格式。复位写入位到0,然后这些值传送到实际时钟计数器并允许恢复正常操作。

停止和启动时钟振荡器

时钟振荡器可以随时停止。以增加保质期,该振荡器可以被关闭以最小化从电池的漏电流。该OSC比特是MSB为秒寄存器。将其设置为1振荡器停振。

频率测试位

比特当天字节6为频率测试位。当频率测试位被置为逻辑1,并且振荡器运行,对LSB秒寄存器将切换为512赫兹。当秒注册为被读出后, DQ0线将在512 Hz的频率进行切换,只要获取条件仍然有效(即CE低,并OE低点)和地址秒钟注册仍然有效,稳定。

时钟精度

DS1642是保证计时精确度内±1每个月分钟,在25℃的时钟C.校准时使用特殊的校准非易失性调谐元件由Dallas Semiconductor的工厂。在DS1642不需要额外的校正和温度偏差将有一个可忽略不计在大多数应用中实现。出于这个原因,场时钟校准方法不可用并且不有必要的。