74LS244点击型号即可查看芯片规格书

74LS244为3态8位缓冲器,一般用作总线驱动器。74LS244没有锁存的功能。地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数据和地址总线采用分时复用操作方法,即用同一总线既传输数据又传输地址。

当微处理器与存储器交换信号时,首先由CPU发出存储器地址,同时发出允许锁存信号ALE给锁存器,当锁存器接到该信号后将地址/数据总线上的地址锁存在总线上,随后才能传输数据。

锁存器是一个很普通的时序电路。一般的,它在时钟上升沿或者下降沿来的时候锁存输入,然后产生输出,在其他的时候输出都不跟随输入变化,这就是所谓边缘触发的D触发器。

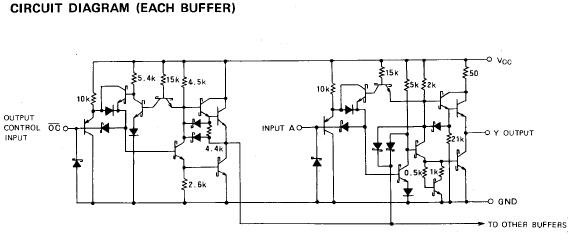

内部功能原理图:

74LS244由2组、每组四路输入、输出构成。每组有一个控制端G,由控制端的高或低电平决定该组数据被接通还是断开。

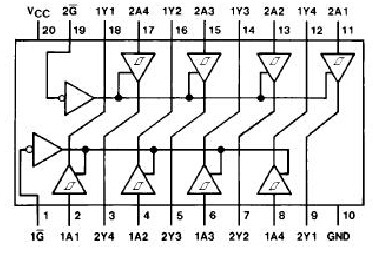

引出端符号:

1A1~1A4,2A1~2A4输入端

/1G,/2G三态允许端(低电平有效)

1Y1~1Y4,2Y1~2Y4输出端

74LS244引脚图:

极限值:

电源电压:7V

输入电压:5.5V

输出高阻态时高电平电压:5.5V

工作环境温度

54XXX:-55~125℃

74XXX:0~70℃

存储温度:-65~150℃

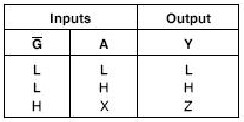

74LS244功能表:

它主要用于三态输出,作为地址驱动器、时钟驱动器、总线驱动器和定向发送器等。其真值表如下:

L表示低电平

H表示高电平

X表示不定状态

Z表示高阻态

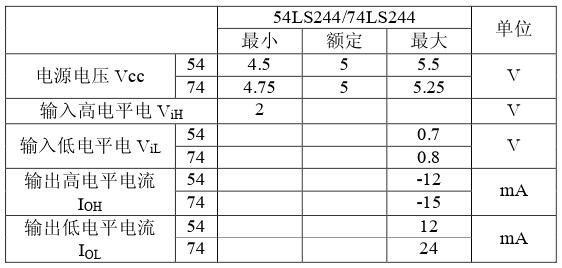

74LS244推荐工作条件:

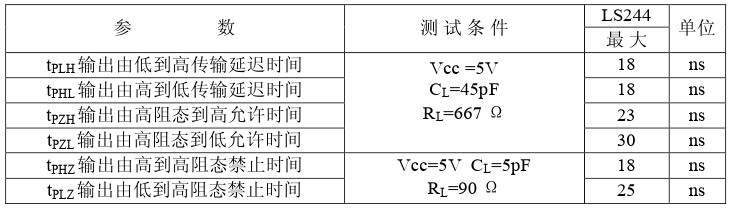

动态特性(TA=25℃):

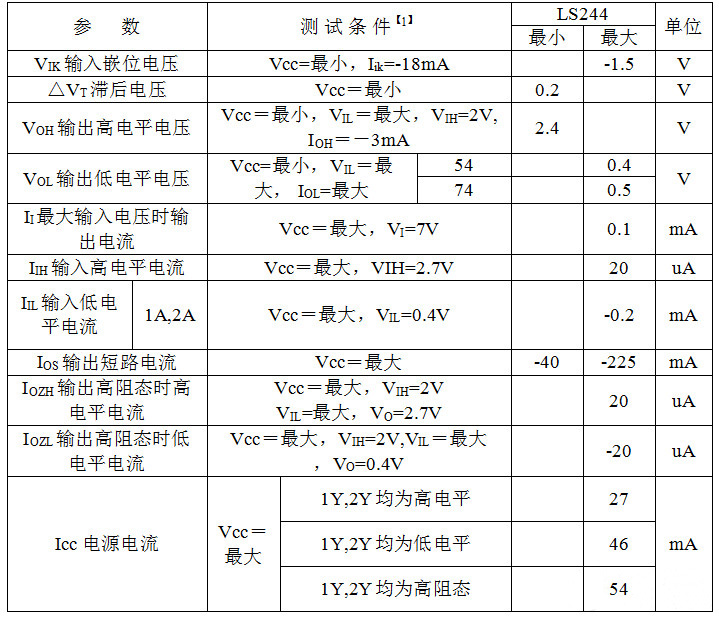

静态特性(TA为工作环境温度范围):

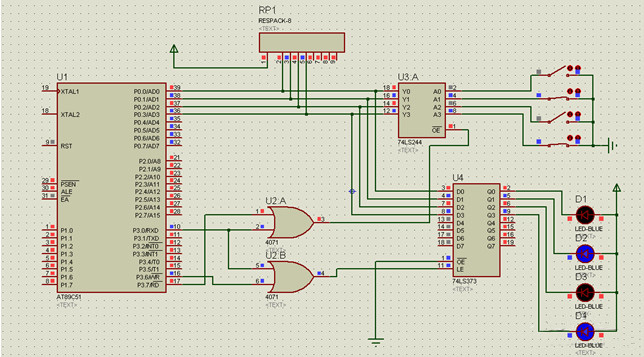

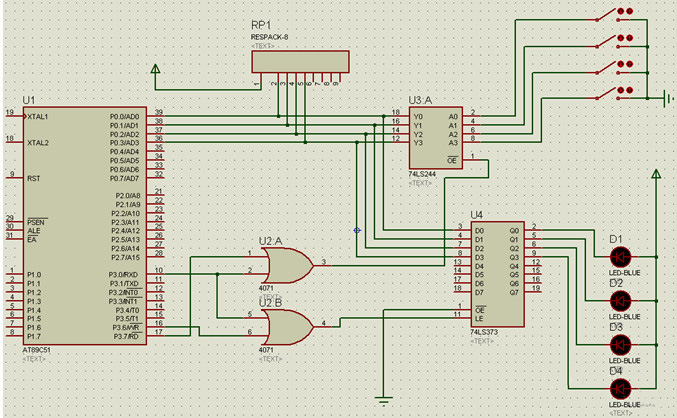

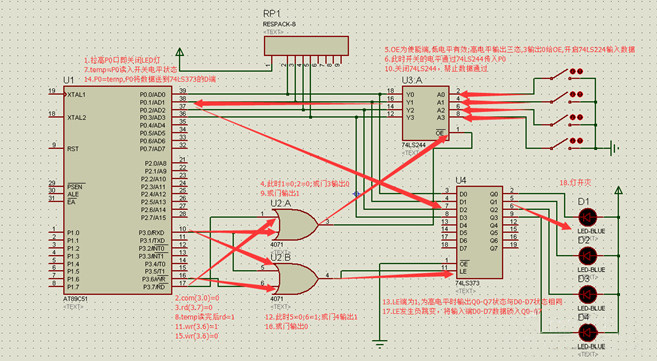

74LS244应用电路:

用4个开关控制4个LED的亮灭状态,其中采用74LS244控制开关的输入,采用74LS373控制LED输出。

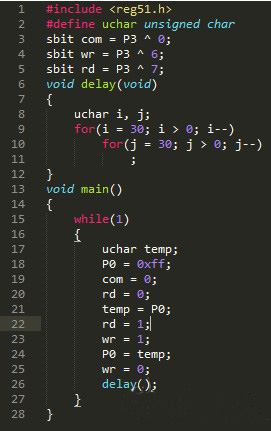

代码:

电路图:

过程分析:

过程:

#18 P0=0xff; 通过拉高P0口置为1111 1111,即关闭LED灯;

#19 com=0; 对CD4071 U2.A的1和CD4071 U2.B的5输入一个0;

#20 rd = 0; 对CD4071 U2.A的2输入一个0;

由于CD4071的功能是执行逻辑或运算,1和2分别输入0,则3输出0给74LS244的OE口;

74LS244缓冲驱动器的OE为使能端,低电平是有效的,高电平时输出为三态,此时通过CD4071传给OE低电平,使开关的电平可以通过74LS244传入P0;

开关状态传入P0;

#21 temp = P0; 通过定义的unsigned char temp来存放P0的状态

#22 rd = 1; 对CD4071 U2.A的2输入一个1;

1=0;2=1;此时或门输出为1;

74LS244的OE端高电平时输出为三态,关闭74LS244

#23 wr = 1;对CD4071 U2.B的6输入一个1;

此时5=0;6=1;CD4071 U2.B的7输出一个1;

74LS343的OE为低电平时,用作地址锁存器;LE为高电平时,输出Q0-Q7状态与D0-D7状态相同;当LE发生负跳变(1-》0)时,输入端的D0-D7锁入Q0-Q7

#24 P0 = temp; temp中的数据存入P0,传送到74LS343的D端;

#25 wr = 0; 对CD4071 U2.B的6输入一个0;

此时5=0;6=0;CD4071 U2.B的7输出一个0;

LE的状态从1-》0,发生负跳变,输出Q0-Q7

LED等接受到开关的情况,发生亮灭。

实验结果